進入後摩爾定律時代後 異質整合藍圖接棒

簡易重點為 : 建立全球產業共通語言,加速半導體產業實現異質整合的優勢,發展更高效能、更低延遲、更小尺寸、更低功耗與更低成本的技術與產品。

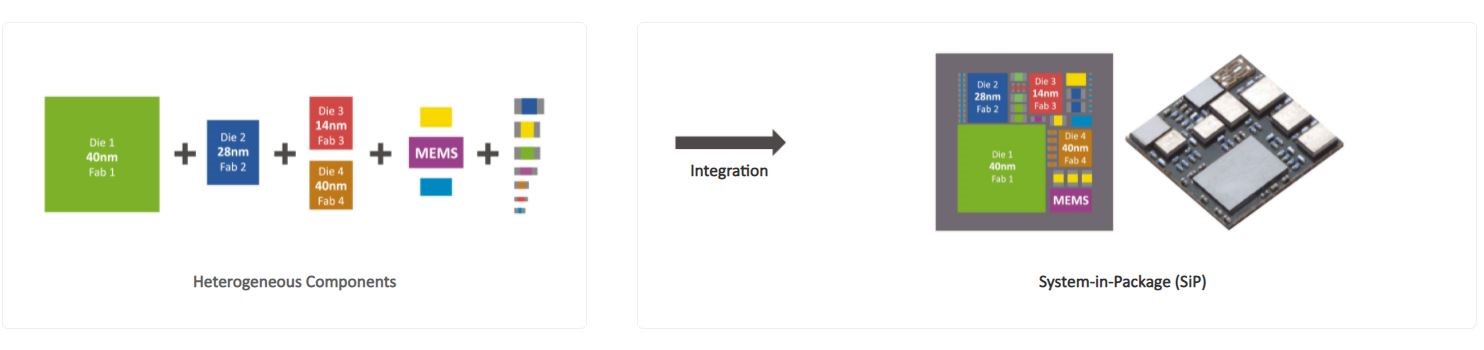

由於半導體摩爾定律限制,使得線寬不斷微縮、電晶體密度快速增加及升高,人們從早期的個人計算機發展並搭配QFP(Quad Flat Package)導線架傳統封裝方法,演進至現今5G通訊及IoT應用的SiP(System in Package)系統級先進封裝技術。

摩爾定律貢獻於終端產品演進,發現它不只帶動半導體製程的不斷精進,也引領封裝技術的逐步提升,遂逐步將終端應用推向智慧化,而5G及IoT應用正開啟人類生活的新視野。日月光集團特別在5G通訊應用上,將藍牙晶片及MCU(微控制器)藉由SiP封裝技術整合為一。 (此圖轉載於 日月光官網 異質整合公開資訊)

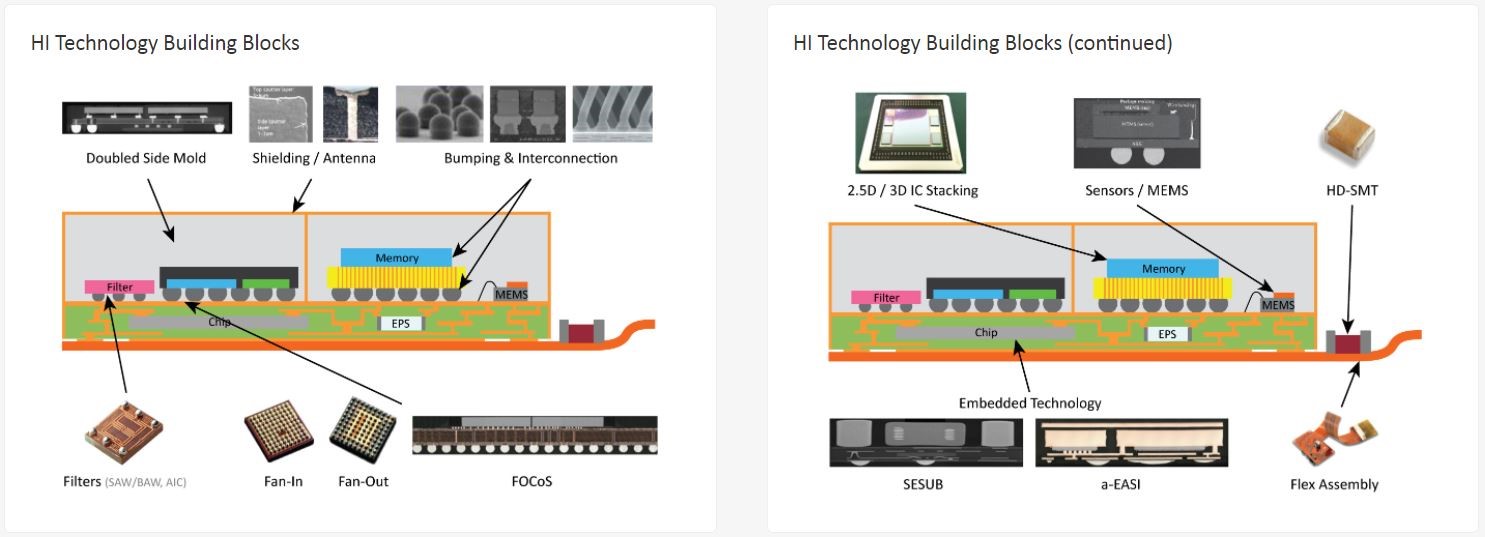

(此圖轉載於 日月光官網 異質整合公開資訊)

異質整合能力決定 未來封測技術發展指標

針對異質整合的發展特性,將有以下幾個評估要點:考量整體的機械性質、元件結構間的熱能變化,以及適當材料及程序操作,還有晶片彼此間的互通有無等。

日月光是目前台廠中,具備系統級封裝技術層次最廣的封裝廠,涵蓋FCBGA、FOCoS和2.5D封裝等近十種封裝技術,將不同製程的晶片進行異構整合成單晶體,且具備模組構裝的設計能力, 讓晶片設計人員可以簡化設計, 縮短產品上市時間。眾多晶片商和系統廠採用日月光提供系統級封裝〈SiP)的平台,開發用於手機、網通、車載、醫療、穿戴式裝置和家電等多種產品應用。

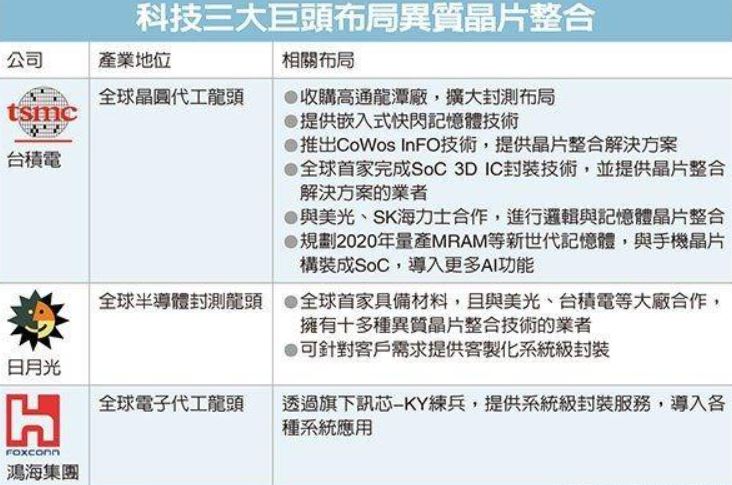

(此圖轉載於 經濟日報 公開資訊)

異質整合優點 已成各家趨勢

不意外的,未來更能將不同功能性及不同製程的產品,可直接在whole wafer型態時,即可整合成完成除了減少體積提升效能之外,更能降低傳統封裝製程各項複雜的process及轉廠運送時間成本(例 : SMT及wire bonding)有效掌握一條龍生產鏈,且提高UPH的好方式。半導體產業過去數十年來,以摩爾定律作為降低成本與功耗,並提升電晶體效能的發展主軸。

摩爾定律是指積體電路上可容納的電晶體數目,每18個月便會增加一倍。隨著製程愈來愈精密,摩爾定律推進時間面臨延長問題,業界透過封裝、材料和軟體等方式,進行異質整合,藉此延伸晶片性價比,並擴大應用。封測技術更扮演成敗關鍵,從台積電、日月光、鴻海等科技大廠都積極投入來看,凸顯異質整合已是大勢所趨。

(此圖轉載於 日月光官網 異質整合公開資訊)

台廠加快異構整合布局 甩開全球對手

業界認為,異構整合將是台灣拉開與全球競爭差距,藉由差異化,搶先進應用晶片商機的利器。工研院產業科技國際發展策略所研究總監楊瑞臨預期,未來十年,異構晶片整合將為先進封裝廠帶來龐大機會。不過,還是要透過材料及封測技術突破,才能將市場商機擴大。

這些異構整合的趨勢,主要建立在穿戴裝置、智慧型手機、5G、AI、網通設備對微型化的系統級封裝(SiP)需求持續揚升。尤其未來手機及穿戴產品須將連網的關鍵元件,例如Sub 6GHz與毫米波(mmWave)、射頻前段模組(RF-FEM)進行異構整合;應用在資料中心晶片則須將高速運算的繪圖晶片(GPU)和網通晶片整合,甚至朝向多晶片/多模組封裝。