本篇幅主要為大家介紹氮化鎵 (GaN) 和碳化矽 (SiC) 等寬帶隙半導體器件用作電子開關的優勢,以及如何權衡利弊。主要權衡因素之一是開關損耗,開關損耗會被高 di/dt 和 dv/dt 放大,造成電路噪聲。為了減少電路噪聲,需要認真考慮柵極電阻的選擇,從而不必延長死區時間而造成功率損耗。本文介紹選擇柵極電阻時的考慮因素,如脈衝功率、脈衝時間和溫度、穩定性、寄生電感等。同時,將和大家探討不同類型的柵極電阻及其在該應用中的優缺點。

一、寬帶隙半導體器件的優勢

設計出色功效的電子應用時,需要考慮使用新型高性能氮化鎵 (GaN) 和碳化矽 (SiC) 技術的器件。與電子開關使用的傳統矽解決方案相比,這些新型寬帶隙技術具有祼片外形尺寸小、導熱和熱管理性能優異、開關損耗低等顯著優勢,非常適合工業、醫療、通信和車載應用電源、驅動器和逆變器等空間受限的應用。

不過,設計需要考慮一些利弊關係,特別是開關損耗。例如,di/dt 和 dv/dt 提高,開關速度加快,電路頻率振盪放大,使噪聲成為重要考慮因素。

二、電路設計中的考量因素

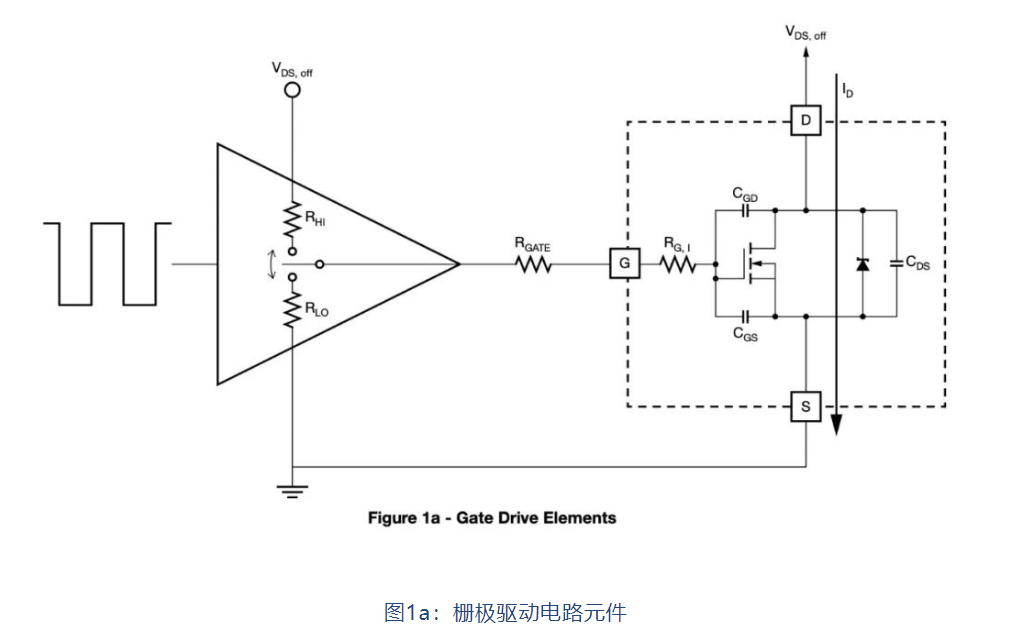

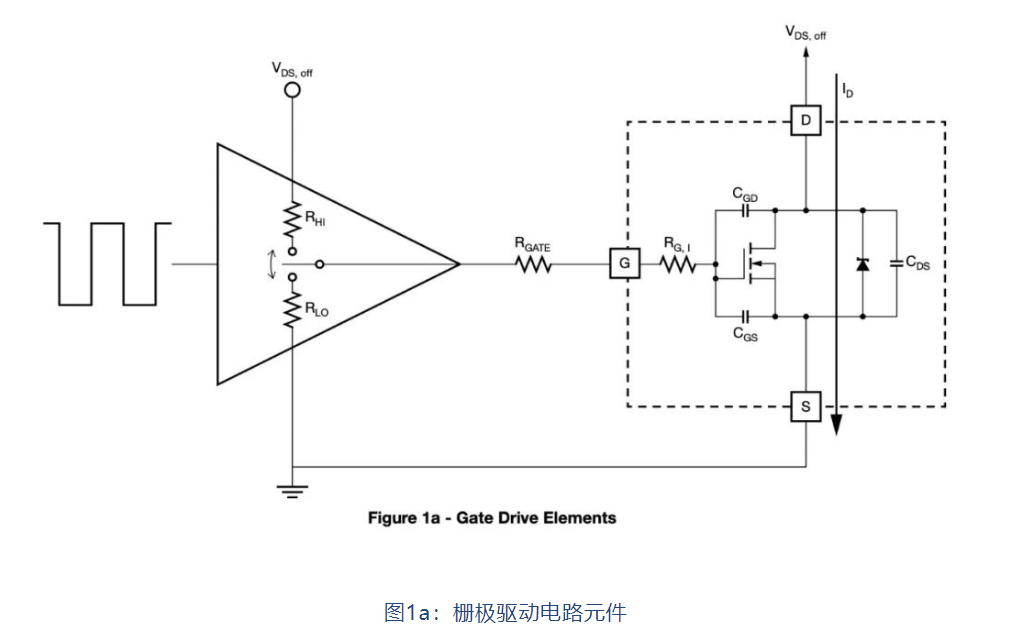

典型電路功能中,高邊 (HS) 和低邊 (LS) MOSFET 用作開關器件驅動電感負載。在 HS 開關導通,LS 開關關斷時,電流從電源 Vcc 流向電感器 Lo。反之,在 HS 開關關斷,LS 開關導通時,電感器電流繼續從接地端同步流向 Lo。導通/關斷狀態由柵極電壓定義,柵極電壓的變化影響柵極迴路的充放電。開關時間和相關損耗取決於柵極電容通過柵極電流充放電的速度。柵極電流受驅動電壓柵極電阻和驅動電路整體寄生效應的影響(圖1a)。

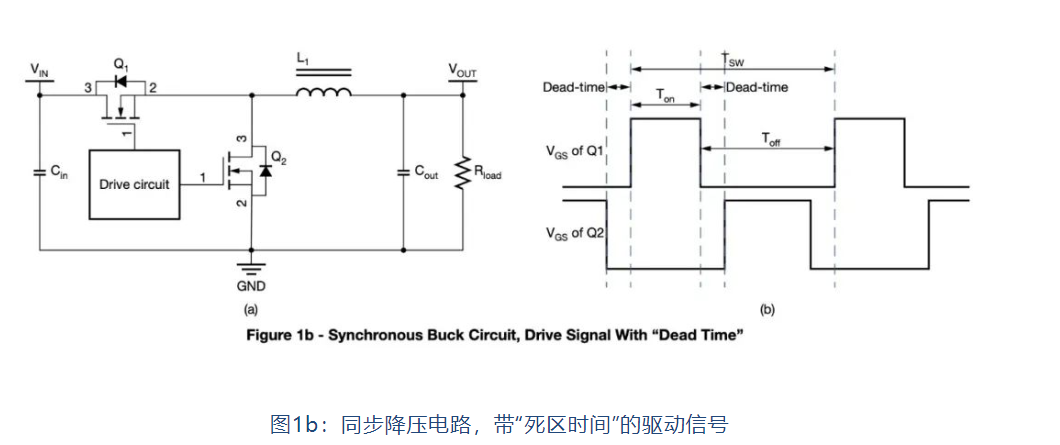

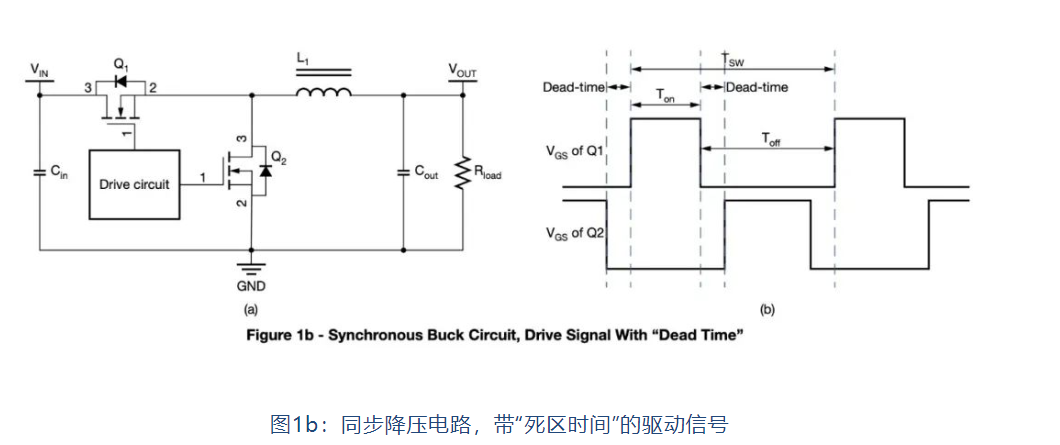

為了避免同時導通/關斷,需要認真選擇柵極電阻解決方案,如高功率厚膜片式電阻、薄膜 MELF 或高功率背接觸電阻。這類解決方案不需要延長有效轉化為功率損耗的“死區時間”(HS 和 LS 開關導通之間的時間間隔)(圖1b)。

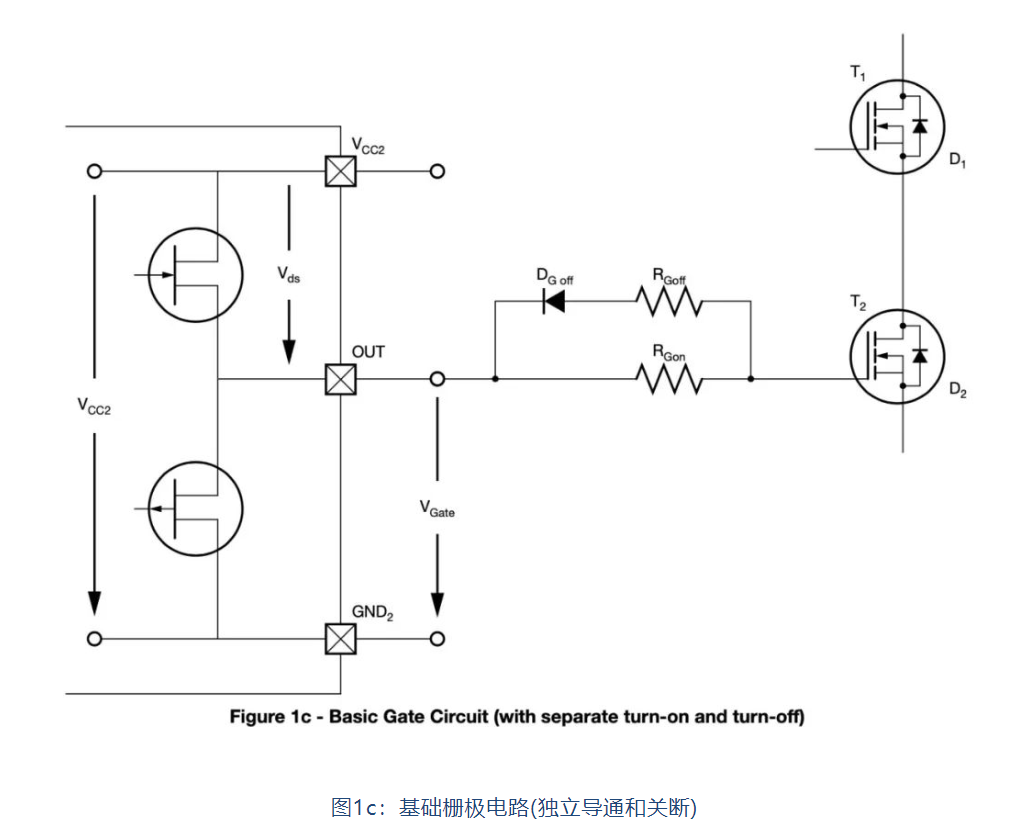

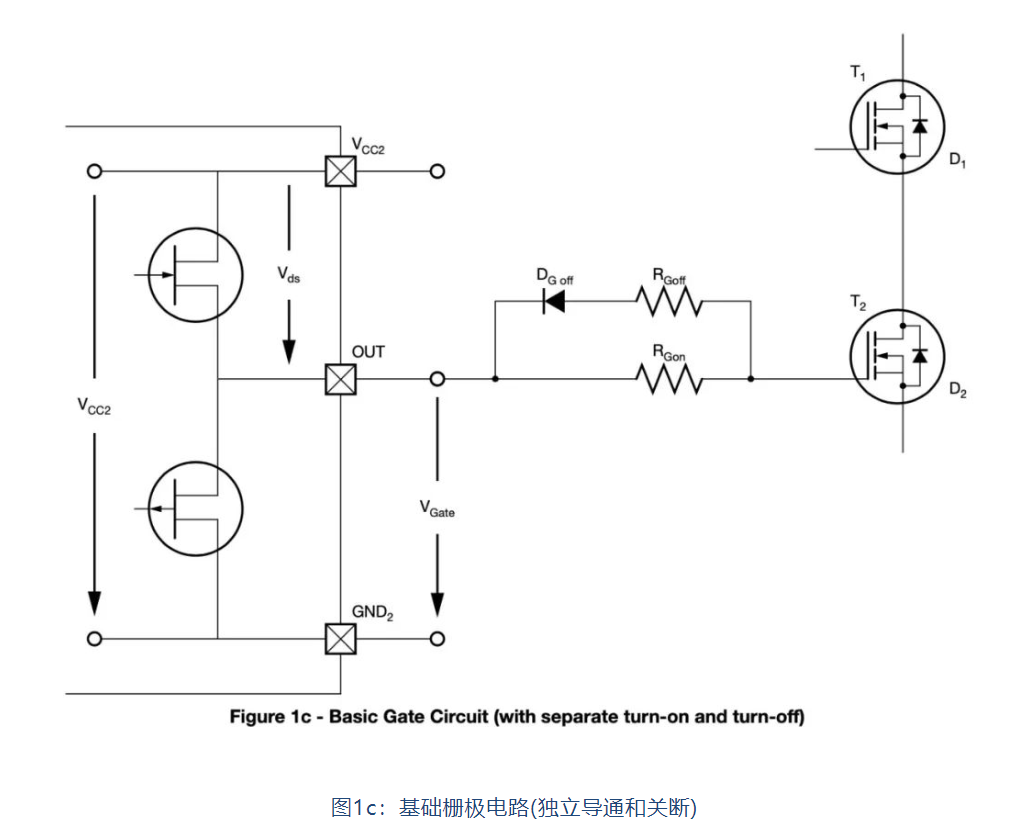

選擇柵極電阻技術的基本考慮因素主要包括脈衝功率、脈衝時間和溫度以及穩定性。使用兩個柵極電阻時,通常建議導通柵極電阻值至少是關斷柵極電阻值的兩倍(圖1c)。重要的是注意關斷柵極電阻值,避免漏極(或 IGBT 情況下,集電極)電壓上升發生寄生導通。

同時,還要考慮柵極電阻的阻值,阻值過高或過低都會發生損耗或振盪。柵極電阻要求能夠承受短時間高峰負載,平均功耗隨頻率和占空比而增加。在功能上,電阻能夠對器件內部寄生電容放電並進行 Miller 充電。減小電壓過沖可以降低器件和驅動器的應力,減小寄生電感可以避免開關過程產生 VGS 振盪。

為了儘量減少電路中的噪聲,縮短布線長度(減小寄生電感)很重要。因此,通常首選打線或表面貼裝柵極電阻。採用 IGBR 打線電阻的情況下,背接觸具有優異導熱性,並最大限度減小器件與 PCB 之間的熱梯度。在連接、外形尺寸和燒結能力方面,IGBR 電阻在打線連接,小尺寸以及燒結能力方面的綜合性能可以讓其更靈活地內置於高功率半導體模塊或封裝。這樣電阻可以在布局上非常接近開關器件,從而減少部分寄生元件,有助於降低電路噪聲。

一、寬帶隙半導體器件的優勢

二、電路設計中的考量因素

典型電路功能中,高邊 (HS) 和低邊 (LS) MOSFET 用作開關器件驅動電感負載。在 HS 開關導通,LS 開關關斷時,電流從電源 Vcc 流向電感器 Lo。反之,在 HS 開關關斷,LS 開關導通時,電感器電流繼續從接地端同步流向 Lo。導通/關斷狀態由柵極電壓定義,柵極電壓的變化影響柵極迴路的充放電。開關時間和相關損耗取決於柵極電容通過柵極電流充放電的速度。柵極電流受驅動電壓柵極電阻和驅動電路整體寄生效應的影響(圖1a)。

為了避免同時導通/關斷,需要認真選擇柵極電阻解決方案,如高功率厚膜片式電阻、薄膜 MELF 或高功率背接觸電阻。這類解決方案不需要延長有效轉化為功率損耗的“死區時間”(HS 和 LS 開關導通之間的時間間隔)(圖1b)。

選擇柵極電阻技術的基本考慮因素主要包括脈衝功率、脈衝時間和溫度以及穩定性。使用兩個柵極電阻時,通常建議導通柵極電阻值至少是關斷柵極電阻值的兩倍(圖1c)。重要的是注意關斷柵極電阻值,避免漏極(或 IGBT 情況下,集電極)電壓上升發生寄生導通。

三、柵極電阻的選型建議

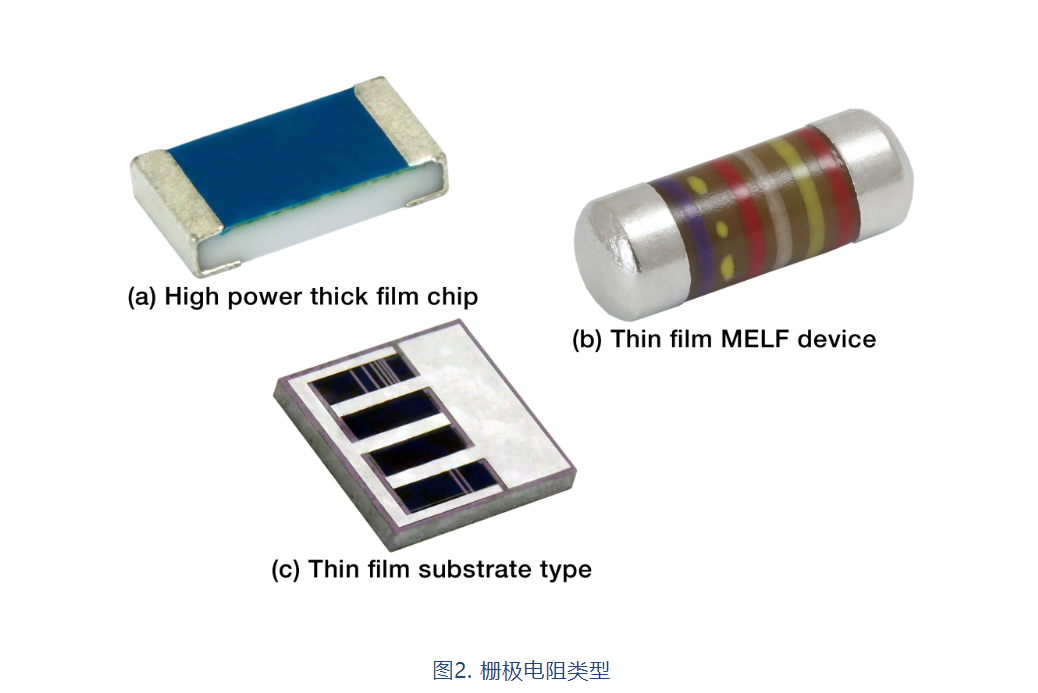

柵極電阻涵蓋多種技術解決方案,包括高功率厚膜片式電阻 (a)、薄膜 MELF 電阻 (b) 和額定功率達 4 W 的薄膜襯底電阻 (c)。柵極電阻選型的其他考慮因素包括元件尺寸、精度、可靠性、元件與 PCB 之間的熱性能以及並聯寄生電感。

評論