DC/DC Phase node量測是一般的電源量測中是一個常見的基本測項,以下為量測實列及改善方法

buck controller demo board 的condition 如下:

Vin=12, Vout=3.3, Fsw=250kHz

Low side MOSFET VDS=25V, 一般而言VDS的測試spec會抓VDS電壓的80%=>20V

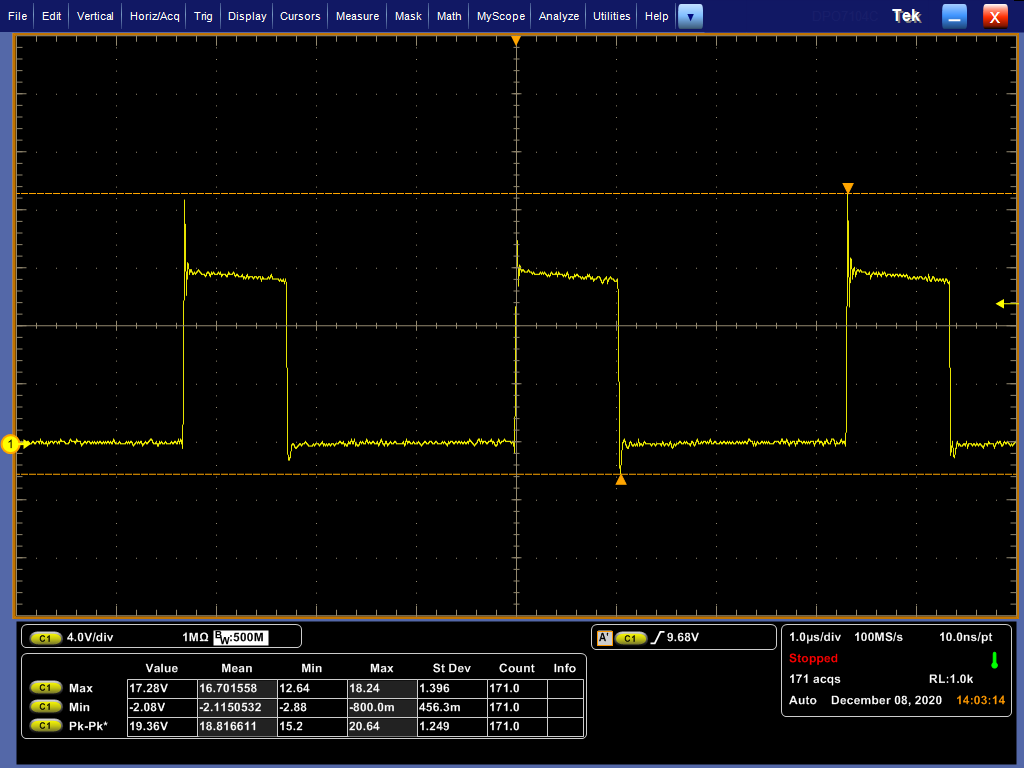

下圖使用最短路徑,bandwidth=500MHz,Max值=18.24V, 可meet spec

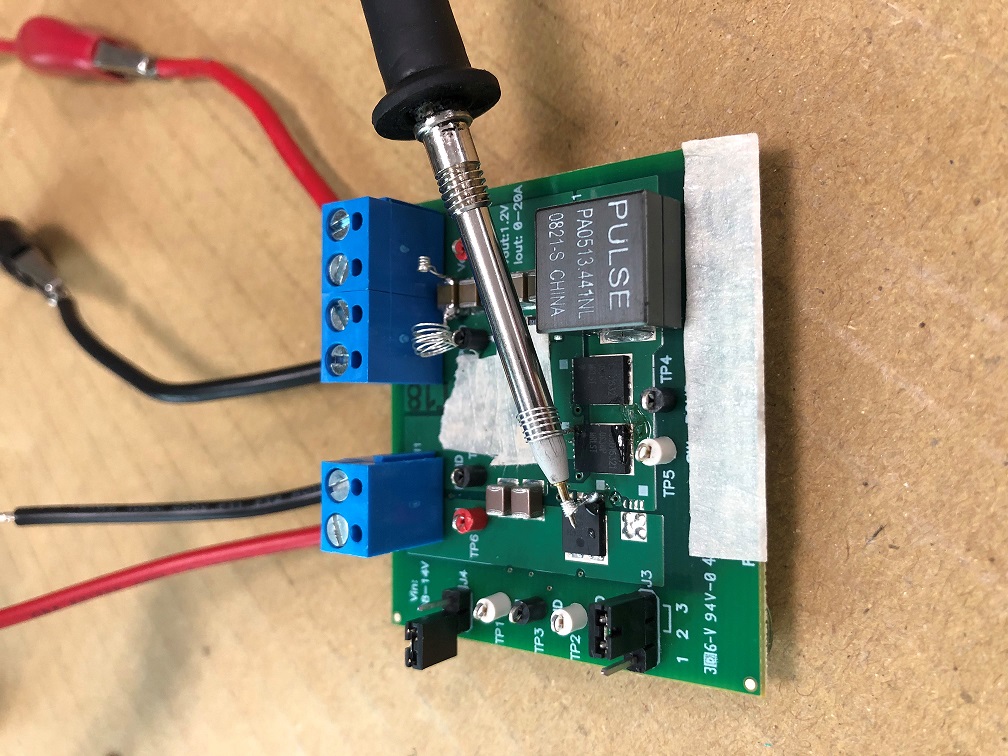

最短路徑

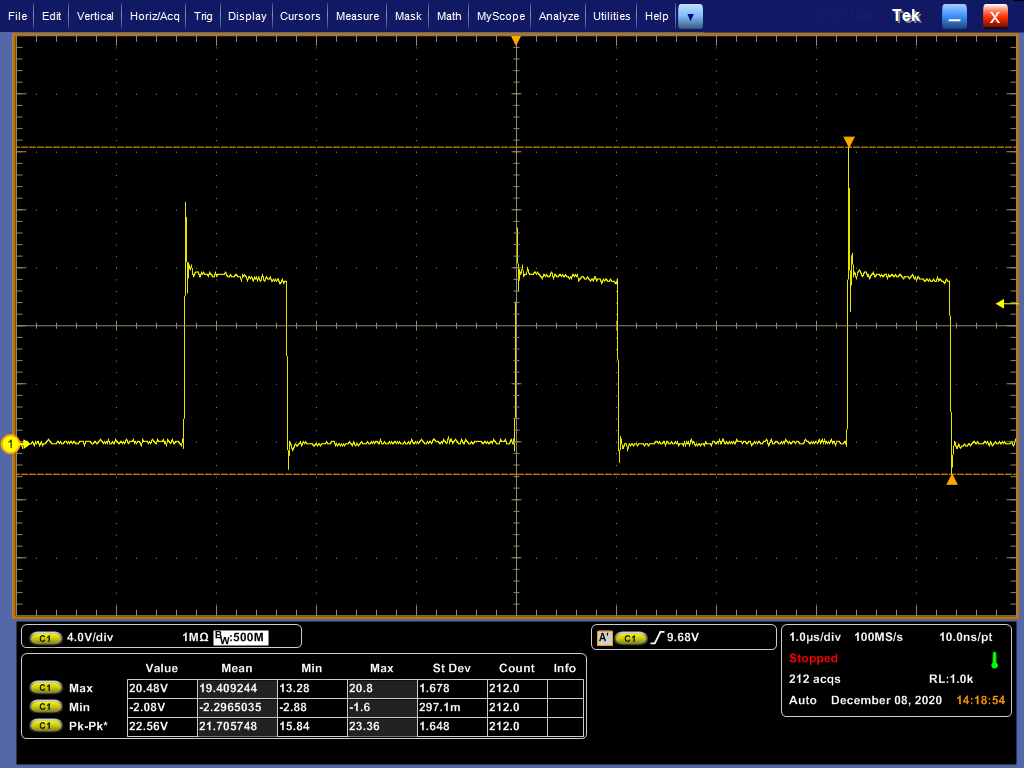

如果沒有使用最短路徑則可能得到下圖,結果=>20.8V over spec

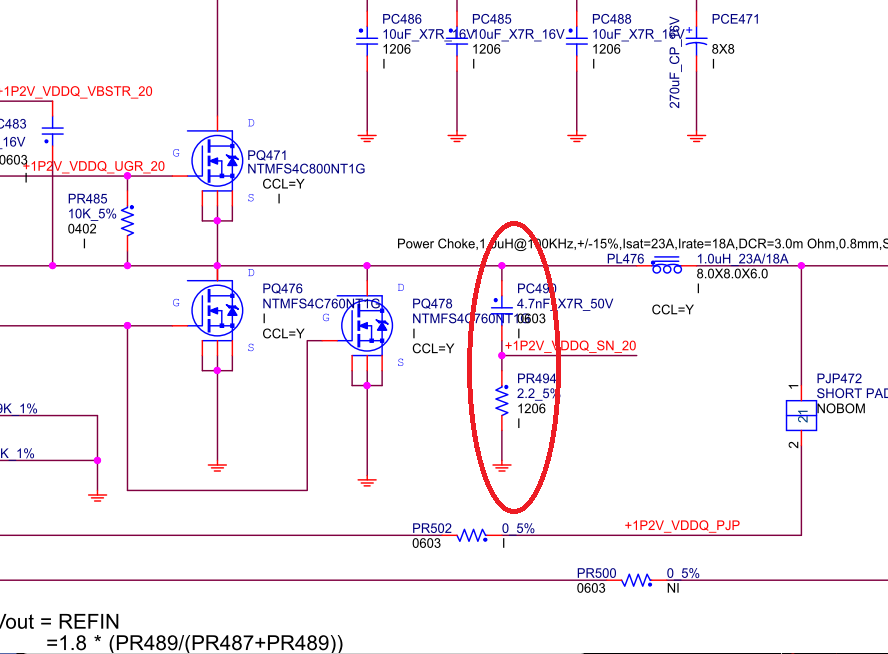

如果在使用最短路徑量測但結果還是會over spec的話,可能的原因如下:

- 量測位置點不好

- Layout placement

- MOSFET本身參數影響(Qg)

而最快的處理對策就是加snubber或R boost,但不能下得太重,因為會對效率有影響

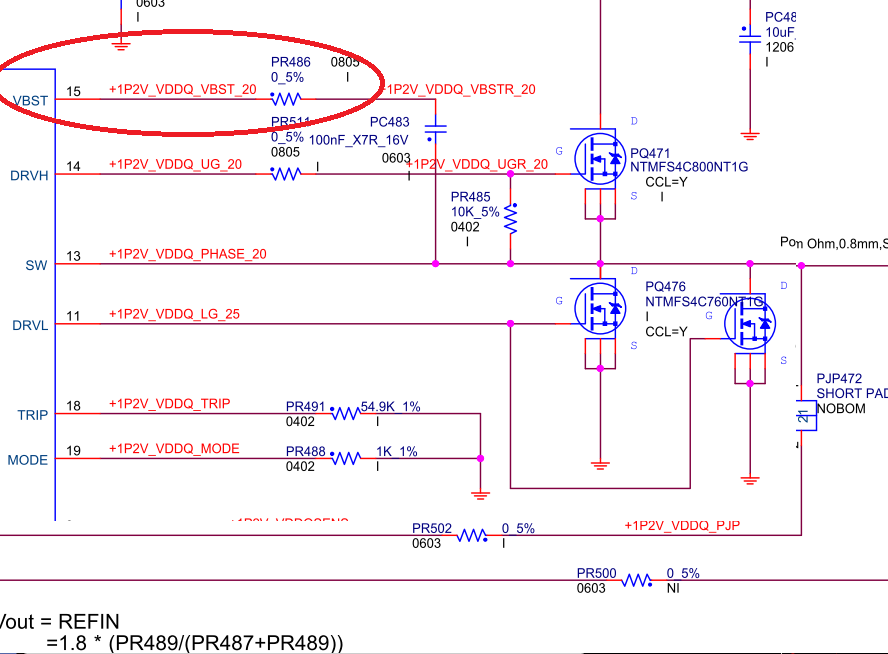

Snubber電路

R boost位置

如果使用snubber和R boost的改善效果都不大的話,就只能建議改善MOSFET的layout 或MOSFET

評論