本文主題是介紹如何以 NXP 的 DSC 實現 Peak Current Control Mode PSFB 功能的系列文章。文章分為三篇,本篇會先介紹 DSC 是使用那些功能來實現全橋 PWM,續篇會解說 PSFB 的動作機制。第三篇則是同步整流 PWM 的實現方式,以及透過內部機制偵測當前的 PWM 切換狀態。

相位移全橋 (Phase shift full bridge,簡稱 PSFB) 是經常使用在大功率電源上的電源架構,使用兩個 Duty 固定在 50% 的半橋開關組成全橋轉換器架構,利用兩個半橋間開關的相位差導通變壓器初級側,將能量轉換到次級側。由於相位差產生的開關導通時間順序,正好可以用來使開關上的電壓在導通前降至 0V,從而實現零電壓切換 (ZVS) 切換來提高效率。

PSFB 在一個週期內會有兩個導通的時段,分別對變壓器的磁化電感充磁與洩磁。在傳統的電壓控制型 PSFB 電路上,是以輸出電壓的補償器來決定目前輸出的 Duty,兩個導通時段在設計上是相同的。但是還是會因為以下的原因導致電感的充磁與洩磁的能量不同。

-

PFC 的輸出電容上存在的 120Hz 漣波電壓

-

每顆開關的 Rds(on) 不同導致兩個區間上的電感電流不同

-

實際上開關訊號有可能因為電路延遲或 IC 的缺陷導致時間不同

-

開關晶體的 Coss 不同導致實際開關導通的時間不同

磁化電感的充磁與洩磁的能量不同,則變壓器會產生磁偏,磁化電感無法工作在固定的磁化曲線上,會漸漸地朝某一邊偏,最後導致電感飽和。飽和則會導致電感呈現短路狀態,開關晶體則會因為短路的大電流損壞。因此必須要增加增加平衡電路,使磁偏可以被平衡回來。

但是平衡電路會造成多餘的成本與損耗,因此後來便提出了峰值電流控制模式 (Peak current control mode) 的方式,控制的對象由相位移的角度變成變壓器兩個區間的峰值電流,而輸出電壓的補償器則是控制變壓器電流的大小。如此一來便解決了磁偏的問題,但是讓開關以峰值電流控制的開關方式切換需要複雜的功能來實現。

傳統的 PSFB 的電路基本和和傳統的全橋轉換器相同,但是能量傳輸的方式較為特殊。是使用帶有 Deadtime 的 50% Duty PWM 分別控制兩組半橋開關,當兩個半橋開關的相位差大於零,使對角的開關 PWM 交疊時,變壓器就可以從輸入電壓獲得能量來進行轉換。由於控制的對象是相位差,因此可以將其中一組半橋視為固定臂,另一組開關動作上相位落後的則視為相移臂。

而 Peak Current Control Mode PSFB 在電路上則多了一個變壓器電流偵測的比流器,而在 PWM 上,因為採取控制變壓器磁化電流的方式,因此 PWM 不再是固定的 50% Duty,而是以電流峰值來決定開關的運作。實際運作上,與傳統 PSFB 相同,一樣存在一個固定臂,而另一組相移臂則在電流上升頂到目標時進行開關狀態的切換。

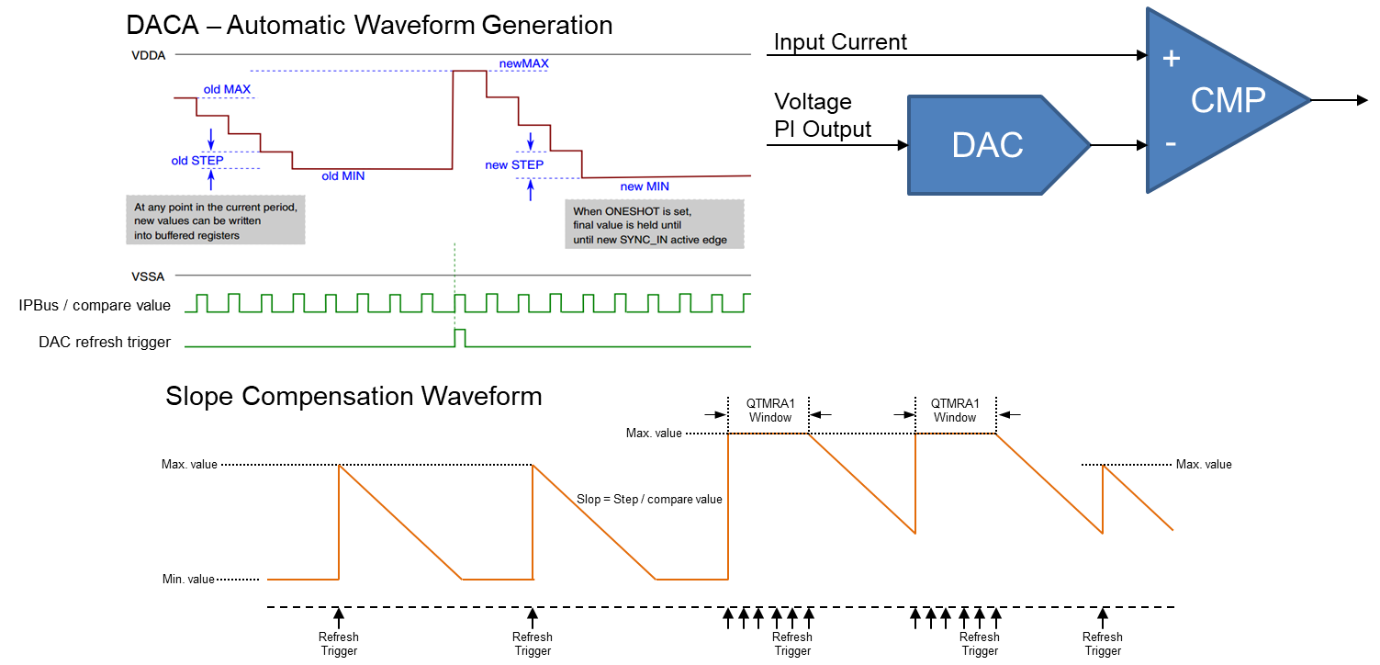

在電源上採用峰值電流控制方式時,在能量傳輸區大於週期 50% 時會開始因次諧波震盪的問題而有控制不易穩定的情況發生。原因與理論推導就不加詳述,結論上來說,一般採用峰值電流控制時,都會需要導入負斜率補償到電流峰值的參考訊號中來解決這個問題。

當使用 MCU 實現 PSFB 波形時,由於峰值電流控制相移,而電流變化的速度又遠高於一般 MCU 的 ADC 採樣與控制環路的計算速度,因此電流控制的相移臂動作會需要以硬體方式實現。以下先歸納一下要實現 PSFB 全橋開關控制的 PWM 所需要的功能。

-

全橋的固定臂要可以設定固定的 PWM 頻率,並在需要時可以改變頻率 ( 用作產生 Jitter 降低 EMI 噪聲 )。

-

四個 PWM 都需要有 Deadtime,Deadtime 需要可以調整以優化效率。

-

變壓器順向與逆向電流的電流峰值必須相同,避免造成磁偏。因此相移臂應該在每次峰值電流頂到相同高度時切換相移臂的開關的狀態。

-

電流的參考訊號需要帶有負斜率。

-

相移臂需要具備不傳輸能量的狀態 ( 相移角 0 度或是關閉 PWM 輸出 )。

-

可以限制最大的相移角度低於 180 度或是更低,以避免變壓器初次側兩端短路。

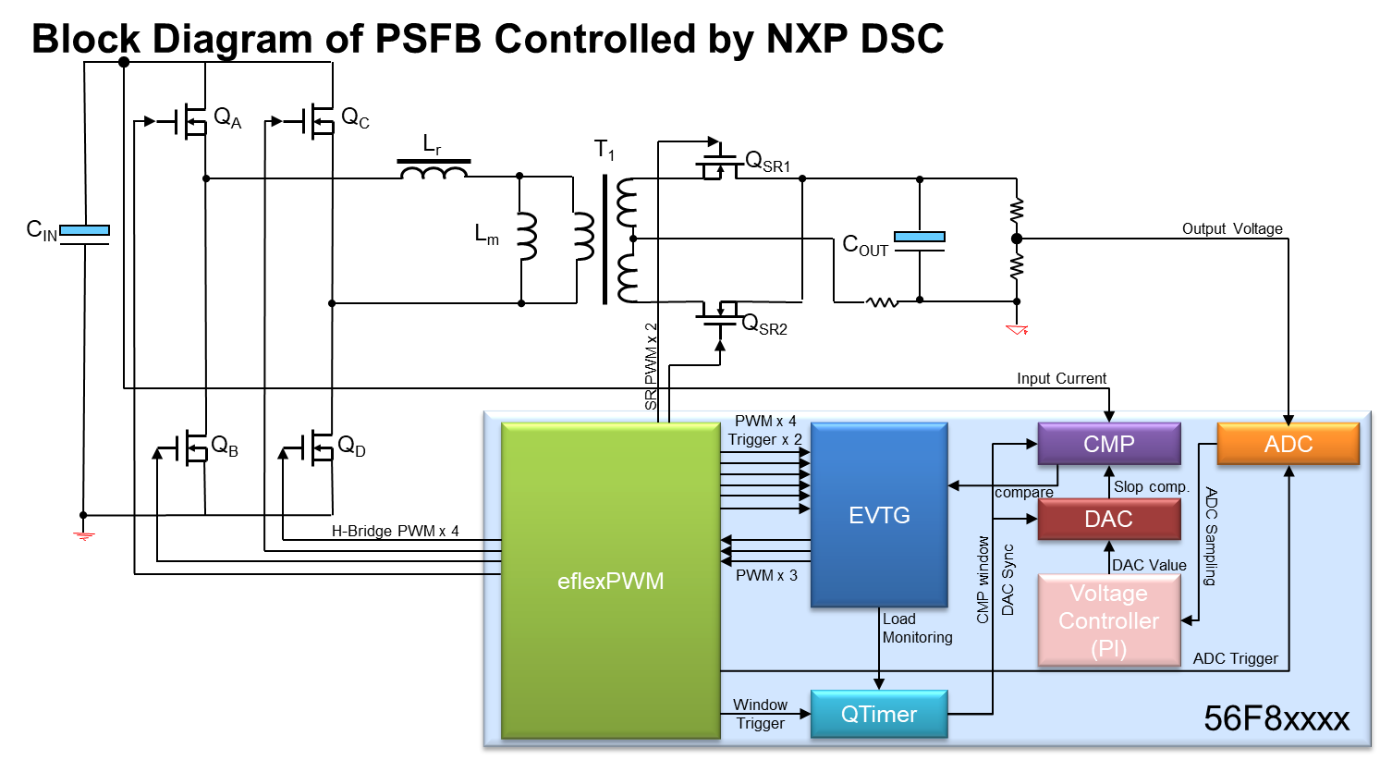

NXP 的 DSC 具備了靈活的功能,使用內部的專用功能互相搭配,可以完成所需波形的所有功能。整體控制環路的框圖可以參考下圖,所有的 PWM 都透過 eflexPWM 模組輸出,內部的數個模組之間互相連動,搭配軟體的 PI 環路控制 PSFB 轉換器的輸出電壓。

NXP PSFB Block Diagram

主要的控制環路,分為由 ADC 與軟體控制器實現的電壓環,以及使用 DSC 硬體實現的電流環。

硬體電流環的實現方式,會使用到幾個內部模組互相搭配。首先是峰值電流偵測的比較器與參考訊號。參考訊號由 DAC 產生,比較器則負責輸出電流採樣訊號與參考訊號比對的結果。

-

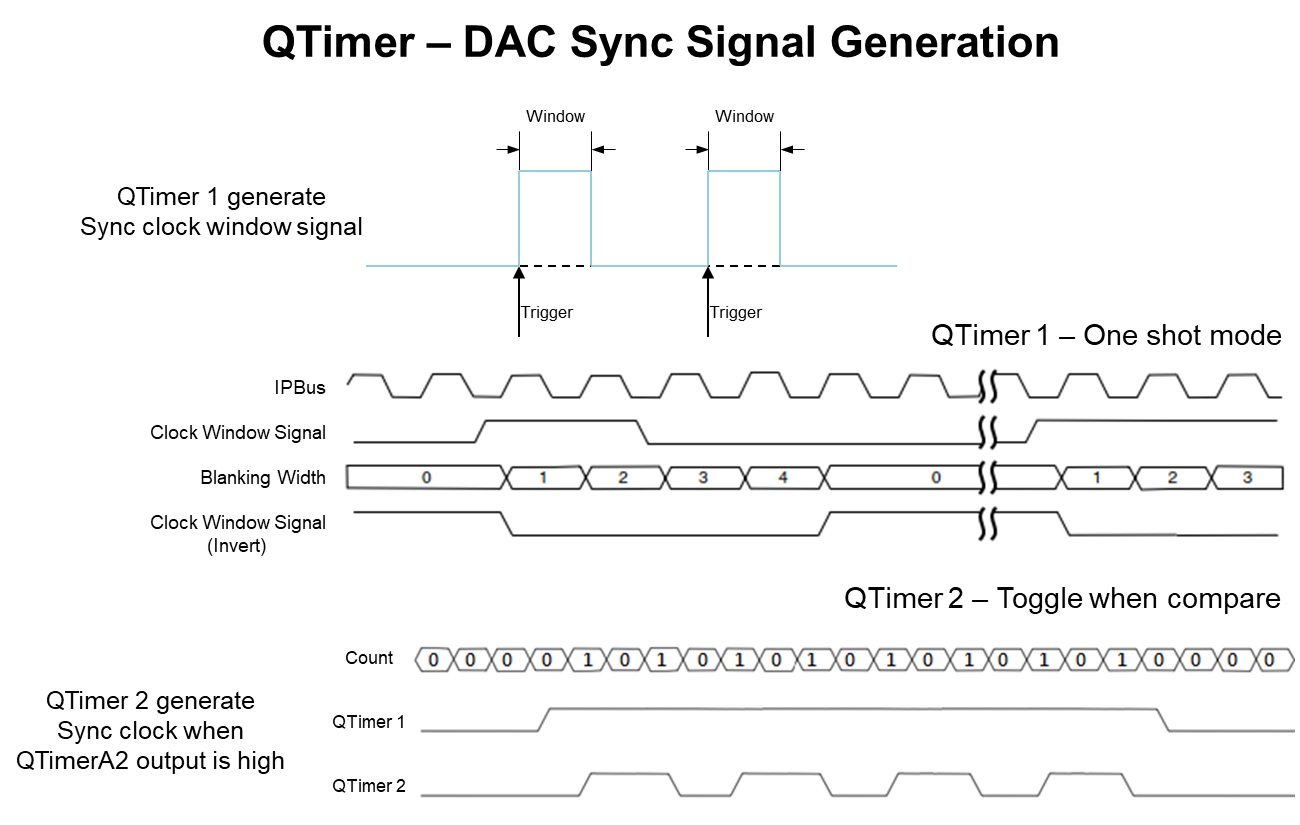

QTimer ( DAC Refresh Trigger ) : 使用兩組 QTimer 通道產生可以連續觸發的 DAC SYNC 訊號,如此一來,當負斜率波形的起點超過 DAC 輸出上限的 3.3V 時,可以使超出 3.3V 的部分維持在 3.3V 。

-

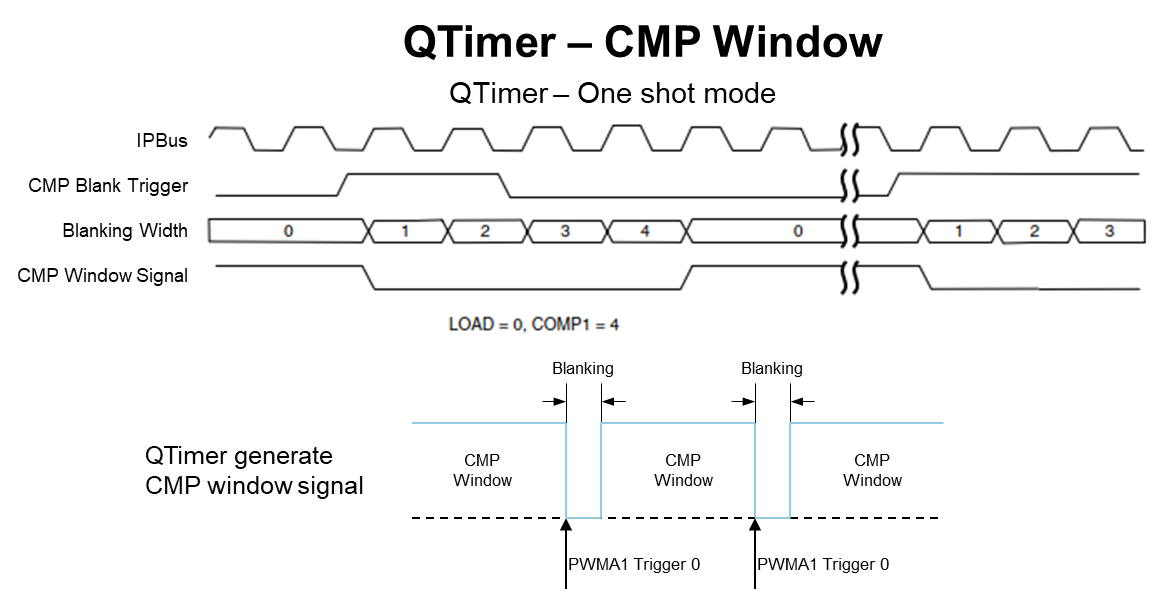

QTimer ( Window ) : 由於在開關切換時的雜訊較大,單靠比較器的濾波來處理不太合適,因此使用 QTimer 用來產生避開雜訊的 Window 訊號,使比較器只在 Window 訊號存在時才會改變輸出。

-

DAC : 帶有自動波形產生功能的 DAC 可以用來產生帶有斜率補償所需的向下斜坡的參考電壓,作為峰值電流控制環路參考電流使用。透過 SYNC 訊號與雙緩衝的暫存器,DAC 可以不使用 CPU 或是 DMA 的資源,就能透過 QTimer 觸發負斜率波形的更新,使負斜率波形的更新完全與 PWM 同步。

-

CMP : 帶有濾波與遲滯級數調整的比較器可以構成峰值控制環路的一部分,並且很好的過濾掉可能產生的雜訊。

-

EVTG : 這個模組內部帶有邏輯閘電路與可程式化正反器,可以透過設置產生全橋波形中 PWM 相移臂的 PWM 來源訊號。

-

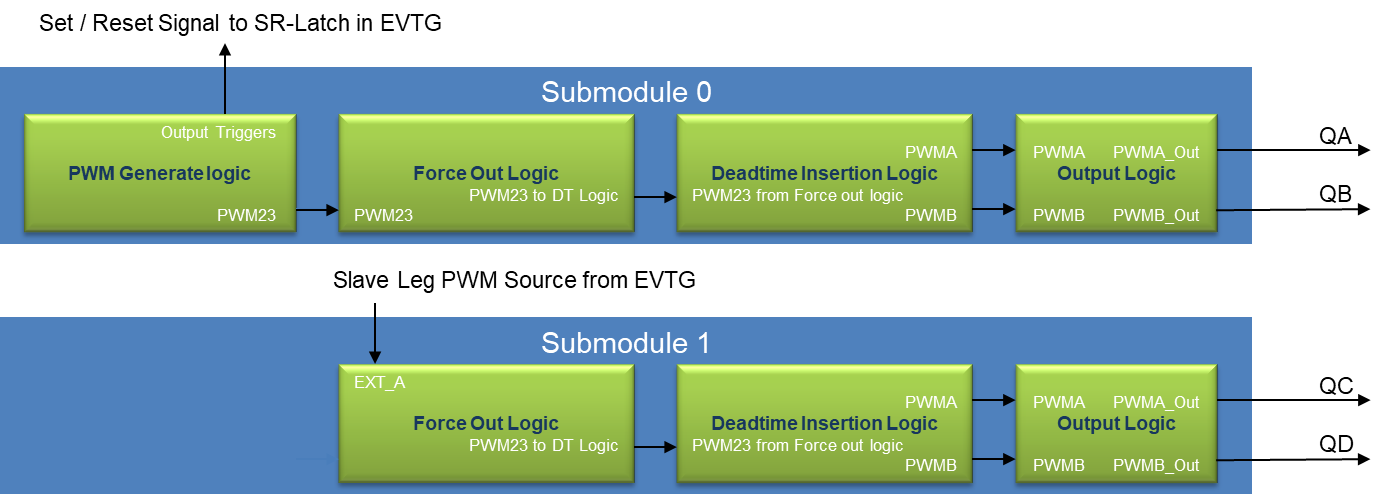

eflexPWM : 第一個通道 ( Submodule 0 ) 負責 PWM 固定臂 PWM 的產生。第二個通道則負責將來自 EVTG 的相移臂 PWM 參考訊號生成帶 Deadtime 的互補對 PWM。

以 DSC 實現的 PSFB 帶有以下優勢 :

-

電流環路完全由硬體機制實現,不占用程式資源。

-

相移臂可以由軟體決定相移量的上限,上限可以在運作中靈活調整,可以與電流偵測的動作並行,不會有誤動作情形。

-

比較器有額外的 Filter 功能,可以確保電流偵測的正確性。

-

比較器帶有 Window 功能,可以無視週期中固定時段產生的特定訊號,比如固定臂開關的 Switching Noise 或 CT 取樣電路的二極體反向恢復雜訊。

-

PWM 全由同一個模組輸出,可以做到與週期同步的 PWM 開啟與關閉,避免開啟或關閉 PWM 時造成 PSFB 硬體上運作有某些不理想的情況發生。

本篇介紹的是 DSC 實現 PSFB 全橋的 PWM,下一篇將針對其中的運作原理與動作的方式進行說明及演示。

若想要知道相關的細節,請聯絡 Jamescl.hsu@wpi-group.com