承接Toshiba TC358746XBG初始化程式碼工具教學(一)說明因為此影像轉換橋接晶片可以進行Parallel to CSI2或是CSI2 to Parallel雙向的功能,僅需要在硬體設計時將MSEL pin腳pull high(Parallel to CSI)或是pull low(CSI to Parallel)即可完成所需影像介面的設定,前文針對Parallel to CSI2初始化程式碼設計方式做了詳細介紹,本文將繼續把CSI2 to Parallel初始化程式碼設計方法做完整的介紹說明。

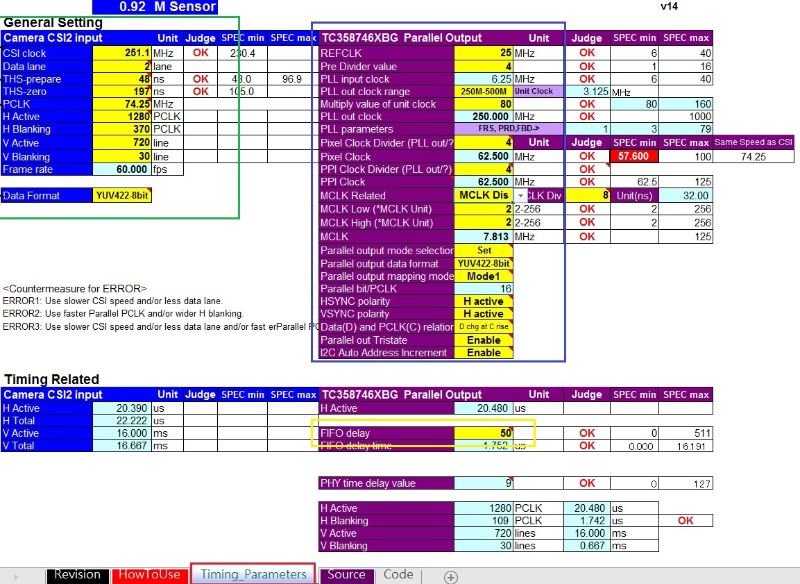

首先打開TC358746XBG CSI to Parallel spreadsheet工具(兩者設計工具為獨立兩個版本)的Timing Parameters介面(如下圖一),點選紅框處即切換到Timing Parameters頁面,CSI to Parallel設計上比較單純所有設定集中在這個頁面完成;首先調整綠框處CSI2 Rx的參數,主要將需要接收CSI2的MIPI clock, lane通道數與影像格式填入,本文範例以1280x720@FPS YUV422影像格式為範例填入,其他PCLK,H/V對應參數僅提供影像轉換timing計算使用並不會影響暫存器設定。

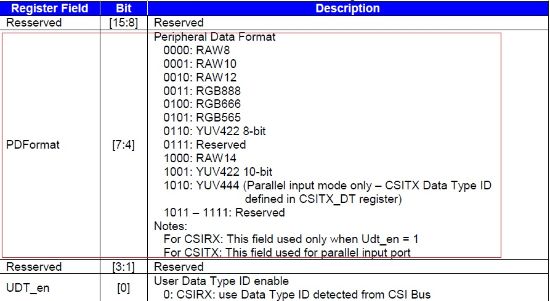

CSI2 Rx接收端設定完成後可以轉到藍框處開始設定Parallel output的相關參數,因為TC358746XBG為event trigger會即時將CSI2封包內Vsync, DE等訊號轉換到對應的Parallel訊號pin輸出,因此這邊僅需要調整對的PCLK設定,由藍框上方依序設定,先設定實際Reference Clock後設定適當提供IC所需的PPL clock設計,再依照PLL clock除頻出所需要的PCLK;Parallel output影像格式可以設定”Follow CSI”或是”set”,前者設定會直接參考CSI2 Rx的格式,後者則可以選擇所需要的格式如圖二列表。

圖一: Timing Parameters介面

圖二: TC358746XBG Parallel輸出影像格式列表

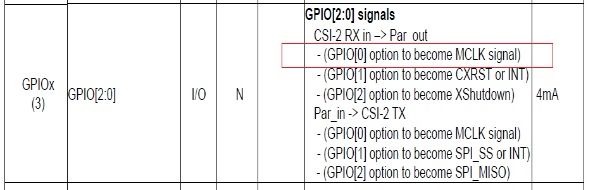

部分需要MCLK需求的device,TC358746XBG也可以支援,只要開啟MCLK Enb即可在GPIO[0]獲得MCLK訊號輸出(如下圖三)。

圖三: MCLK輸出腳位

最後Vsync, DE等訊號Active觸發方式與準位可以依據實際需要調整即完成,所有Timing設定工具都會協助運算,可以調整到”Judge”列表為OK即可。

相關Timing與格式參數設定完成一樣需要確認影像轉換時Fifo設定上是underflow或是overflow,可以調整黃框處Fifo參數將錯誤消除,這樣影像就可以依照所設定的Timing參數與格式順利完成轉換輸出。

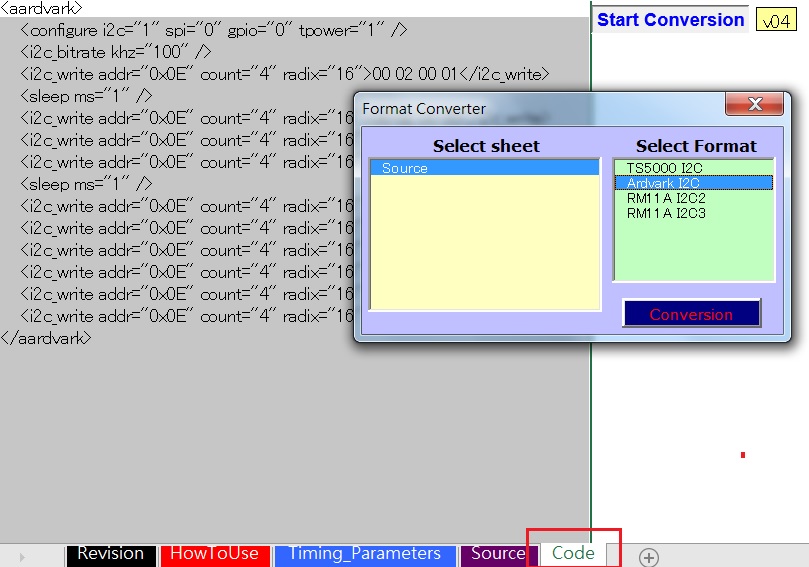

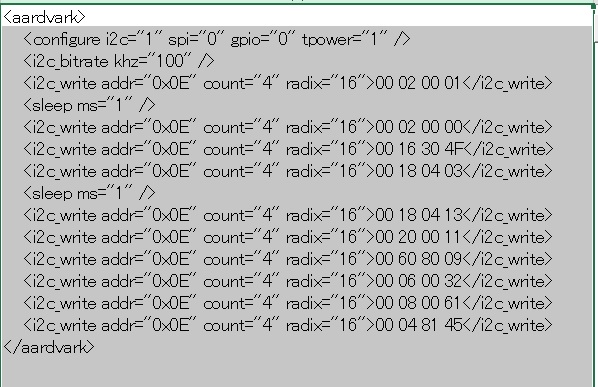

設定都確認完成後,切換到Code頁面(如圖四),點選”Start Conversion”->”Source”->依需求選擇需要產生初始化code碼的格式(符合軟體開發或測試做適合的選用)->”Conversion”即可產生TC358746XBG所需的初始化程序(如圖五),客戶即可參考所產生的初始化code碼進行軟體移植或是開發。

圖四:初始化程序產生頁面

圖五:初始化程序碼產生顯示結果

評論