調試器 - Debugger,是 MCU 開發中必不可少的工具,其主要有以下兩大功能:

- 程序下載

每顆 MCU 出廠時,用於存放代碼的存儲空間都處於擦除狀態,必須通過調試器將應用程序編譯結果下載到其中,才能實現產品功能。

- 程序調試

代碼下載進 MCU 之後,為了驗證代碼功能的正確性,需要查看代碼執行時,CPU 內核和外設控制/配置寄存器以及狀態寄存器和數據寄存器,當然還包括存儲在 SRAM 和 EEPROM 中的算法和控制過程的中間/臨時變量和最終計算結果等。

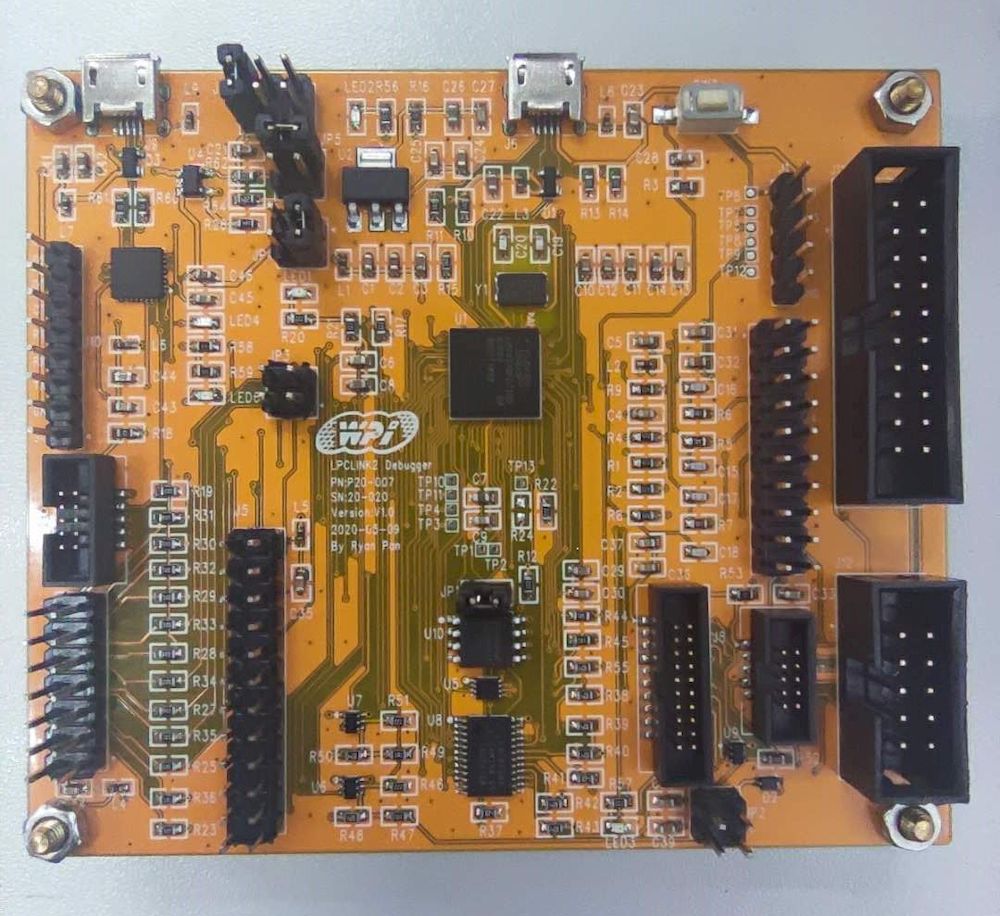

本調試器方案是基於 NXP LPCLINK2 基礎上,進行優化更新的新版本,是一款可擴展、獨立運行的硬體調試器,可使用各種可下載的固件映像來支持各種開發工具和 IDE。可以使用的固件包括 Segger 的板載 J-Link,CMSIS-DAP。功能上新增了 UART 串口調試模塊,便利性上添加了一個 2.54mm 間距的 10pin 插口和一個 2.54mm 間距的 20pin 插口。不僅支持 NXP 絕大部分的 MCU,而且也支持市面上其他非 NXP,支持SWD和 JTAG 標準接口的其他 MCU。主晶片頻率高,工作效率高。

同時也可以用作 LPC4370FET100的評估板,可用外設豐富(有 ADC、UART、I2C、SPI 以及其他多個 I/O 口支持的功能),功能強大,使用便利,是產品開發調試器很好的一個選擇。

硬體設計要點:

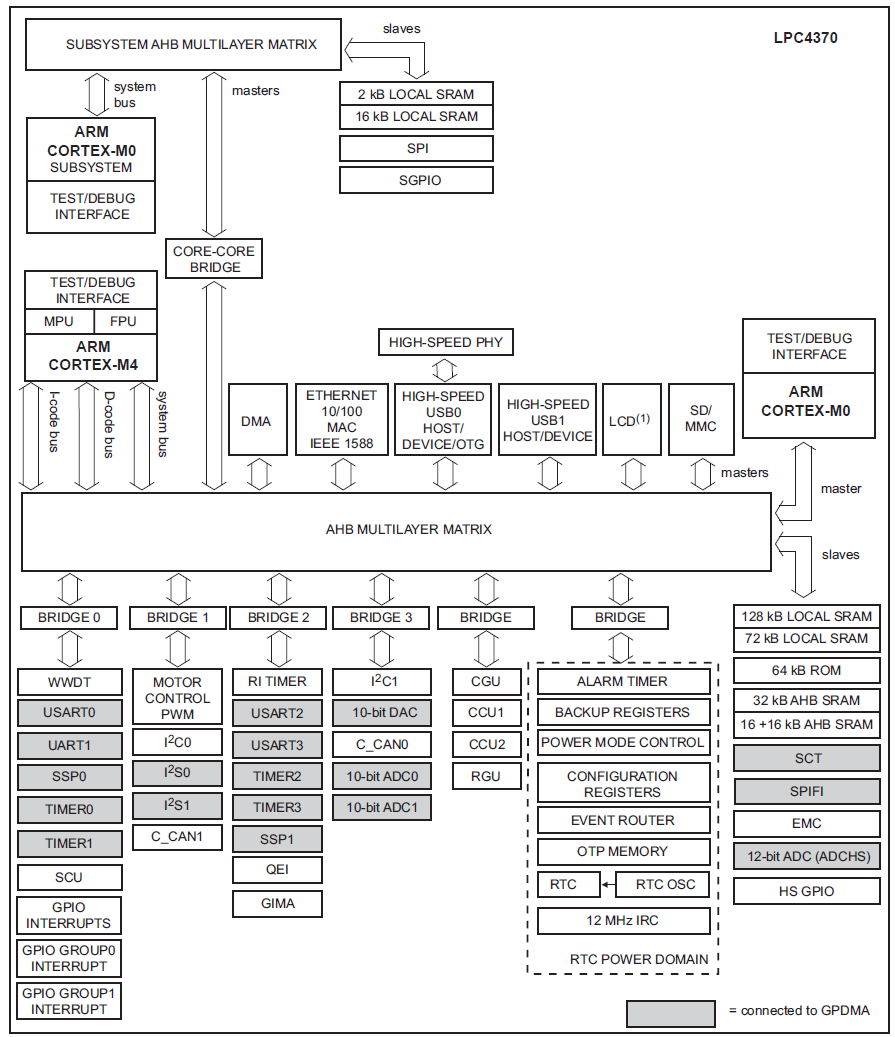

1. 主控選擇 LPC4370FET100 高性能 MCU,無論是用作調試器還是 LPC4370FET100 開發板效率大大提升,具體參數如下:

- 有 2*Cortex-M0+Cortex-M4 三內核

- 運行頻率可以高達 204MHZ

- 無內部 FLASH,內部282 kB of SRAM

- 主控封裝是 TFBGA100(100pin BGA 封裝)

- 支持 USB

- 支持以太網接口

主控框圖如下

2. 外部引腳

該方案有多個接口,10pin 1.27mm 標準 SWD/JTAG 接口,20pin 和 10pin 2.54 間距標準 SWD/JTAG,20pin SWD/JTAG+ETM 接口,用作 LPC4370FET100 評估板的接口(一個基本外設接口,一個數字 I/O 接口,一個模擬ADC+其他數字信號接口)以及 UART 模塊信號輸入輸出接口,並且引出 5V、3.3V 和 GND,需要時可以用作給目標 MCU 板供電使用。

3. 調試器電平兼容處理

調試器模塊選擇兩顆 74LVC1T45、一顆 74LVC2T45 和一顆 74LVC8T245 電平轉換器處理調試器和目標 MCU 連接接口,使 MCU 板輸出到調試器板的信號和調試器板電平一致,使調試器板輸出的信號和 MCU 板點平一致,增加系統的安全性。

4. UART 模塊電平兼容處理

UART 模塊選擇一顆可調輸出電壓的 LDO(SGM2306-ADJ),使用 header 跳線的方式,將 1.8V、3.3V 和 5V 輸出到 USB 轉 UART 串口 IC 的 VCCIO 上, 同時預留一個可以將目標 MCU 板的電平直接送給 VCCIO 的接口,保證了 UART 模塊工作電壓和目標 MCU 板的電壓相同,保證工作的安全性。

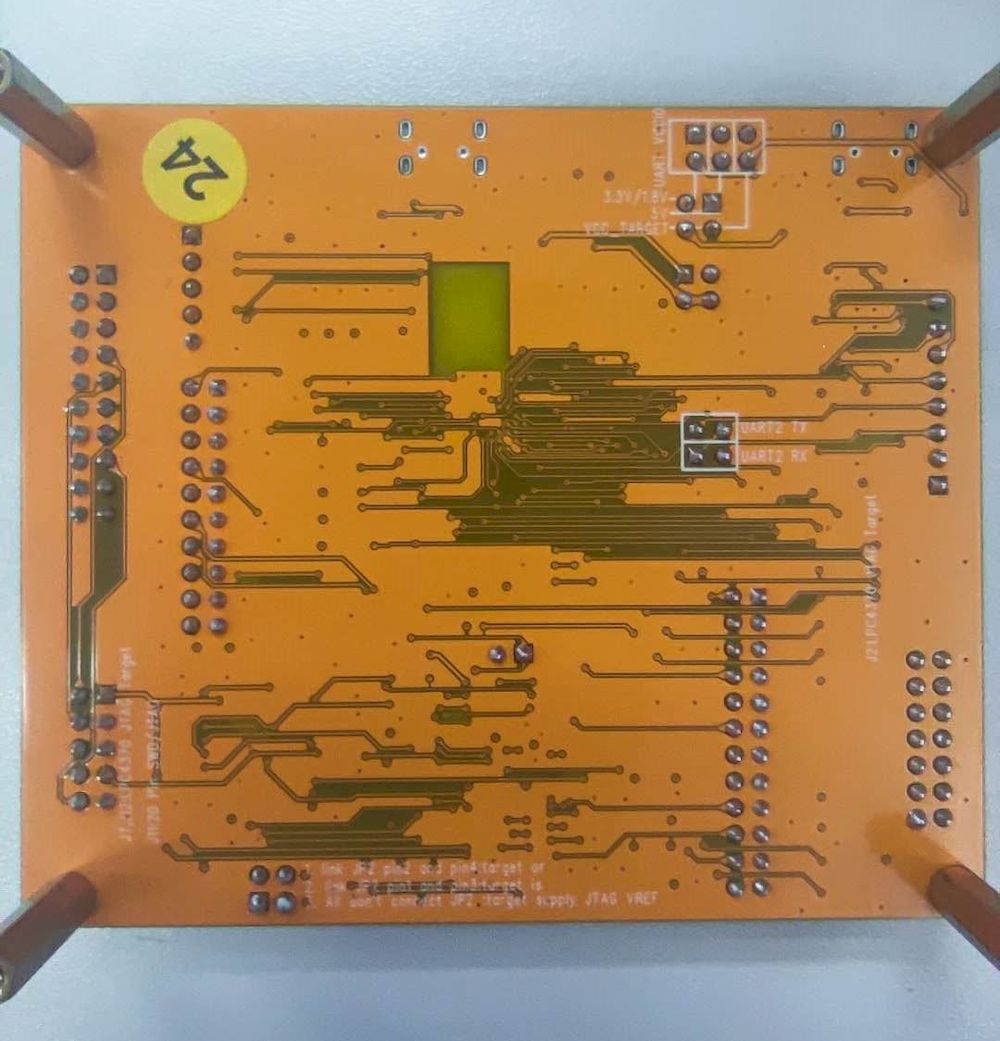

5. PCB 注意要點

PCB 為四層設計,第二層、第三層分別是地層和電源層。電源層為分割平面,分布三個電源,周圍圍一圈地防止外部信號干擾。PCB 畫法採用最基本的畫法,唯一難處在於 BGA晶片走線 5mil 線寬,5mil 間距,這個線寬和間距是最佳方案,常規 0.8mm 間距的 BGA 晶片都可以按這種走線規則走線。

特別需要注意的是晶振的處理,晶振必須緊靠 MCU ,儘量讓晶振走線短。布完線晶振周圍必須要圍一圈地,防止外界干擾,這種干擾可能來自外界干擾信號或者 PCB 製造工藝等多種原因。晶振下面不能有任何金屬,也就是晶振這個區域的所有層都不能鋪銅,避免金屬間產生電容對晶振造成影響。

因為調試器主控頻率高,耗電大,會產生大量的熱,PCB 要注意主控的散熱。

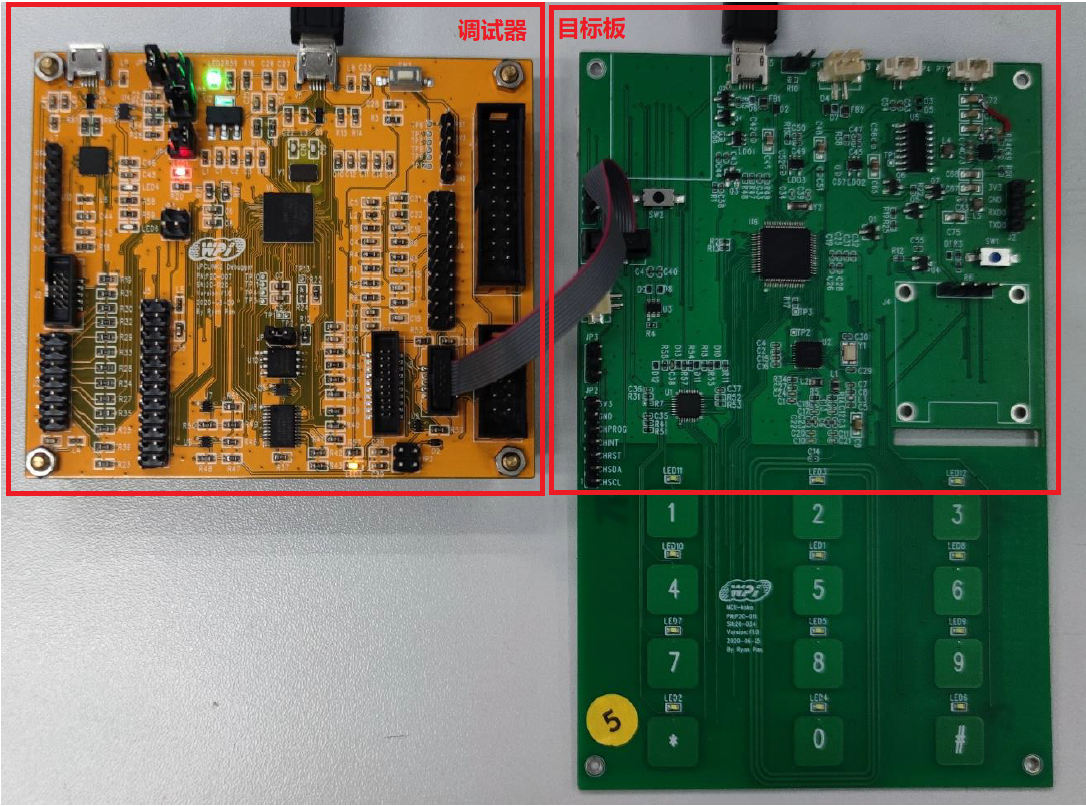

►場景應用圖

►展示板照片

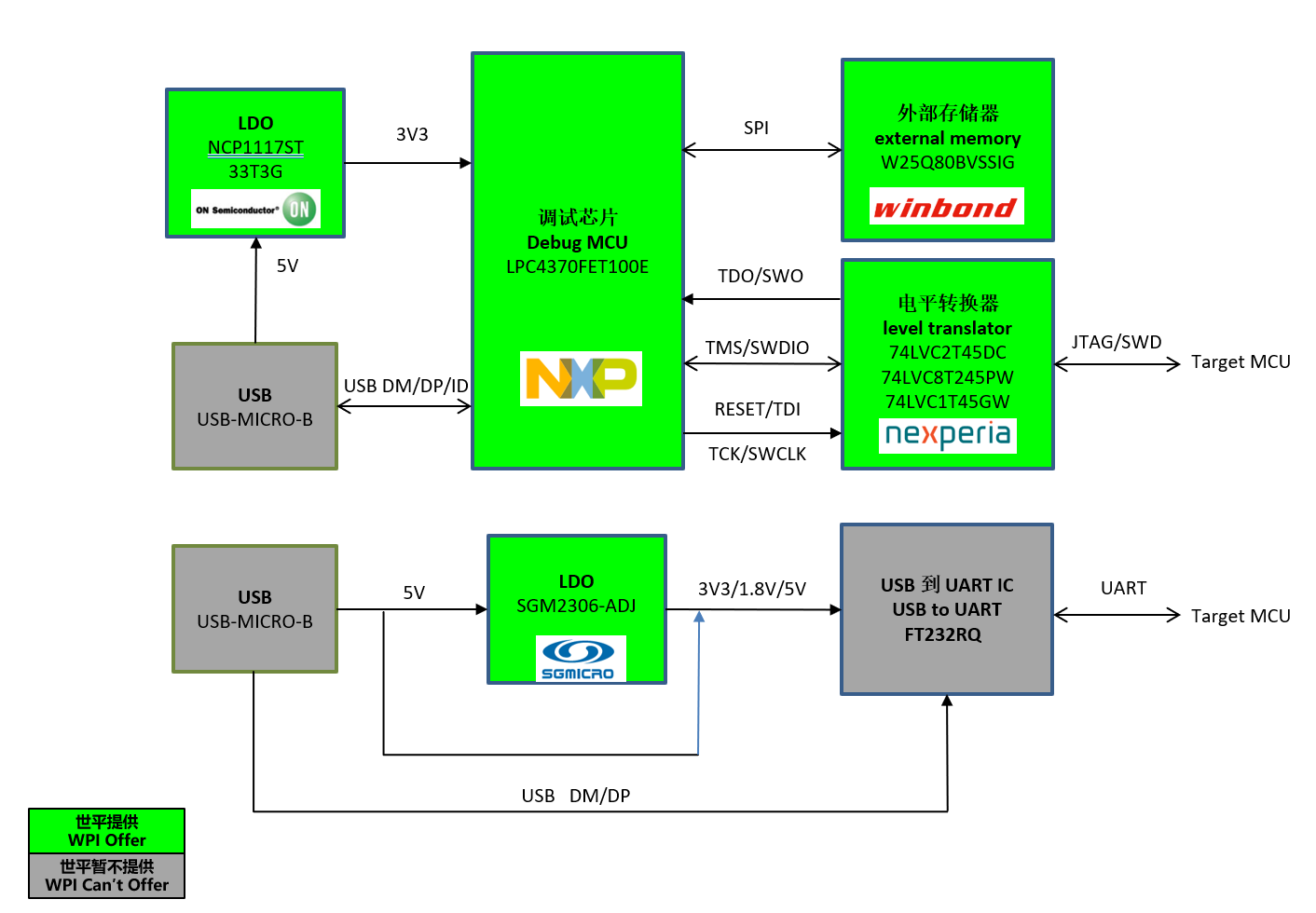

►方案方塊圖

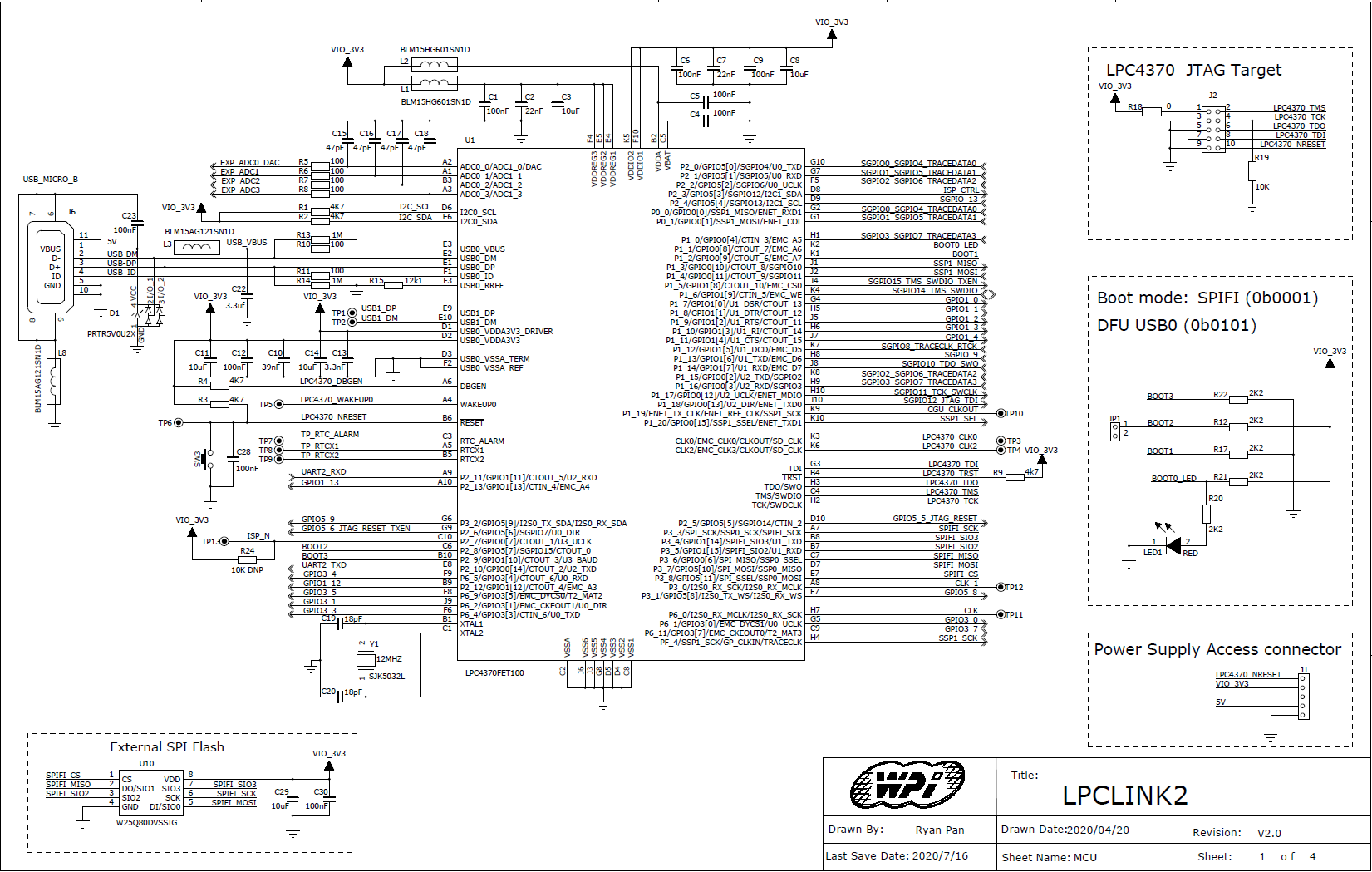

►方案原理圖

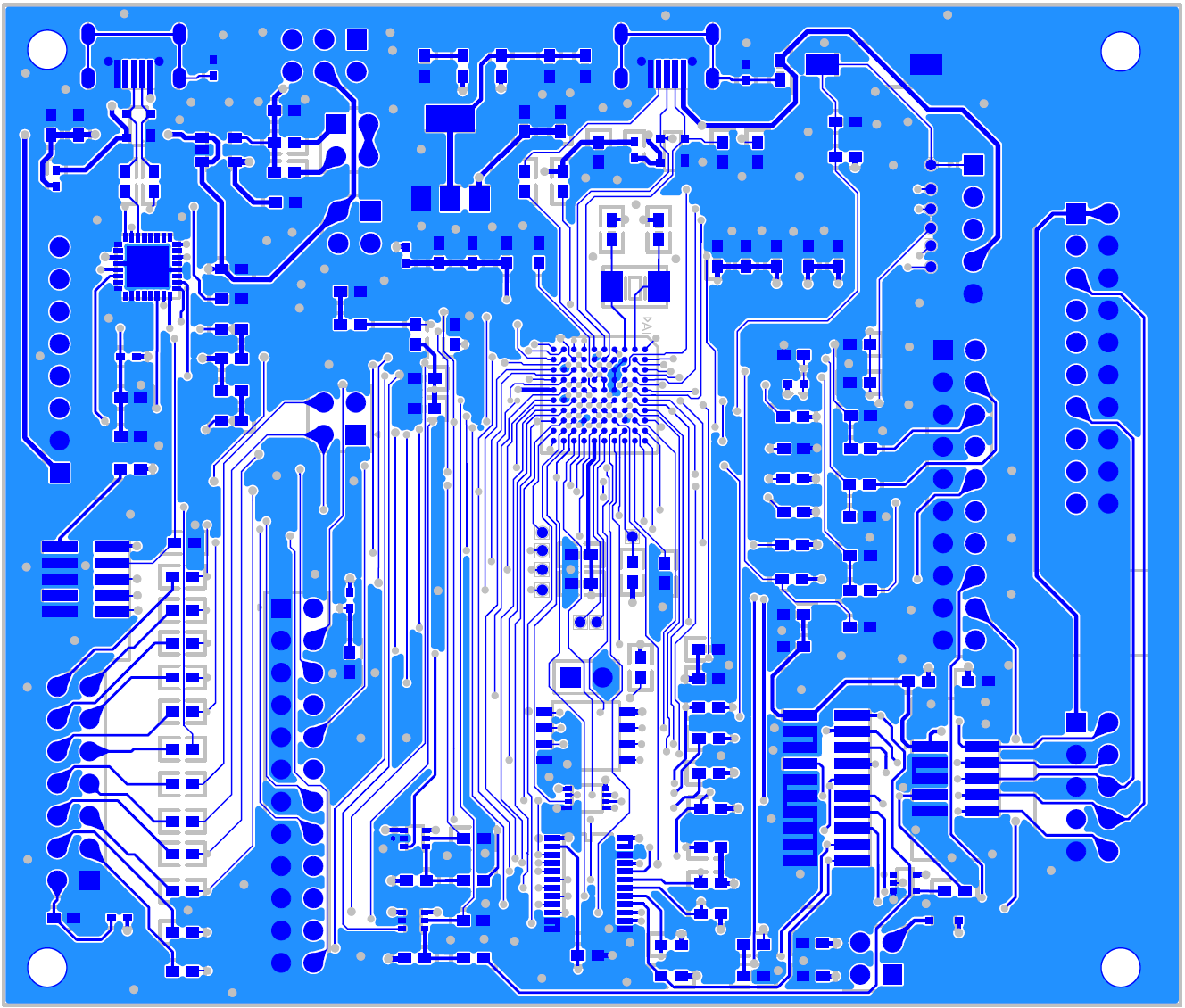

►PCB-Layer1-TOP

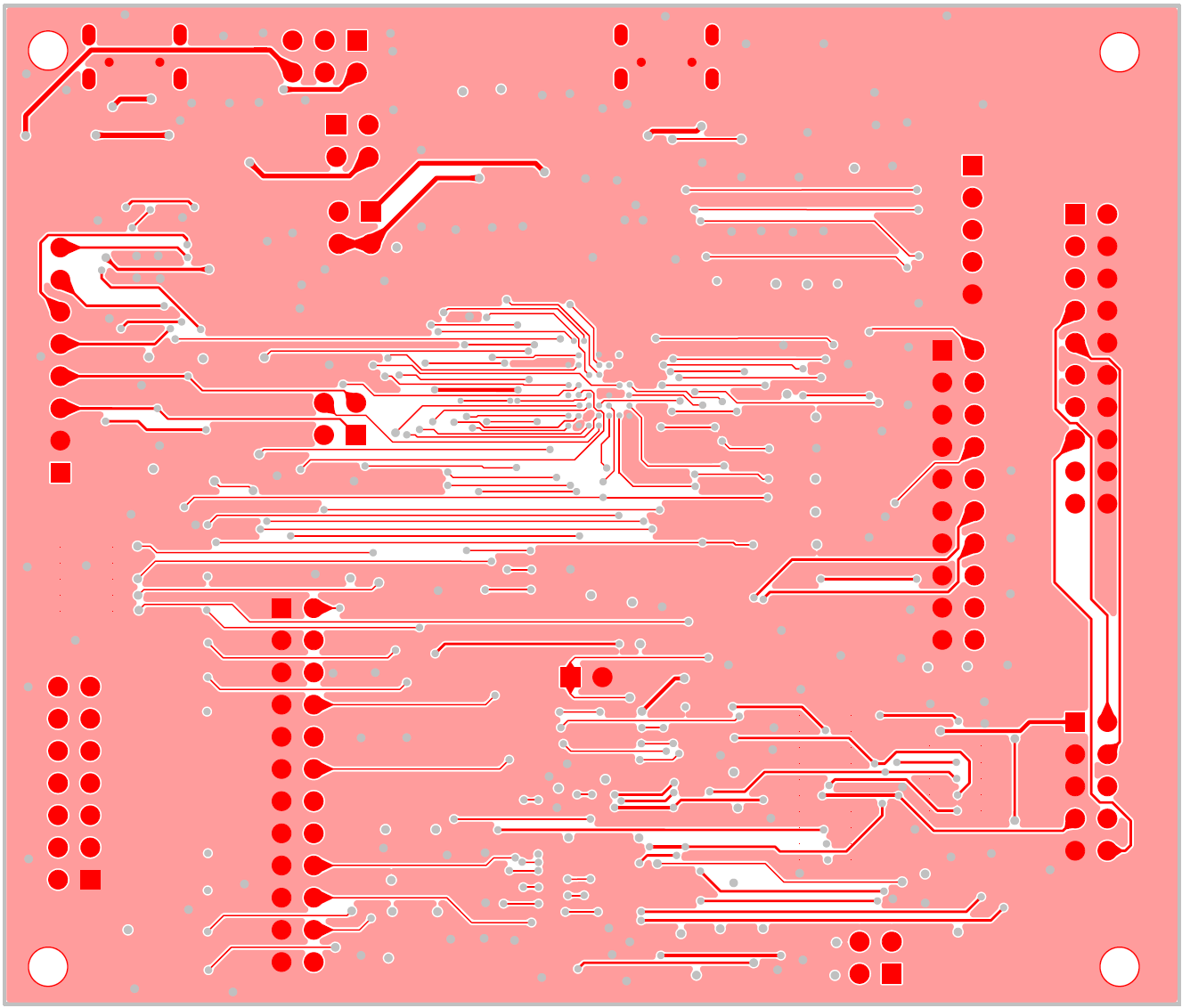

►PCB-Layer4-Bottom

►核心技術優勢

1. 調試器支持大部分 NXP MCU: KL Series Cortex-M0+ K4x USB & Segment LCD K6x Ethernet K2x USB KE Series Cortex-M4/M0+ K1x Mainstream LPC1200 Cortex-M0 LPC1100 Cortex-M0+/M0 i.MX RT Crossover MCUs K8x Secure LPC800 Cortex-M0+ K3x Segment LCD KV Series Cortex-M4/M0+/M7 K5x Measurement K0x Entry-Level K7x Graphic LCD KM Series Cortex-M0+ LPC54000 Cortex-M4 可調式其他支持 SWD,JTAG標準接口的 MCU 2. LPCLINK2 可編譯為 CMSIS-DAP 和 J-LINK2,功能強大。 3. 可當做 LPC4370FET100 開發板使用。 4. 支持 1.8V、3.3V、5V UART 串口調試。 5. 支持不同電平的系統(1.8V~5V)。

►方案規格

1. 支持 1.8V~5V 系統。 2. 可供 5V 和 3.3V 電壓給目標 MCU 板。 3. 有 2*Cortex-M0+Cortex-M4 三內核。 4. 主控內部 282 kB SRAM,外接 SPI Flash。 5. USB供電,主晶片輸入電壓 3.3V。 6. 有多功能性,可用作調試器和 LPC4370FET100開發板。 7. 外部引出 LPC4370FET100 GPIO,ADC,I2C,SPI,UART 等外設供開發板模式時使用。 8. 主晶片 package: TFBGA100。