一、 概述

本文将详细介绍 NXP S32K1xx 系列 MCU 的时钟模块的相关知识,包括对 S32K1xx的时钟架构的介绍、各模式下的时钟配置要求以及对时钟监控模块的介绍。

二、 S32k1xx时钟架构

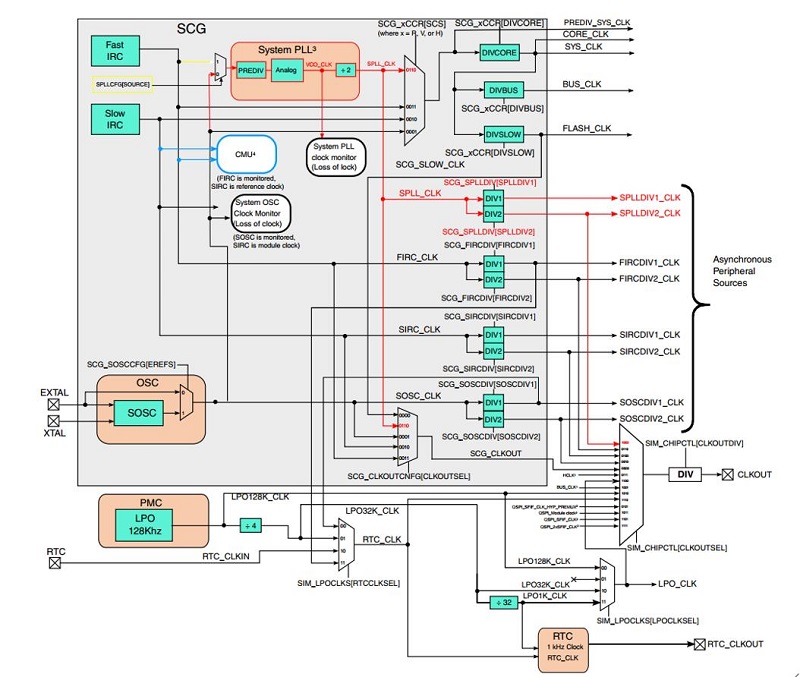

如下图所示为 S32K1xx MCU 的时钟架构图,从图中我们可以看到每个时钟的路径,包括时钟源的选择以及时钟分频的设置,可以看到 S32K1xx 内部的时钟

源包括 FIRC、SIRC 和 LPO128KHz,外部时钟源包括 SOSC 和 RTC。需要注意的是,图中黄线部分是 S32K14xW 芯片仅有的功能,蓝线部分为 S32K11x 仅有的功能。

图 2.1 S32K1xx 时钟架构图

关于 S32K1xx 各个时钟的定义如下表所示

|

时钟 |

描述 |

|

PREDIV_SYS_CLK |

HSRUN 80MHz 模式下 QSPI 存储器时钟 |

|

CORE_CLK |

Arm 核的时钟 |

|

SYS_CLK |

系统时钟,为交叉开关、NVIC、Flash 控制器、FTM、PDB 等模块的时钟 |

|

BUS_CLK |

芯片外设的时钟 |

|

FLASH_CLK |

内部 Flash 的时钟 |

|

SPLL_CLK |

PLL 的输出时钟 |

|

SIRC_CLK |

内部低速时钟,由 SCG 模块生成 |

|

FIRC_CLK |

内部高速时钟,由 SCG 模块生成 |

|

SOSC_CLK |

外部晶振时钟 |

|

RTC_CLKOUT |

RTC 时钟输入,连接到外部引脚 |

|

LPO32K_CLK |

RTC 的时钟源 |

|

LPO128K_CLK |

PMC 模块生成的低功耗振荡器时钟 |

|

SCG_CLKOUT |

SCG 输出时钟,可以由 SOSC_CLK、SIRC_CLK、FIRC_CLK、SPLL_CLK、SCG_SLOW_CLK 中的其中一个生成。 |

|

LPO_CLK |

LPO 时钟,可以是 LPO128K、LPO32K、LPO1K 中的其中一个生成 |

|

CLKOUT |

由八个内部时钟中的一个生成,连接到外部引脚 |

|

VCO_CLK |

VCO 输出时钟,其频率为 SPLL_CLK x 2 |

|

SPLLDIV1_CLK |

由 SPLL_CLK 分频生成,RUN 模式下配置为 80 MHz 或以下,HSRUN 模式下配置为 112 MHz 或以下 |

|

SPLLDIV2_CLK |

由 SPLL_CLK 分频生成,RUN 模式下配置为 40 MHz 或以下,HSRUN 模式下配置为 56 MHz 或以下 |

|

FIRCDIV1_CLK |

由 FIRC_CLK 分频生成,在 RUN/HSRUN 模式下应配置成 48 MHz 或以下 |

|

FIRCDIV2_CLK |

同上 |

|

SIRCDIV1_CLK |

由 SIRC_CLK 分频生成,在 RUN/HSRUN 模式下应配置成 8 MHz 或以下,在 VLPR/VLPS 模式下配置成 4MHz 或以下 |

|

SIRCDIV2_CLK |

同上 |

|

SOSCDIV1_CLK |

由 SOSC_CLK 分频生成,在 RUN/HSRUN 模式下应配置成 40 MHz 或以下 |

|

SOSCDIV2_CLK |

同上 |

表 2.1 S32K1xx 时钟定义

三、各模式下的时钟配置

S32K1xx 时钟相关的模块主要有 SCG(System Clock Generator) 和 PCC (Peripheral Clock Controller)两个模块,SCG 模块主要用于提供 MCU 的

系统时钟,SCG 模块包含了一个系统锁相环 SPLL ,一个内部低速时钟 SIRC,一个内部高速时钟 FIRC 和系统振荡器时钟 SOSC。SPLL 的时钟源可以是

SOSC 或者 FIRC。PCC 模块用于控制外设时钟的开关,如果外设还有功能时钟,PCC 模块还提供时钟源选择和分频的选项。可以通过 PCC 寄存器的 PCS

域和 PCD 域进行配置。

SCG 模块的寄存器描述如表 3.1所示。

|

SCG 寄存器 |

功能描述 |

|

SCG_VERID |

SCG 的版本号寄存器,只读 |

|

SCG_PARAM |

SCG 参数寄存器,用来读取 SCG 的系统时钟分频和时钟源是否存在 |

|

SCG_CSR |

通过该寄存器读取当前的系统时钟源,内核时钟分频和总线时钟分频 |

|

SCG_RCCR |

该寄存器控制 RUN 模式下的时钟源选择以及内核时钟分频和总线时钟分频 |

|

SCG_VCCR |

该寄存器控制 VLPR 模式下的时钟源选择以及内核时钟分频和总线时钟分频 |

|

SCG_HCCR |

该寄存器控制 HSRUN 模式下的时钟源选择以及内核时钟分频和总线时钟分频 |

|

SCG_CLKOUTCNFG |

该寄存器选择那个时钟源输出到 CLKOUT 引脚 |

|

SCG_SOSCCSR |

系统振荡器 SOSC 的控制状态寄存器 |

|

SCG_SOSCDIV |

系统振荡器 SOSC 的分频寄存器,可以设置两路分频时钟 |

|

SCG_SOSCCFG |

系统振荡器 SOSC 的配置寄存器,可以选择 SOSC 的频率范围、参考时钟等 |

|

SCG_SIRCCSR |

内部低速时钟 SIRC 的控制状态寄存器 |

|

SCG_SIRCDIV |

内部低速时钟 SIRC 分频寄存器,可以设置两路分频时钟 |

|

SCG_SIRCCFG |

内部低速时钟 SIRC的配置寄存器,可以选择 SIRC的频率范围 |

|

SCG_FIRCCSR |

内部高速时钟 FIRC 的控制状态寄存器 |

|

SCG_FIRCDIV |

内部高速时钟 FIRC的分频寄存器,可以设置两路分频时钟 |

|

SCG_FIRCCFG |

内部高速时钟 FIRC的配置寄存器,可以选择 FIRC 的频率范围 |

|

SCG_SPLLCSR |

系统锁相环 SPLL 的控制状态寄存器 |

|

SCG_SPLLDIV |

系统锁相环 SPLL 的分频寄存器,可以设置两路分频时钟 |

|

SCG_SPLLCFG |

系统锁相环 SPLL 的配置寄存器,可以设置 SPLL 的时钟源,分频系数和倍频系数 |

表 3.1 SCG 寄存器描述

关于时钟的设置需要满足下面几点要求:

- 在 RUN 模式下 CORE_CLK 和 SYS_CLK 的频率应该设置为 80 MHz 或以下,在 HSRUN 模式下应设置为 112 MHz 或以下。(不可低于 BUS_CLK 的频率)

- 在 RUN 模式下 BUS_CLK 的频率应设置为 48 MHz 或以下,在 HSRUN 模式下应设置为 56 MHz 或以下。

- 在 RUN 模式下, FLASH_CLK 的频率应设置为 67 MHz 或以下,在 HSRUN 模式下应设置为 28 MHz 或以下,并且是 CORE_CLK 的整数分频(最大为 8)。

下面列举了在 Normal RUN、Slow RUN、HSRUN、VLPR 等 4 种模式下时钟配置的例子。

- 在 Normal RUN 模式下,SCG 寄存器配置及频率如下表所示

|

时钟 |

频率 |

寄存器配置 | |

|

|

S32K14x 和 S32K11x |

S32K14xW |

SCG_RCCR[SCS] = 0110b SCG_RCCR[DIVCORE] = 0001b SCG_RCCR[DIVBUS] = 0001b SCG_RCCR[DIVSLOW] = 0010b

|

|

CORE_CLK |

80MHz |

80 MHz | |

|

SYS_CLK |

80MHz |

80 MHz | |

|

BUS_CLK |

40MHz |

40 MHz | |

|

FALSH_CLK |

26.67 MHz |

20 MHz | |

表 3.2 Normal RUN 模式 SCG 寄存器配置

- 在 Slow RUN 模式下 SCG 寄存器的配置及频率如下(时钟源选择 FIRC):

|

时钟 |

频率 |

寄存器配置 | |

|

|

S32K14x 和 S32K11x |

S32K14xW |

SCG_RCCR[SCS] = 0011b SCG_RCCR[DIVCORE] = 0000b SCG_RCCR[DIVBUS] = 0000b SCG_RCCR[DIVSLOW] = 0001b

|

|

CORE_CLK |

48 MHz |

48 MHz | |

|

SYS_CLK |

48 MHz |

48 MHz | |

|

BUS_CLK |

48 MHz |

48 MHz | |

|

FALSH_CLK |

24 MHz |

16 MHz | |

表 3.3 Slow RUN 模式 SCG 寄存器配置

- 在 112MHz 的HSRUN 模式下 SCG 寄存器的配置及频率如下(仅 S32K14x 支持):

|

时钟 |

频率 |

寄存器配置 |

|

CORE_CLK |

112 MHz |

SCG_HCCR[SCS] = 0110b SCG_HCCR[DIVCORE] = 0000b SCG_HCCR[DIVBUS] = 0001b SCG_HCCR[DIVSLOW] = 0011b

|

|

SYS_CLK |

112 MHz | |

|

BUS_CLK |

56 MHz | |

|

FALSH_CLK |

28 MHz |

表 3.4 HSRUN 模式 SCG 寄存器配置

- 在 VLPR 模式下 SCG 寄存器的配置及频率如下

|

时钟 |

频率 |

寄存器配置 | |

|

|

S32K14x 和 S32K11x |

S32K14xW |

SCG_VCCR[SCS] = 0010b SCG_VCCR[DIVCORE] = 0001b SCG_VCCR[DIVBUS] = 0000b SCG_VCCR[DIVSLOW] = 0011b

|

|

CORE_CLK |

4 MHz |

1 MHz | |

|

SYS_CLK |

4 MHz |

1 MHz | |

|

BUS_CLK |

4 MHz |

1 MHz | |

|

FALSH_CLK |

1 MHz |

0.25 MHz | |

表 3.5 VLPR 模式 SCG 寄存器配置

四、时钟监控模块

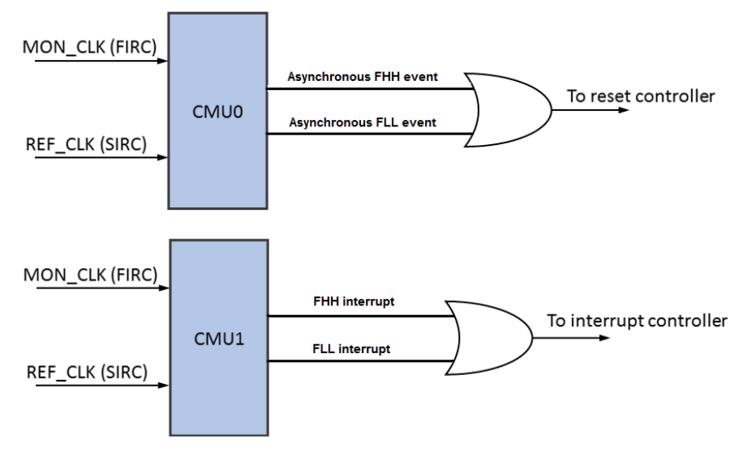

时钟监控模块(CMU)仅支持 S32K11x 系列芯片,CMU 模块有两个实例 CMU0 和 CMU1,用来监测 FIRC 时钟,默认情况下 CMU 模块是关闭的,如果要使用需要进行相关配置。CMU 的两个实例分别用于生成复位和中断,当检测到时钟频率不在设置的阈值区间时会产生复位,而 CMU1 则是当检测到的时钟频率不在设置的阈值区间时会产生中断,CMU 模块在芯片内部的连接示意图如下所示。

图 4.1 CMU 模块连接图

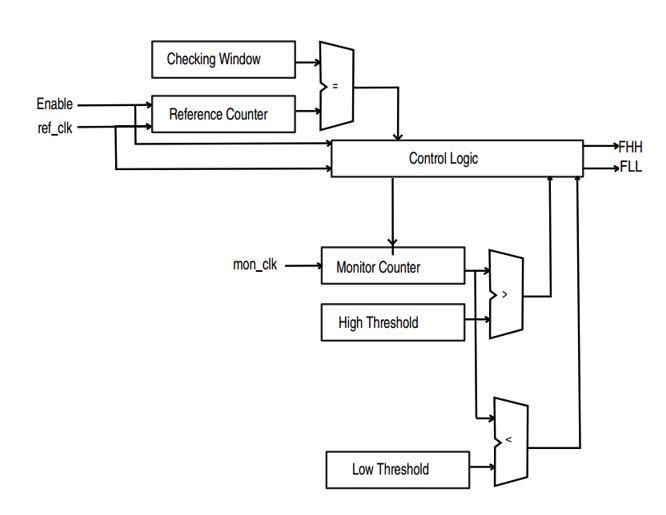

CMU 模块的检测原理是在设置的监控周期(N 个参考时钟,可以通过 RCCR 寄存器设置 )内对所监控的时钟周期数进行计数,在监控周期结束后将该计数值和用户设定的阈值进行比较(该阈值通过寄存器 HTCR 和 LTCR 进行配置),当超过设定阈值后状态寄存器 SR 对于的状态位会置位,如果有设置中断使能,则会产生相应的中断。

图 4.2 CMU 模块工作原理示意

CMU 模块的寄存器定义如下表所示。

|

寄存器 |

功能描述 |

|

GCR |

该寄存器用于使能 CMU_FC 模块,当 GCR[FCE] = 1 时使能 CMU_FC 模块 |

|

RCCR |

该寄存器用于设置频率检测窗口的大小 |

|

HTCR |

该寄存器用于设置监控时钟计数器的高阈值 |

|

LTCR |

该寄存器用于设置监控时钟计数器的低阈值 |

|

SR |

该寄存器为状态寄存器,通过该寄存器可以查看 CMU 的运行状态,是否出现时钟频率超出阈值范围的事件 |

|

IER |

该寄存器为中断使能寄存器,可以配置是否使能时钟异常中断 |

表 4.1 CMU 模块寄存器定义

关于 CMU 模块的推荐配置流程如下:

- 设定 RCCR[REF_CNT] 域来配置时钟检测的窗口时间

- 设定 LTCR[LFREF] 和 HTCR[HFREF] 域来配置监控时钟的高低阈值

- 如果需要的话设定 IER 寄存器来使能中断

- 完成以上步骤后设定 GCR[FCE] = 1 来启动时钟监控的功能,当时钟监控使能后,RCCR,LTCR[LFREF] 和 HTCR[HFREF] 都不允许进行写入操作,否则会出现总线传输错误

- 如果要修改 RCCR 、LTCR[LFREF] 或 HTCR[HFREF] 的配置,则需要在 SR[RS] = 1 时设置 GCR[FCE] = 0。

五、参考资料

- NXP ,《S32K1XXRM》https://www.nxp.com.cn/webapp/sps/download/preDownload.jsp?render=true

- NXP ,《S32K-DS》, https://www.nxp.com.cn/docs/en/data-sheet/S32K-DS.pdf

评论