我们平时在查阅芯片规格书的时候,通常其参数页,都有介绍芯片的ESD能力。如在HBM、MM、CDM下,能满足多少KV的ESD。

我们平时在查阅芯片规格书的时候,通常其参数页,都有介绍芯片的ESD能力。如在HBM、MM、CDM下,能满足多少KV的ESD。

摘自某28nm SoC产品 datasheet

但当我们在做产品的ESD测试时又会发现,认证要求的是IEC的标准。那么这些不同的ESD测试到底是什么意思,又有何不同?

系统级和器件级ESD标准

代表电子设备在终端所有的应用环境内的抗损能力

通常只代表芯片在生产制造、运输、贴片焊接等过程中的抗损能力

器件级ESD模型:HBM 人体放电模型

评估IC单体的ESD模型有很多种,其中最为典型的是JEDECJESD22-A114E的HBM模型(人体放电模型),模拟人体静电对敏感IC的作用。

其等效电路为:

HBM放电波形图

HBM放电,其上升时间(tr)一般为2~10ns,衰退时间(td)一般为130~170ns。

一般芯片都会采用HBM来表征静电等级,而商用IC的HBM标准,通常为2KV,其峰值电流可达1.33A。

系统级ESD模型:IEC标准模型

系统静电测试设备

IEC61000-4-2标准模型是目前国内外整机ESD测试最为通用的标准,模拟带电人体持金属对受试设备(DUT)进行放电,属于系统级测试标准。

IEC 模型放电波形图

IEC模型放电,其上升时间(tr)一般为0.7~1ns,衰退时间(td)一般为100ns。

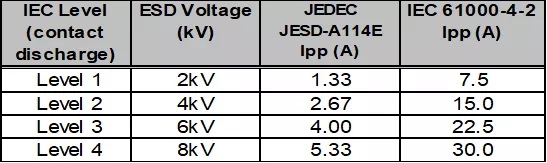

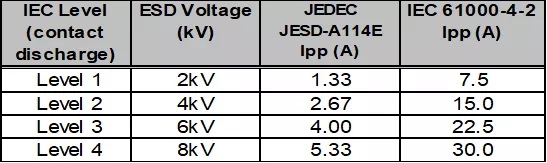

IEC标准的ESD测试分为四个等级,如下图所示:

IEC 模型放电波形图

IEC模型放电,其上升时间(tr)一般为0.7~1ns,衰退时间(td)一般为100ns。

IEC标准的ESD测试分为四个等级,如下图所示:

对于普通消费类产品,一般采用接触放电4~6KV,空气放电8KV;而对于偏工业类的或人为使用较频繁的设备,一般采用接触放电8KV及以上,空气放电15KV及以上的测试要求。

对于ESD测试的要求,一般厂家只能接受A级或B级,即设备在规定范围内能正常工作或可自行恢复的暂时性功能异常,而不能接受C级或D级,即需操作者介入或系统必须重启才能解除的异常或更为严重的设备硬件、软件损坏,或数据丢失造成不可恢复的异常现象。

对于普通消费类产品,一般采用接触放电4~6KV,空气放电8KV;而对于偏工业类的或人为使用较频繁的设备,一般采用接触放电8KV及以上,空气放电15KV及以上的测试要求。

对于ESD测试的要求,一般厂家只能接受A级或B级,即设备在规定范围内能正常工作或可自行恢复的暂时性功能异常,而不能接受C级或D级,即需操作者介入或系统必须重启才能解除的异常或更为严重的设备硬件、软件损坏,或数据丢失造成不可恢复的异常现象。

系统级 vs. 器件级 对比1

2KV ESD波形比较

通过前面的叙述,我们知道,系统级和器件级的ESD事件都类似于一个电容的充放电过程。由于充电电容和放电电阻的不同,造成了它们能量上的巨大差异。同样是2KV的ESD,HBM下的上升时间为2~10ns,峰值电流为1.33A,而在IEC下的上升时间为0.7~1ns,峰值电流为7.5A 。

相比较而言,系统级的ESD具有更快的上升时间和更大的峰值电流,这就对敏感芯片冲击力更大,在保护器件的选取上则要选择响应时间更快的,ESD电流吸收能力更好的保护器件。

系统级 vs. 器件级 对比2

虽然我们知道JEDEC和IEC之间有差异,那么我们在做系统级ESD防护的时候可以参考芯片规格书里的哪些参数呢?HBM的ESD等级能做为评判系统级ESD测试的标准吗?

通过电容的储能公式:

我们知道,在同样的充电电压下,IEC标准的150pF 电容储存的能量将会比JECEC的100pF 高出50%。

而1500Ω 的放电电阻又会比330Ω 的消耗更多的能量,故在待测设备上消耗的能量计算公式为:

因此,如果同样作用于50Ω 的负载上,IEC的ESD能量将会是HBM的6倍之多。这也告诉了我们,为什么不能拿芯片规格书上标的ESD能力,来作为其整机ESD测试的参照。

综上所述,芯片规格书上所写的ESD等级,如HBM下的ESD能力,只适合于表征它在生产制造、运输、贴片焊接等过程中的抗损能力。对于我们整机ESD测试来说,因为在同级别下的系统级ESD能量是器件级的6倍之多,所以,HBM等级不能做为整机ESD测试的参考,而要选择IEC等级的ESD来做为整机测试的标准。

★博文内容参考自 网站,与平台无关,如有违法或侵权,请与网站管理员联系。

★文明上网,请理性发言。内容一周内被举报5次,发文人进小黑屋喔~

评论