一、i.MX8DX 简介及 GPIO 说明

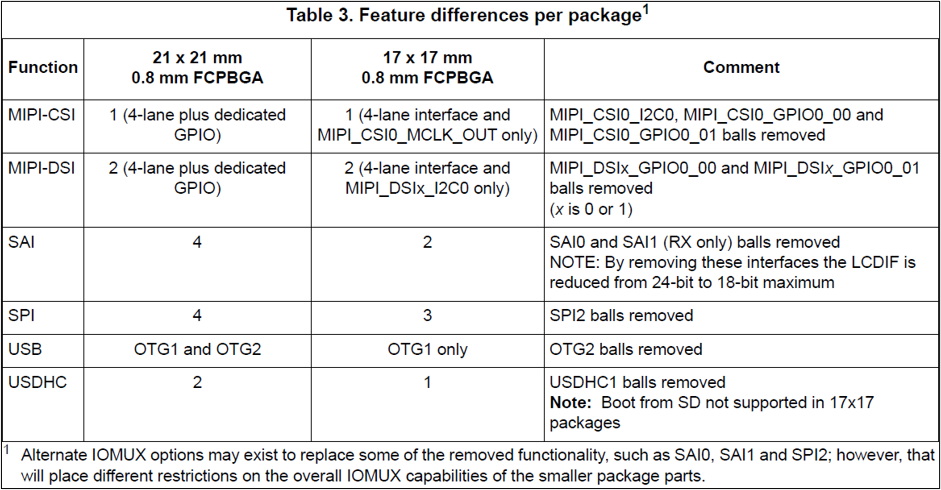

1. NXP i.MX8DX 平台,基于两个 Cortex-A35,一个 Cortex-M4F 架构。支持 16-bit LPDDR4 @1200MHz 或 16-bit DDR3L @933MHz。 有 21mm * 21mm 和 17mm*17mm 两种封装,两种封装功能上的差异参考下图:

▲ 图 1 i.MX8DX 不能封装的功能差异

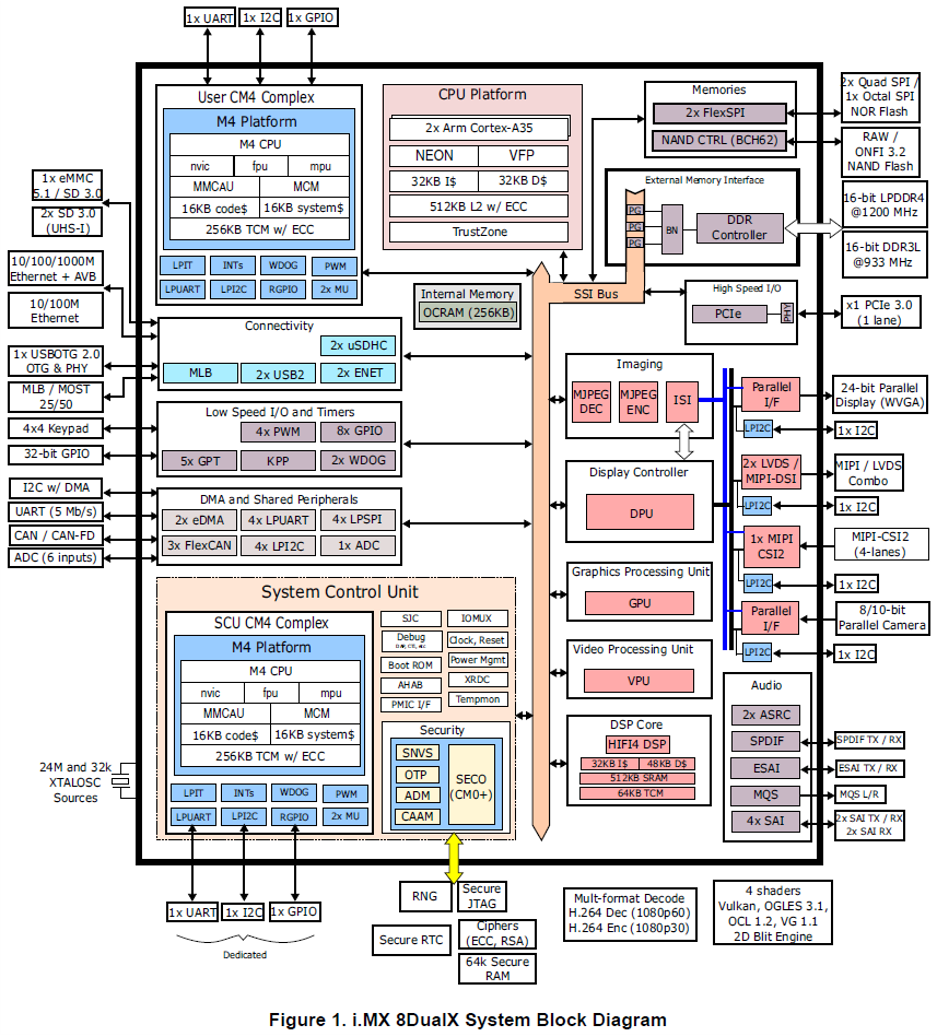

2. i.MX8DX 系统框图如下:

▲ 图 2 i.MX8DX 系统框图

3. i.MX8DX 支持 3.3V 及 1.8V 电平 GPIO,具体请参考 datasheet 和 EVB 原理图。

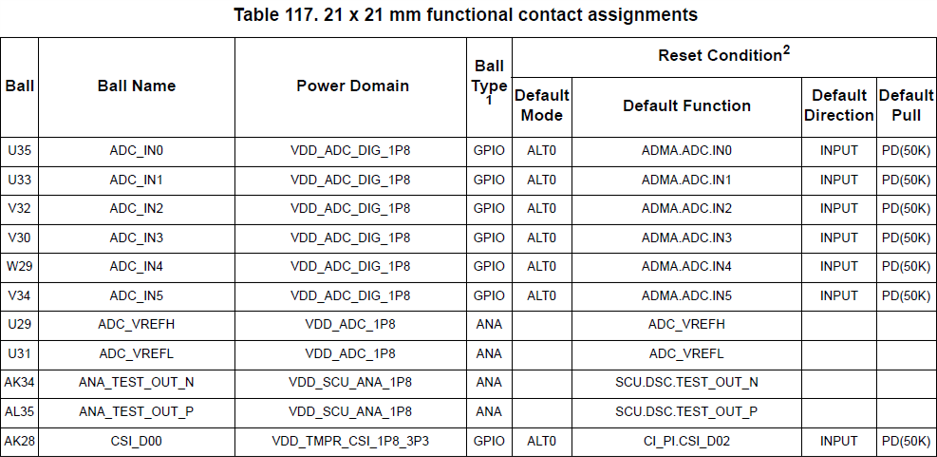

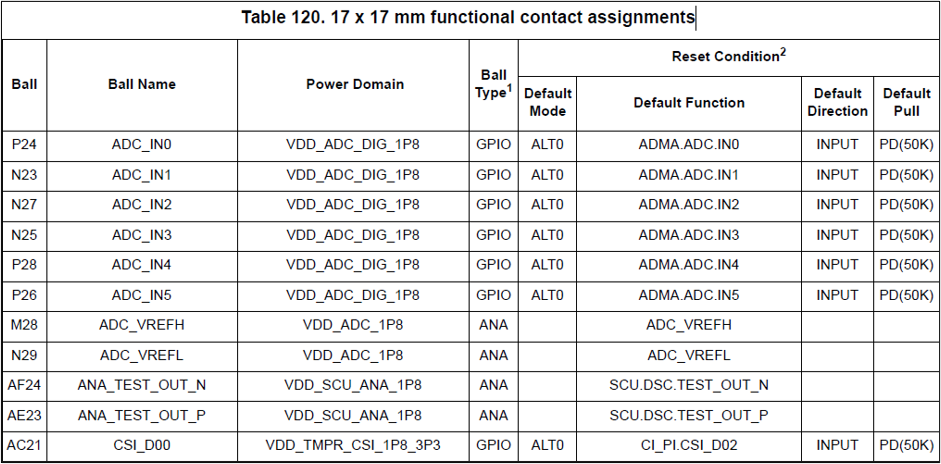

4. 不同封装的 i.MX8DX,GPIO 管脚功能请参考 datasheet,大部分与其他功能复用。

▲ 图 3 21mm*21mm 封装部分功能分配图

▲ 图 4 17mm*17mm 封装部分功能分配图

5. i.MX8DX 的 SPI 等专用中断口,建议不改变其原用途。

6. 普通的中断功能,如有使用 Cortex-M4F 功能,才可以使用 Cortex-M4F 中断接口。

▲ 图 5 Cortex-M4 中断接口

7. 普通中断功能,如果没有使用 Cortex-M4F 功能,只能使用 Cortex-A35 中断接口。

▲ 图 6 Cortex-A35 中断接口

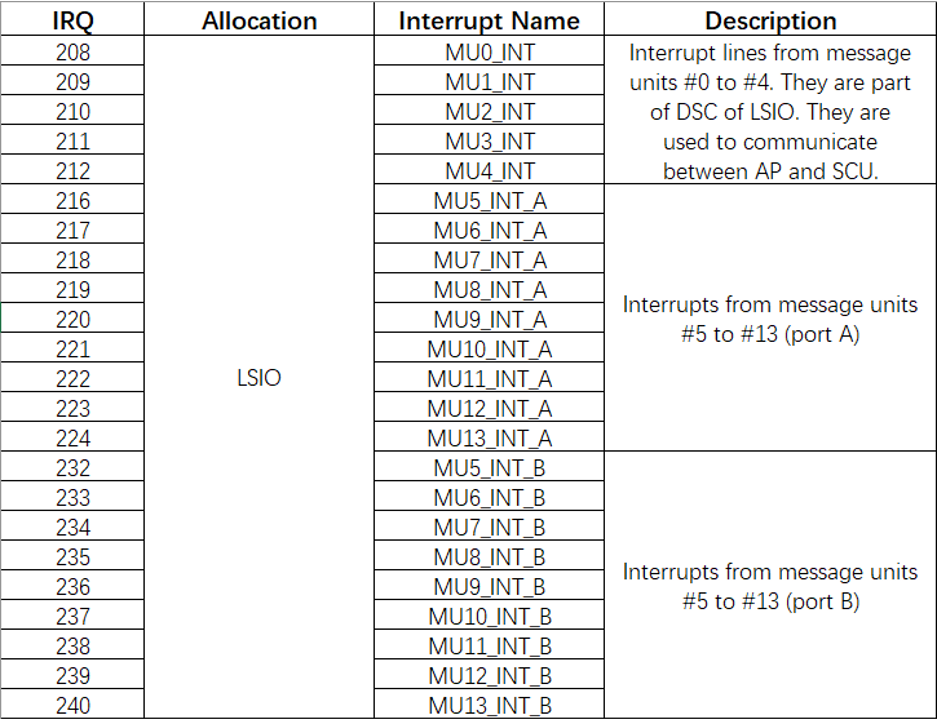

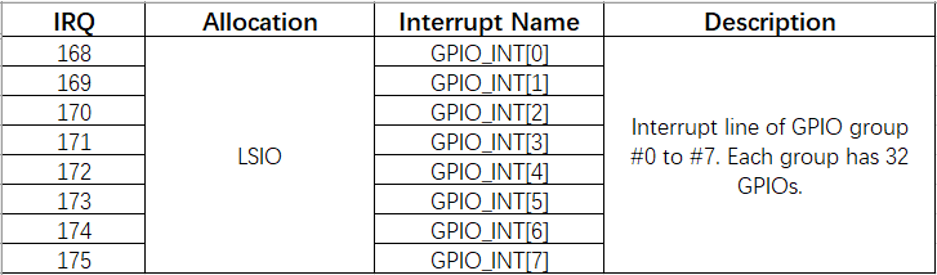

8. 一般,i.MX8DX 的 LSIO(Low Speed IO) 都可以作为普通中断功能使用,但是硬件设计时建议给我们软硬件一起确认比较稳妥。

9. 如需进一步的技术交流讨论,请在 大大通 上关注我,并给我留言。

二、参考文献

1.《 IMX8DXAEC.pdf 》

2.《 IMX8DQXPRM.pdf 》

评论