本文我们将探讨以下内容:

-

芯片片内防护能力与摩尔定律的关系

-

防护器件是否真的可有可无?

众所周知,IC(集成电路)的发展遵循着摩尔定律,已经持续了超过半个世纪。摩尔定律指的是:当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。这一定律揭示了信息技术进步的速度。 而如今,顶尖的光刻技术已能顺利实现5nm芯片的量产,未来还将朝着3nm,1nm甚至更小的线宽发展。 摩尔定律告诉我们,芯片行业要向前发展,必定要用到更小的线宽技术。而更小的线宽对于芯片来说,也暴露出一个致命的问题:ESD免疫力大幅下降。

线宽减小对片内ESD能力的影响 I

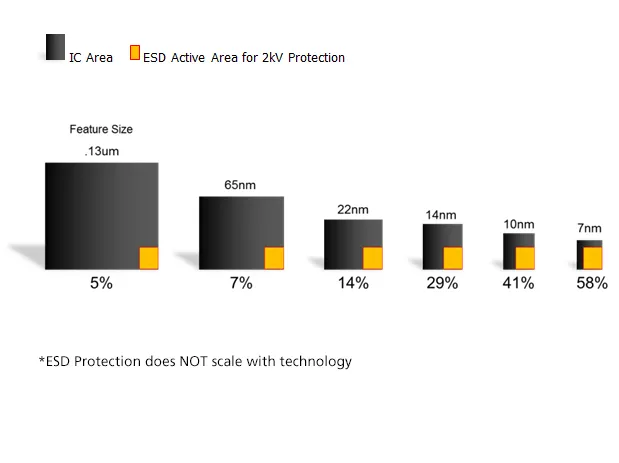

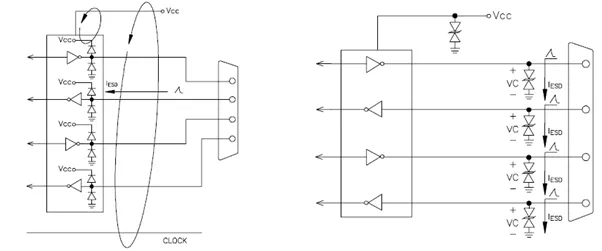

通过片内ESD的防护经验,我们知道,要想芯片达到同样等级的ESD防护能力,片内所需的单位防护面积是少不了的。随着芯片内部的线宽越来越小,要想实现同样HBM下,2KV的ESD能力,在0.13um制程下,只需占用5%的单位面积,而到了7nm制程下,会达到惊人的58%。这种情况对于任何厂家来说,成本上都难以接受。

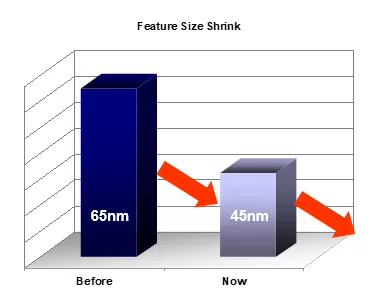

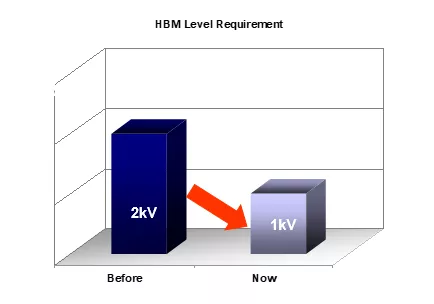

线宽减小对片内ESD能力的影响 II

评论