FS85 系列是 NXP 推出的功能安全系统基础芯片(Safety SBC),下面就来介绍下这款芯片及其在硬件设计上的注意点。

一、芯片介绍

1. 概述

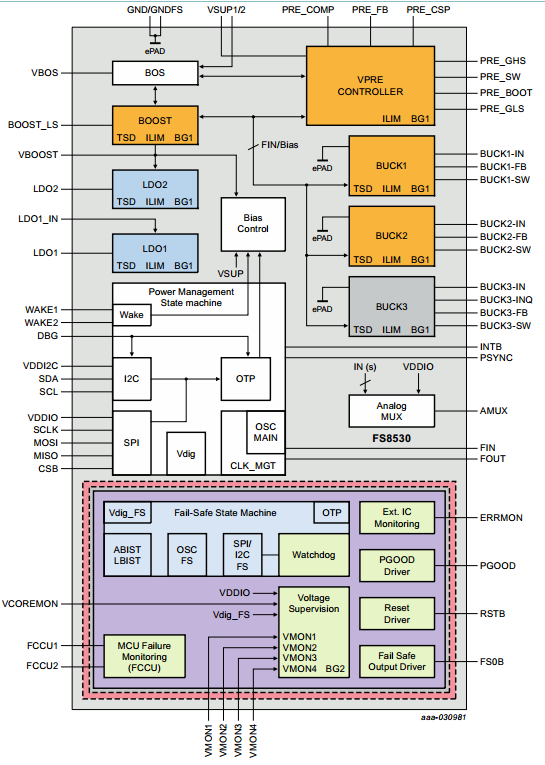

FS85/FS84 是一款汽车功能安全多输出电源集成电路,专注于雷达、视觉、ADAS 域控制器、无线电和信息娱乐应用。芯片包括多个开关模式和线性电压调整器,增强的安全功能和故障安全输出。这使得它完全成为一个面向安全系统的一部分,达到 ASIL D 安全完整性级别。(其中 FS84 系列是兼容于 FS85 系列的芯片,其安全等级为 ASIL B)。

主要性能特征如下:

- 最高 60 V 的输入电压适配汽车和卡车市场

- 多路 SMP 和 LDO 以提供给 S32 微控制器和其他更多需求

- 待机模式和睡眠电流非常低(10µA)

- 32 位 SPI 和 IDC 与 CRC 接口

- 适用于有独立安全监控装置的 ASIL D 系统设计

2. FS85 内部框图如下:

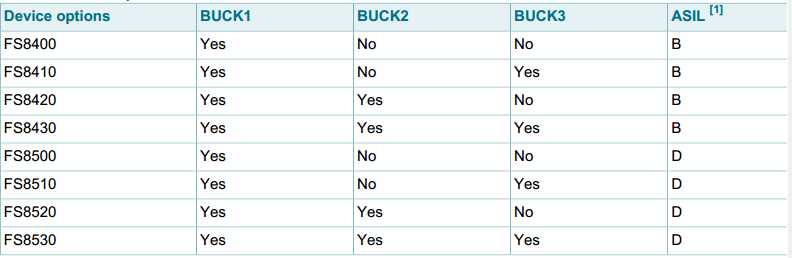

FS85/84 目前各包括 4 个型号,分别有不同的输出配置,这样的配置可以使其在不同应用选型更加的灵活,从而节省系统的总开支,其型号表如下图:

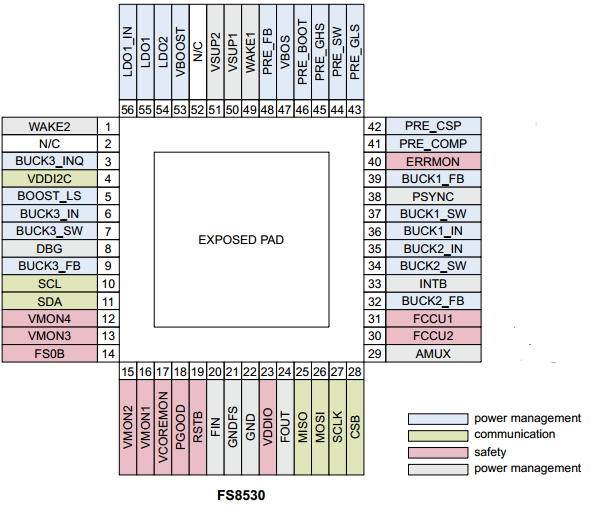

3. 封装及管脚介绍

PF85 封装为 HPQFN56(SOT684-23) 脚封装,其封装引脚分布图如下:

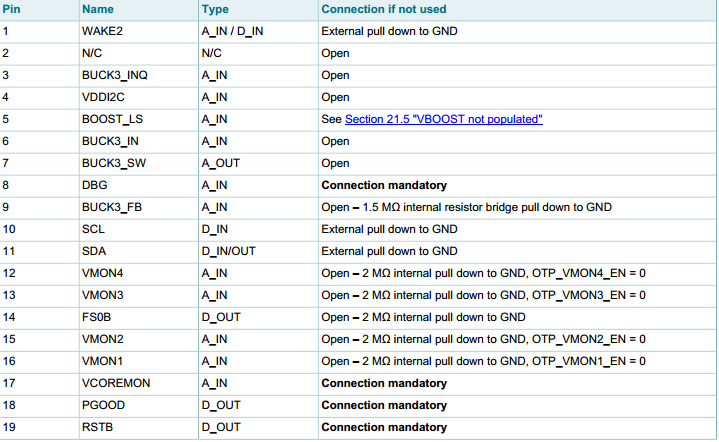

4. 没有使用的引脚处理方式:(由于引脚介绍较多,详细信息可以参考 DATASHEET 的第 8 小节 “Connection of unused pins”)

在设计的时候没有用的引脚一定要严格按照手册的描述来处理。如图所示:

二、硬件设计指南

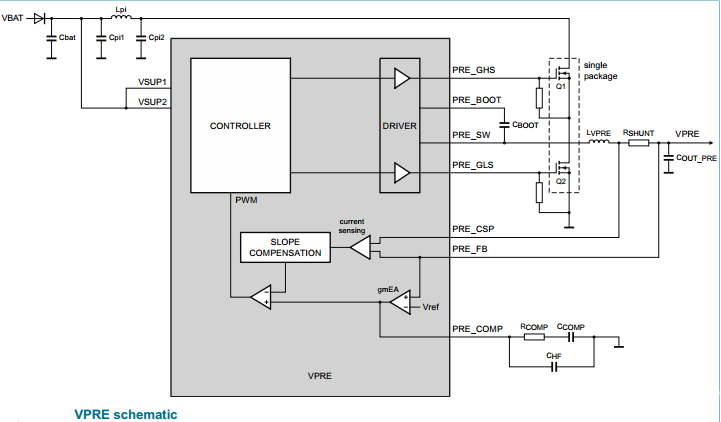

1. VPRE

VPRE 是一个高压,同步,峰值电流模式降压控制器。VPRE 工作在 force PWM 模式下,并使用外部 NMOS。其典型的应用框图如下图:

VPRE 的输出电压可通过 OTP 设定为 3.3 V 到 5.0 V,其工作频率是 455 kHz,输出电流最高达到 10A 的峰值。VPRE 同时也是 BOOST 、BUCK1/2 的输入源(也可以是 BUCK3 和 LDO1 的输入源)。

当使用两个 FS85/FS84 时,可能只需要一个 VPRE。可以不贴第二个 VPRE 的外部组件来优化材料清单。此时需要满足 VPRE2 特殊引脚的连接要求:

- PRE_FB2 必须连接到 PRE_FB1

- PRE_CSP2 必须连接到 PRE_FB1

- PRE_COMP2 必须保持打开状态

- PRE_SW2 必须连接到 GND

- PRE_BOOT2 必须连接到 VBOS2

- PRE_GHS2 和 PRE_GLS2 必须保持悬空

最后在启动阶段结束后,VPRE2 还需要通过 SPI/I2C 用 VPDIS 位进行禁用。

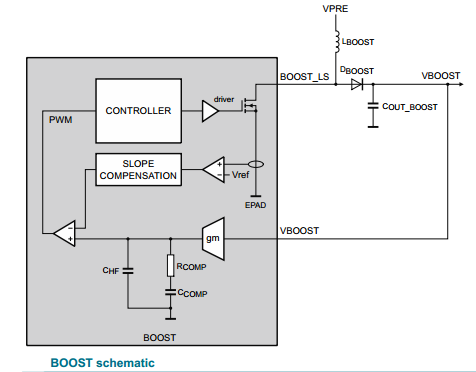

2. VBOOST

VBOOST 模块是一种低压、异步、峰值电流模式的升压变换器。VBOOST 工作在 PWM 模式下,使用外部二极管和内部低侧场效应管。VBOOST 的输入源必须连接到 VPRE 的输出端。

其典型的应用框图如下图:

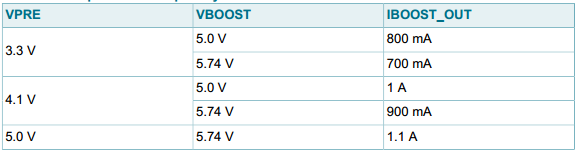

VBOOST 的输出电压可通过 OTP 设定为 5.0 V 到 5.74 V,其工作频率是 2.22 MHz,输出电流限制在 1.5 A 的峰值。具体对应不同 VPRE 的输出电流如下图:

当 VPRE 配置为 4.1 V 或 5.0 V 时,可以不使用 VBOOST。在这种情况下,可以不贴外部 VBOOST 组件来优化材料清单。OTP_BOOSTEN 位应编程为 0, VBOOST pin 必须连接到 VPRE。BOOST_LS 引脚必须保持悬空状态。

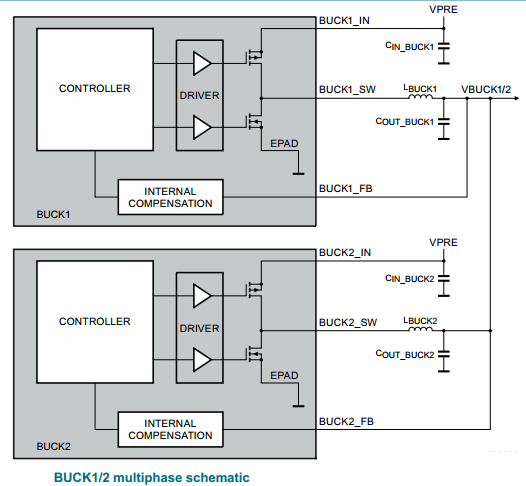

3. BUCK1 & 2

BUCK1 & 2 块是集成了 HS PMOS 和 LS NMOS 的低压、同步、谷电流模式 BUCK 变换器。BUCK1 & 2 工作在 PWM 模式下,输出电压可通过 OTP 设定为 0.8 V 到 1.8 V。其工作频率是 2.22 MHz,输出电流限制在 3.6 A 峰值。BUCK1 & 2 的输入源必须连接到 VPRE 的输出端。

BUCK1 & 2可以独立工作,也可以在双相模式下工作,使输出电流能力提高一倍。

当 BUCK1 & 2 工作于双相模式时,它们必须具有相同的输出电压配置。任何动作如 TSD, OV, 通过 SPI/I2C 在 BUCK1 上禁用会影响到 BUCK2,反之亦然。

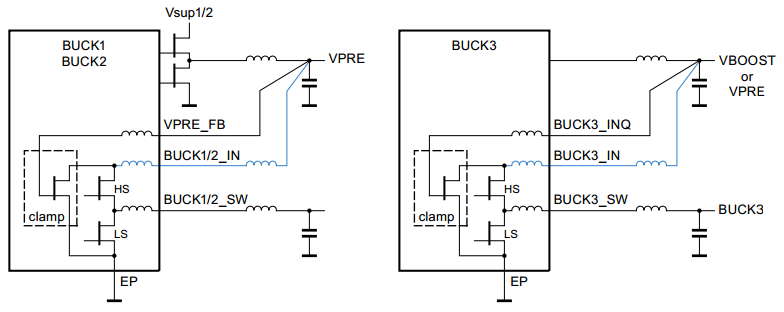

其典型的应用框图如下图(双相模式):

使用 OTP_VB12MULTIPH 位启用双相模式。为了获得最佳的 EMC 性能,BUCK1 和 BUCK2 的 PCB 布局必须是对称的。

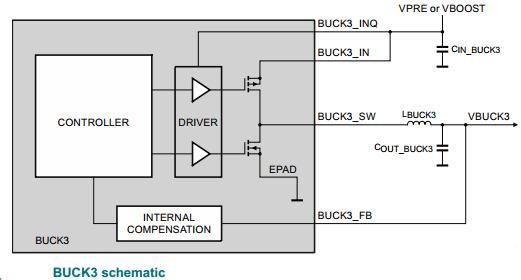

4. BUCK3

BUCK3 是集成了 HS PMOS 和 LS NMOS 的低压、同步、谷电流模式 BUCK 变换器。BUCK1 & 2 工作在 PWM 模式下,输出电压可通过 OTP 设定为 1.0 V 到 3.3 V。其工作频率是 2.22 MHz,输出电流限制在3.6 A 峰值。BUCK3 的输入源可以连接到 VPRE 或 VBOOST 的输出端。

其典型的应用框图如下图:

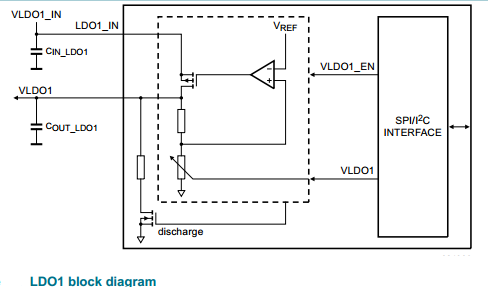

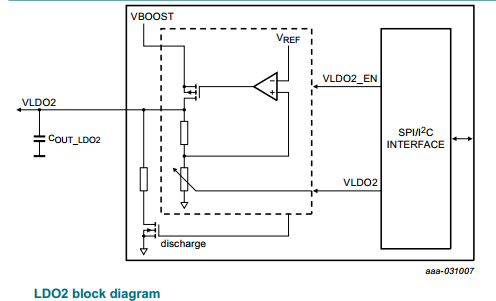

5. LDO1 & 2

LDO1 & 2 是两个线性稳压器。输出电压可通过 OTP 设定为 1.1 V 到 5.0 V。其电流输出能力由其最小压降决定(150mA 为 0.5 V, 400mA 为 1.0 V)。

LDO1 输入电源从外部连接到 VPRE、VBOOST 或其他电源。LDO2 输入电源内部连接到 VBOOST 的输出。其典型的应用框图如下图:

6. I/O 接口

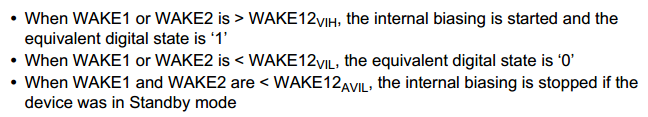

6.1 WAKE1 & 2

WAKE 引脚用于管理设备的内部偏置和主状态机的转换。具体转换条件如下图:

WAKE1 & 2 是基于电平的唤醒输入信号,具有通过 AMUX 进行模拟测量的能力。例如,

WAKE1 可以连接到 VBAT, WAKE2 则可以连接到 CAN 或 FlexRay 收发器的唤醒输出。

6.2 INTB

INTB 是一个开漏输出引脚,其内部上拉到 VDDIO。当一个内部中断发生时,这个引脚产生一个脉冲来通知单片机。通过在 M_INT_MASK 寄存器中设置相应的禁止中断位,可以屏蔽每个中断。

6.3 PSYNC

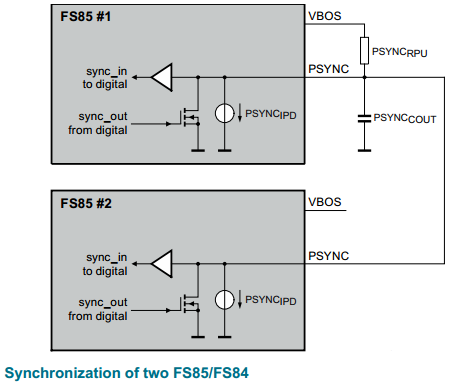

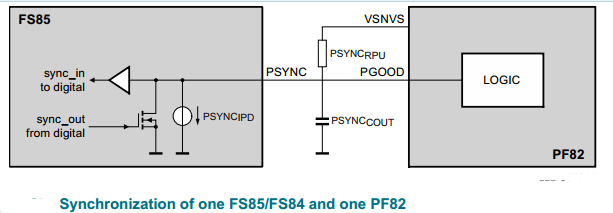

PSYNC 功能允许使用多个电源管理 IC 来管理复杂的启动序列,比如两个 FS85/FS84(OTP_PSYNC_CFG = 0)或一个 FS85/FS84 加上一个 PF82 (OTP_PSYNC_CFG = 1)。

当使用 PSYNC 同步两个 FS85/FS84 时,每个设备的 PSYNC 引脚应连接在一起,并上拉到 FS85/FS84 主设备的 VBOS 引脚,在此配置中,FS85#1 状态机将在 FS85#1_VPRE 启动前停止并等待 FS85#2 来同步 FS85#2_VPRE 启动,如图所示:

当使用 PSYNC 同步一个 FS85/FS84 和一个 PF82 时,FS85/FS84 的 PSYNC 引脚应与 PF82 的 PGOOD 引脚连接,并可上拉至 PF82 的 VSNS 引脚。在这个配置中,FS85 状态机在 VPRE 启动之后停止,并等待PF82_PGOOD 释放后继续它自己的上电时序。它允许同步两个设备各自的电源启动顺序。在断电过程中,FS85 应等待 PF82 断电程序完成后再关闭 VPRE (VPRE 正在为 PF82 供电)。OTP_VPRE_off_dly bit 应将修改其配置,从默认的 250μs 修改为 32ms。如图所示:

7. PGOOD & RSTB

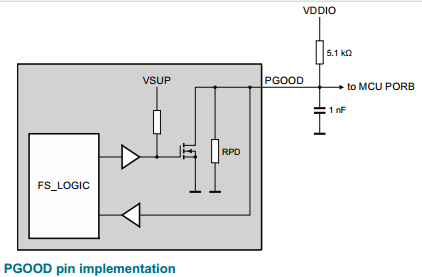

PGOOD 是一个开漏的输出,用于连接到 MCU 的 PORB。PGOOD 需要一个外部上拉电阻到 VDDIO 以及一个滤波电容到 GND 以防止干扰造成误动作。参考下图:

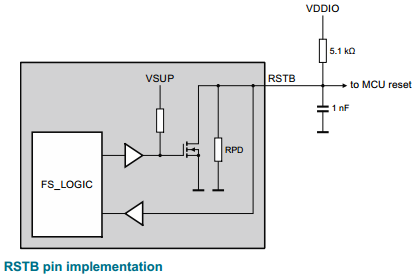

RSTB 是一个开漏的输出,用于连接到 MCU 的 RESET。RESTB 需要一个外部上拉电阻到 VDDIO 以及一个滤波电容到 GND 以防止干扰造成误动作。参考下图:

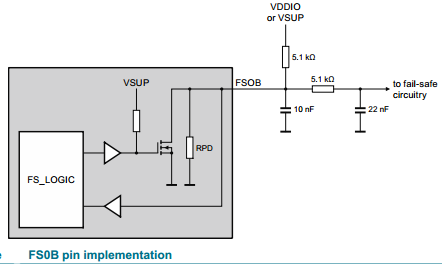

8. FS0B

FS0B 是一个开漏的输出,用于向系统发出安全状态。FS0B 需要一个外部上拉电阻到 VDDIO 或者 VSUP,FS0B 需要一个 10 nF 的滤波电容到 GND 或者一个 RC 滤波网络当其分别使用在局部或者整个全局系统中以防止干扰造成误动作。参考下图:

三、 LAYOUT 指南

1. 器件选型

- SMPS 输入和输出电容器应选用低 ESR (陶瓷或 MLCC 类型的电容器)。最好是 X7R 陶瓷型。输入去耦电容器应尽可能靠近设备引脚。输出电容额定电压应选择为 3 倍的电压输出值,以尽量减少直流偏差退化。

- SMPS 电感器应采用 ISAT 值高于最大电感器峰值电流的屏蔽型电感。

2. VPRE

- 电感器充放电电流回路的设计应尽可能靠近。

- 输入去耦电容应放置在靠近高侧晶体管的漏极引脚的位置。

- Boot strap 电容器应放置在靠近器件的引脚端,并且使用宽而短的走线连接到外部低侧晶体管的漏极引脚。

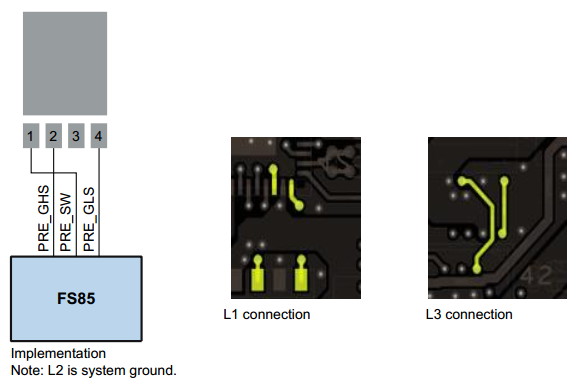

- PRE_GLS、PRE_GHS 和 PRE_SW 走线应宽而短,不应跨越任何敏感信号(例如电流检测信号)。如图所示:

- PRE_FB 作为电压反馈和电流检测信号,应连接在 VPRE 输出电容上,并与 CSP 成对走线,这样可以减少干扰从而提高输出精度。

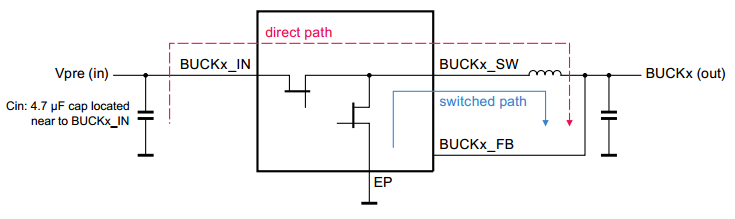

3. VBUCKx

- 电感器充放电电流回路的设计应尽可能靠近。如图所示:

- 输入去耦电容应放置在接近 BUCKx_IN 引脚的位置。

- BUCK3_FB 和 BUCK3_INQ 引脚应连接在同一电容器上,BUCK3_IN 的的输入源是谁决定了 VPRE 或 VBOOST 输出电容的选型(在下面的蓝色路径中,线圈电感是寄生于走线的。在封装中,线圈是寄生于 bonding。)如图所示:

以上就是本文的全部内容,后续我们将会推出更多关于 ADAS 域控制器的硬件设计类的文章,有喜欢的,欢迎关注我并收藏~

【参考资料】:

FS85 参考手册:《FS8400 and FS8500 Fail-safe system basis chip with multiple SMPS and LDO - data sheet V3.0》

评论