通过前面几篇博文我们了解到了一个伺服驱动系统的主要架构(伺服驱动器 、电机、编码器)。在伺服系统中,通常使用从外部到内部嵌套的三闭环控制方案来实现永磁同步电动机的位置、速度和电流的反馈控制。这种控制结构就决定了处于三环最内部的电流环的计算速度制约着整个伺服系统的计算速度,只有首先保证电流环路的计算周期短、带宽大,才能设计出高性能的伺服系统。速度控制和位置控制也是工业控制上最常用的两种控制模式,高性能速度环路和位置环路是保证转子速度的快速跟踪以及伺服系统精确定位的前提。

我们先来看看当前一些不同的伺服驱动架构:

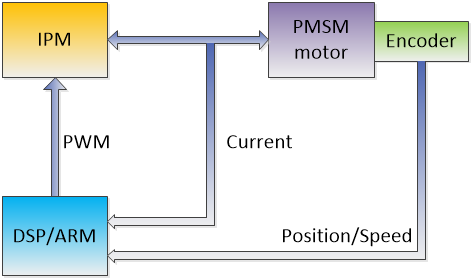

单芯片控制架构:

DSP/ARM 通过编码器采集电机速度、位置信息,同时进行电流环、速度环、位置环的处理。这种架构受 DSP/ARM 的外设及性能影响,控制所达到的精度有限。

Single processor control

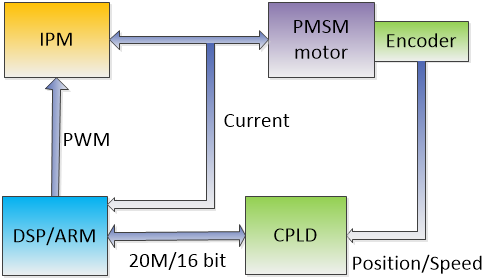

DSP/ARM + CPLD 架构:

CPLD 采集电机的位置、速度等信息并将数据传送给 DSP/ARM,DSP/ARM 根据接收的数据及控制命令进行电流环、速度环以及位置环的处理。这种架构就减小了 DSP/ARM 的负载,使其能将更多的资源用来运行算法控制电流环、速度环、位置环。同时又因为 DSP/ARM 的 PWM 精度有限,在电机控制过程可能没有那么的平滑。

Soft current loop control

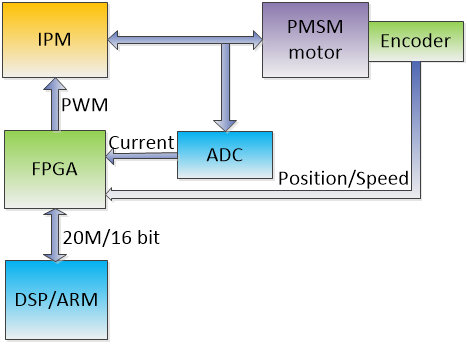

DSP/ARM + FPGA 架构:

由 FPGA 处理电流环,并与编码器通信,同时根据 DSP/ARM 的指令要求进行 PWM 分频输出控制 IPM。DSP/ARM 则大大减轻了负载,可以用更多的资源进行滤波处理,并控制速度环 & 位置环。

这种架构下同时会外挂一个 16bit ΣΔ ADC 进行电流采样,而 FPGA 的 PWM 分频同样可以做到更到的精度,因此整个系统的控制精度及平滑度都提升了一个等级。

Hardware current loop control

随着智能制造的不断升级,运动控制系统担任着越来越重要的角色,其系统也越来越复杂。伺服驱动的控制端需要实时处理,并且快速更新采集的电流数据,与此同时还要进行复杂的算法处理。在不增加太多成本的情况下,很难在一个处理器中实现这些功能。不过通过使用 FPGA,时间紧迫的电流控制执行是通过硬件而不是软件来实现的,因此延迟和执行时间是固定的,并且快速而又稳定。

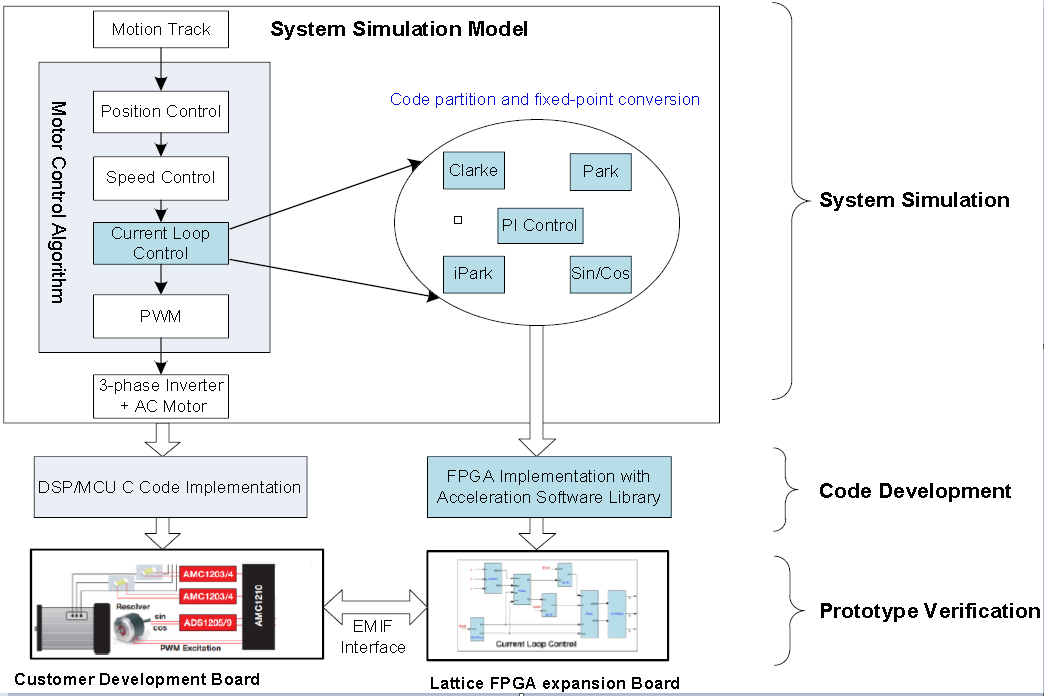

使用 DSP/ARM + FPGA 架构的控制流程:

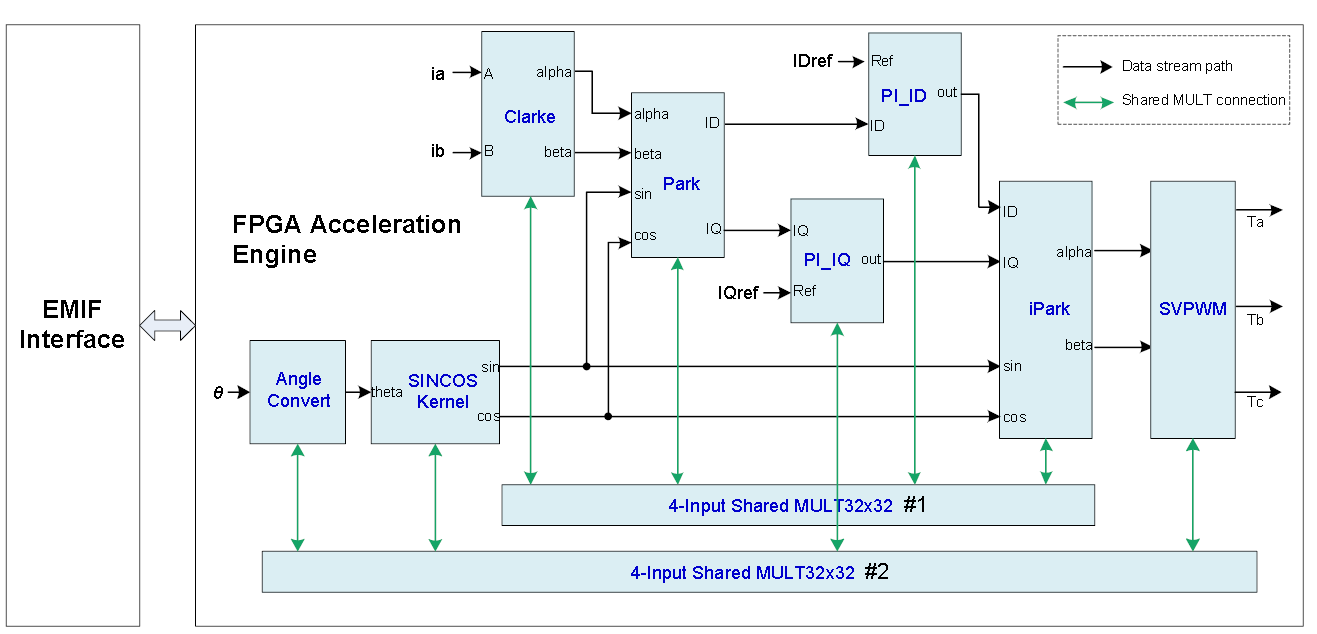

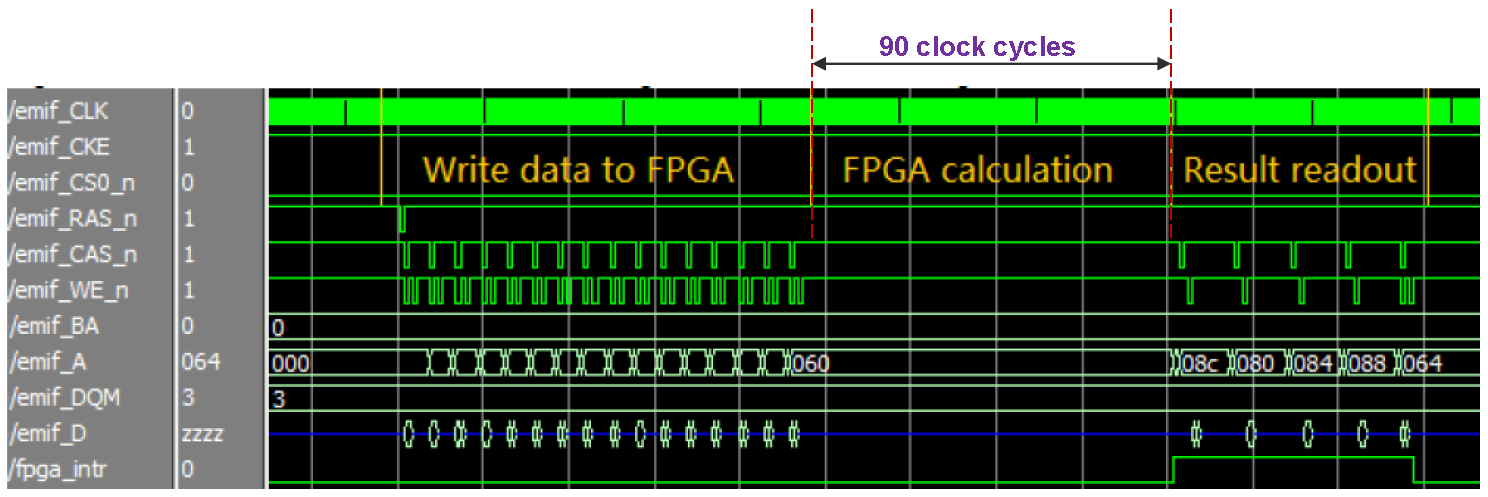

电流环运算的参考设计及时序如下所示:

1us 内完成电流环的计算

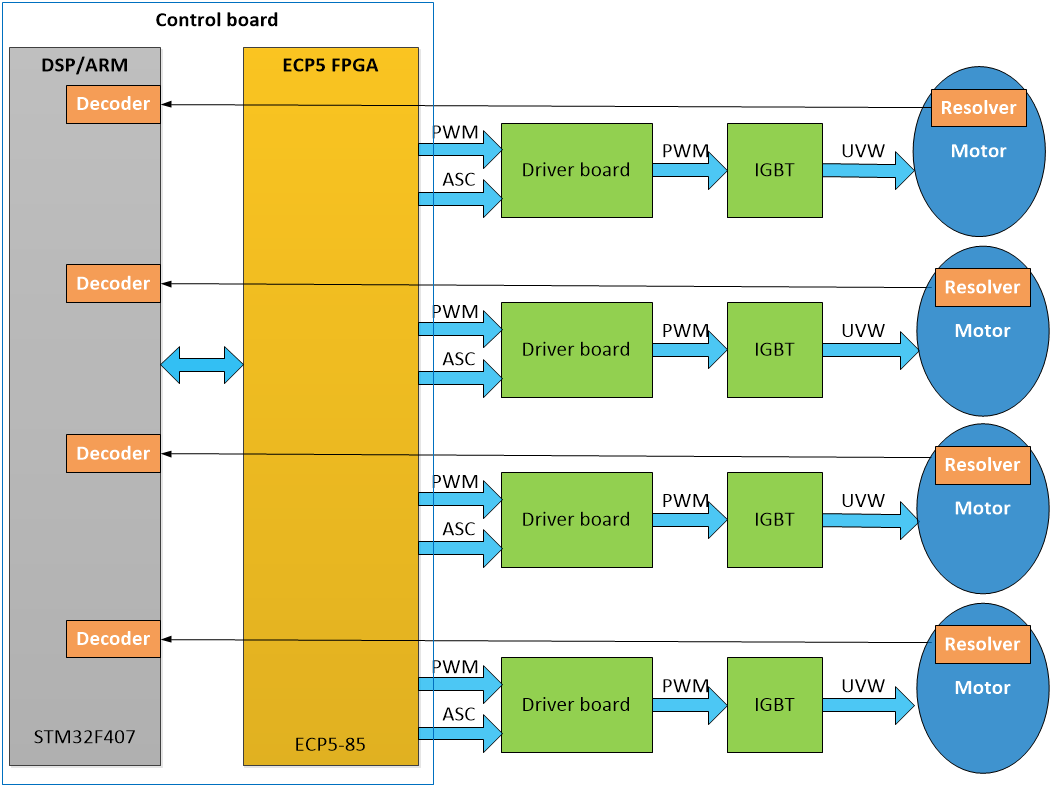

另外在进行多轴控制时,FPGA 的硬件特性及可编程特性使得能我们快速进行功能扩展,从而实现在不同轴电机之间的便捷同步,同时大大降低 DSP/ARM 的负载。

使用 FPGA 进行多轴控制

参考资料:

- 百度文库;

- 电子发烧友;

- Lattice 官网;

- 中国产业信息网;

评论