TJA1102(S)是 NXP 推出的一款高度集成的双(单)端口、兼容 IEEE 100BASE-T1 的车载以太网 PHY。下面就来介绍下 TJA1102 的特点及其在硬件设计上的注意点。

1.1 芯片介绍

1.1 概述

TJA1102(S)是一个高度集成的双端口(S 为单端口),兼容 IEEE 100BASE-T1 以太网物理层收发器。针对汽车用例进行了优化,如网关、IP 摄像机链路、驾驶员辅助系统和骨干网络。该设备通过两条未屏蔽的双绞线可以提供 100Mbit/s 的收发能力,支持至少 15 米长的电缆。

1.2 基本特征

① 车规等级

● AEC-Q100 Grade 1

● 环境温度 -40°C to 125°C

② 兼容 IEEE 100BASE-T1

● 可与任何符合 IEEE 100BASE-T1 和 OABR 的 PHY 互联

● 100Mbps 以太网基于单对未屏蔽双绞线(UTP)电缆

● 单端口和双端口版本引脚兼容

③ 兼容 OPEN Alliance TC-10 的睡眠及唤醒

● 完全集成在 PHY 中,独立于主机控制器

● 通过数据线唤醒,节省额外的唤醒线

● 降低电缆成本和重量

④ 针对汽车用例进行了优化

● MDI 引脚不需要额外的滤波或 ESD 保护

● 电缆极性检测和校正

● 支持单电源3V 供电

● 与电池 Vbat 直连

⑤ 高级诊断功能

● 实时信号质量指示器

● 无间隙欠压检测

● 电缆故障诊断

1.3 封装及引脚信息

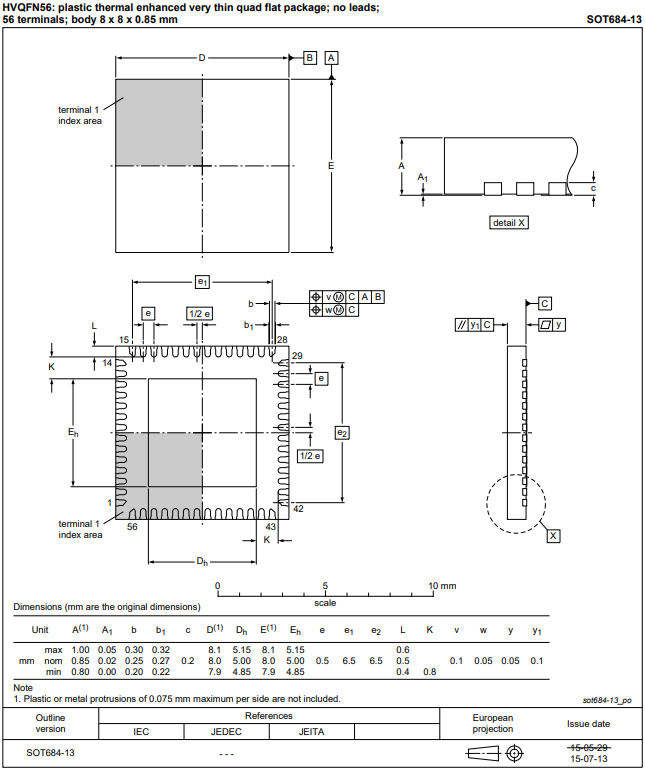

① 封装:TJA1102 系列封装均为 HVQFN56(SOT684-13),具体封装参数如图:

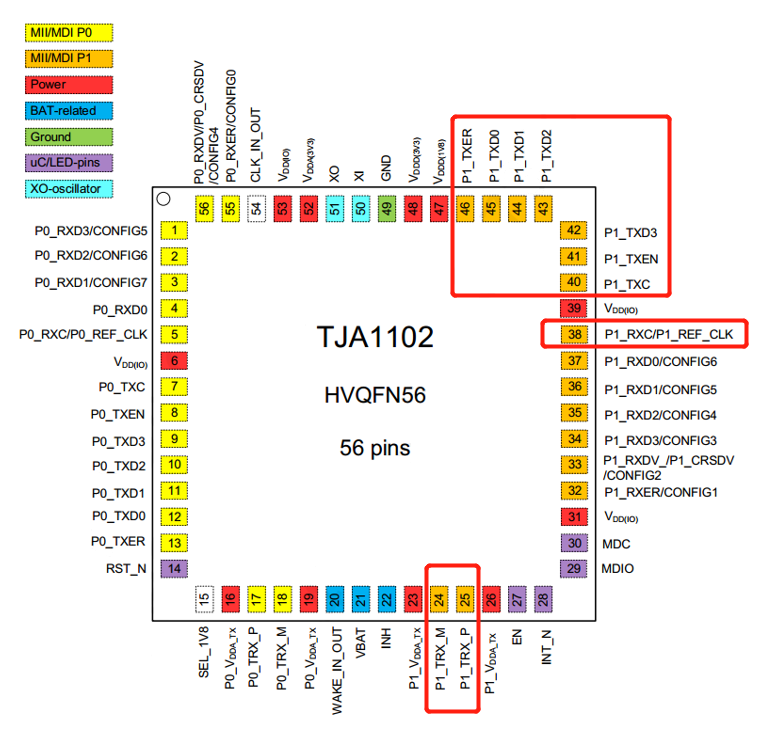

② 引脚定义(TJA1102 双/单端口版本封装引脚兼容):

如上图所示,TJA1102S 版本为单端口,P1 口除复用配置引脚外其余引脚全部为 NC(红框部分引脚),除此之外两个版本在硬件及软件上完全兼容,提高了设计的灵活性。

2. 硬件设计指南

2.1 电源设计

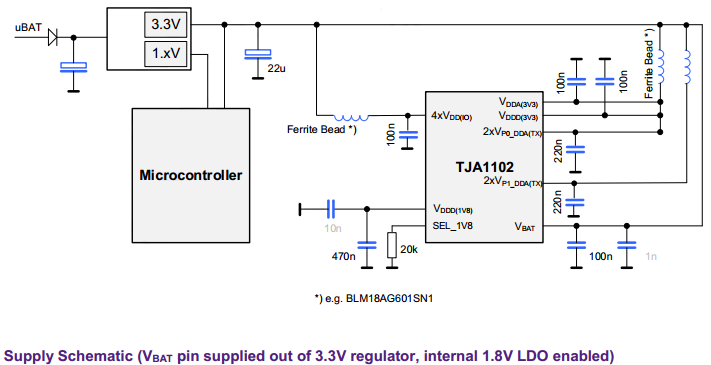

TJA1102 的 VDDD(1V8)可以选择由内部稳压器或者外部提供,通过“SEL_1V8”引脚来配置:高电平为外部 1.8V LDO,低电平为内部 1.8V LDO。

具体电源参考设计如下图:

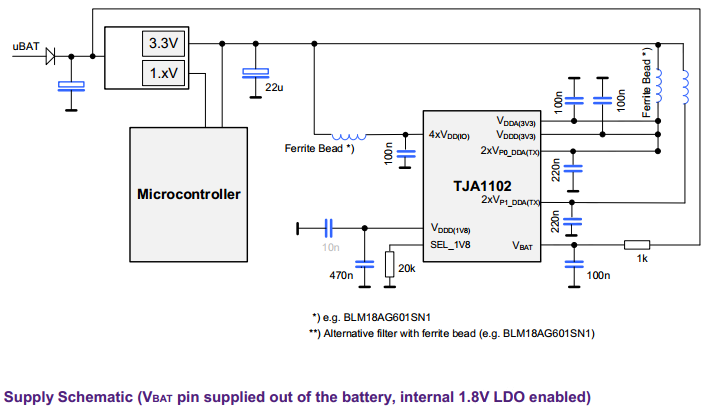

注意:上图中 VBAT 接到了 3.3V,VBAT 也可以由电池直接提供,主要用于支持唤醒。建议在 PHY 的电池供电线路上放置一个 1k 欧姆的串联电阻,以增强对汽车瞬变的保护。此外,增加 100nF 的电容与串联电阻形成低通滤波器,可用于增强瞬态保护。

具体电路如下图所示:

2.2 接口设计

① MII/RMII 接口

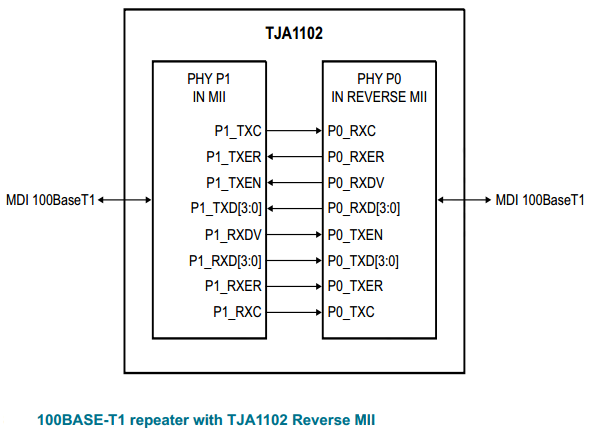

TJA1102 增加了内部 Reverse MII 功能,这样 TJA1102 可以作为一个 100Base-T1 中继芯片。

② SMI 接口

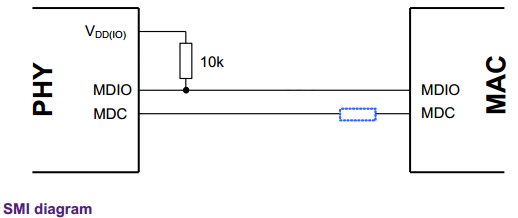

SMI 接口由两个信号实现:

● MDC(数据时钟):由 MAC 驱动并提供给 PHY。MDC 的最高时钟频率为 5MHz,对应的最小时钟周期为 400ns。

● MDIO(数据输入/输出):双向,写的时候由 MAC 来驱动。而读的时候则由 PHY 来接管,在周转比特时,提供 MAC 要求的数据,然后释放 MDIO 线。

为了进一步实现 EMC 微调,可以考虑在 MDC 信号线上(预留)增加一个大约 50 欧姆的串联电阻。MDIO 需要一个特定的上拉电阻(约 10 K)至 VDDIO(上拉电阻可以由 MAC 端提供),确保上拉电阻在同组 MDIO 上只有一个。

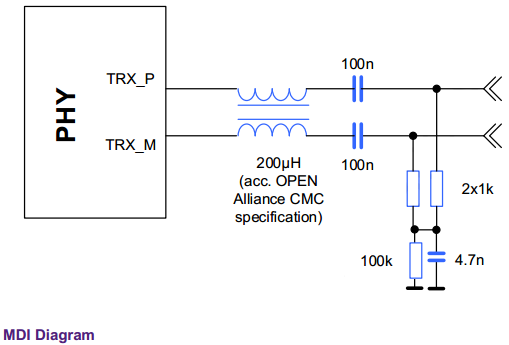

MID 接口参考设计如下图(TJA1102 不需要外部低通滤波,因为有效的低通滤波已经集成到 PHY 中):

TJA1102 芯片内部提供了 ±6kV 的 ESD 保护,如果想要提高等级的话,可以在接口外部增加 ESD 保护器件。

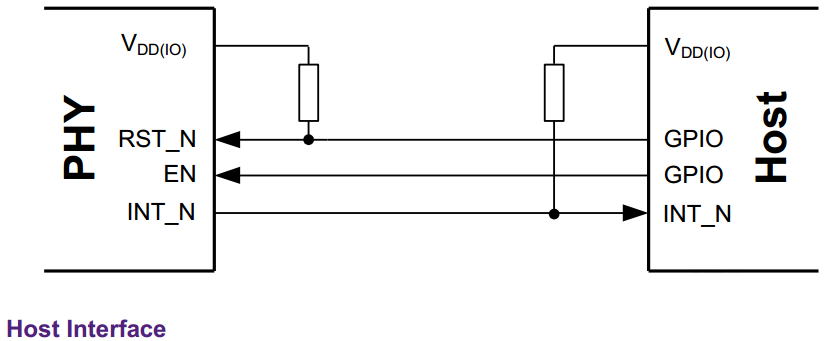

④ 主机接口(RST_N,INT_N,EN)

RST_N 和 EN 是 PHY 的输入信号,通常由微控制器的 GPIO 引脚驱动,INT_N 则为输出信号至微控制器。

INT_N 是集电极开路输出(需要 10K 上拉电阻),允许多个 PHY 同时挂在一个中断输出只微控制器,如图所示:

⑤ WAKE_IN_OUT 引脚

WAKE_IN_OUT 引脚是双向的,可以作为本地唤醒的 Input,也可以作为唤醒 output(当 Cable 上有以太网数据唤醒 TJA1102 时)。芯片是否会响应远程/本地唤醒,以及唤醒的脉冲宽度都是可配置的。

注意:只有上升沿才会触发本地唤醒!

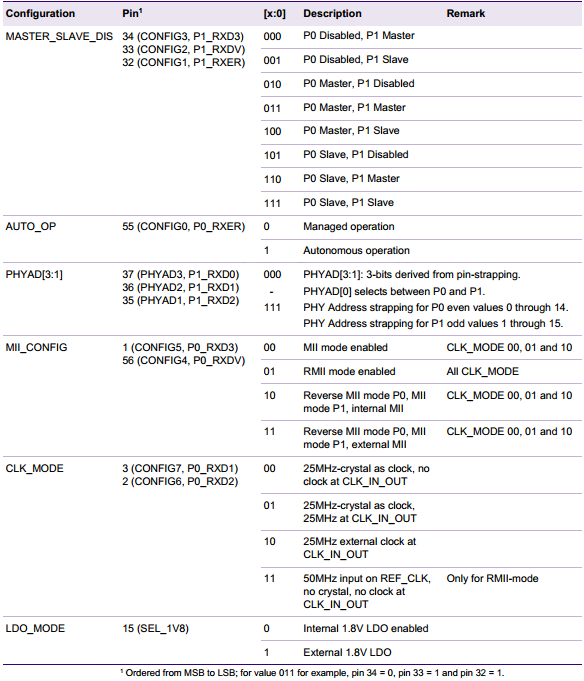

⑥ 配置引脚

TJA1102 在上电时通过读取 #32、#33、#34、#55、#35、#36、#37、#56、#1、#2、#3 和 #15 的引脚电平状态决定其对应的模式(上拉为逻辑“1”,下拉为逻辑“0”。上/下拉电阻的值应该在 5k~20kOhm 之间),具体配置如图所示:

上电进入“Standby”模式后,引脚配置读取完毕,重启时则会重新读取引脚状态。默认的引脚配置也可以通过 SMI 接口的命令进行改动(PHY 的地址除外)。

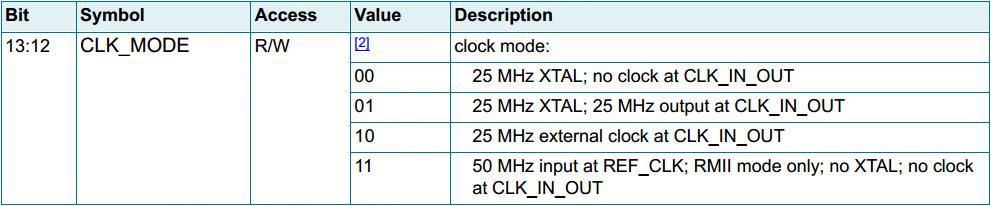

2.3 时钟设计

TJA1102 可以配置多种 Clock 模式,增加了 CLK_IN_OUT(Pin 54),可以接受外部 25MHz 单端时钟输入,也可以输出单端 25MHz 时钟,具体配置如图所示:

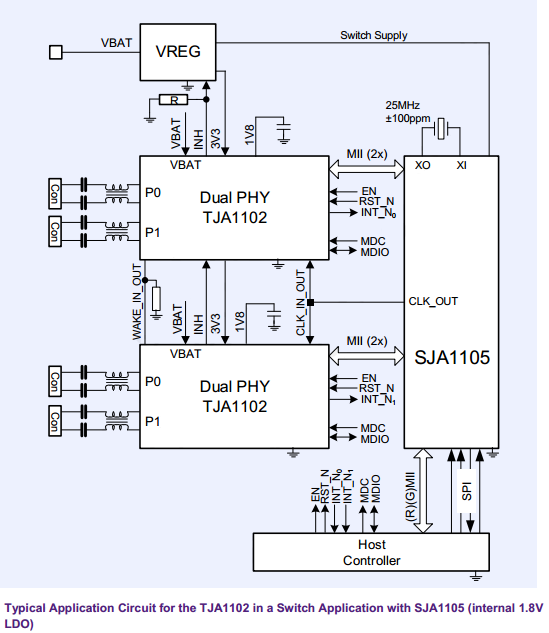

2.4 参考设计

如下图所示为两颗 TJA1102 与一颗 SJA1105P/Q 通过 MII 连接的系统示意图,其中主控与 SJA1105P/Q 通过 RGMII 接口连接。

为了与 TJA1102 兼容,SJA1105 必须选择 3.3 V 的 VDDIO_MIIx 电源。其他接口的电源则根据主控系统电平决定对应的电压大小。

2.5 PCB Layout 指导

① MDI 接口: 100 ohm +/- 10% 差分阻抗,所有器件对称放置,Common mode choke 之前的所有器件靠近芯片侧放置。对内保证等长(10 mil 之内)

② MII 接口: 50 ohm +/- 10% 单端阻抗,串阻靠近信号发送端放置。

同组信号内保持等长(50 mil 之内),例如 RX data 和 RX clk。

③ 建议对时钟和数据信号使用埋地或包地处理,以减少辐射指标。

④ 尽量减小寄生电感和电阻:

● 减少去耦电容的电源与地脚之间的痕迹长度;

● 增加导线宽度;

● 小电容尽量靠近芯片引脚,因为谐振频率高的小电容更容易受到寄生电感和电阻的影响。

3. 参考文档

① TJA1102 Datasheet:《TJA1102 100BASE-T1 dual/single PHY for automotive Ethernet (REV 1.0)》

② TJA1102 Application hints:《AH1508 - TJA1102 Automotive Dual-port Ethernet PHY》

评论