一、原理图部分

1. NXP S32V234 平台最小系统(CPU + DDR + Flash + Reset + Power)电源介绍

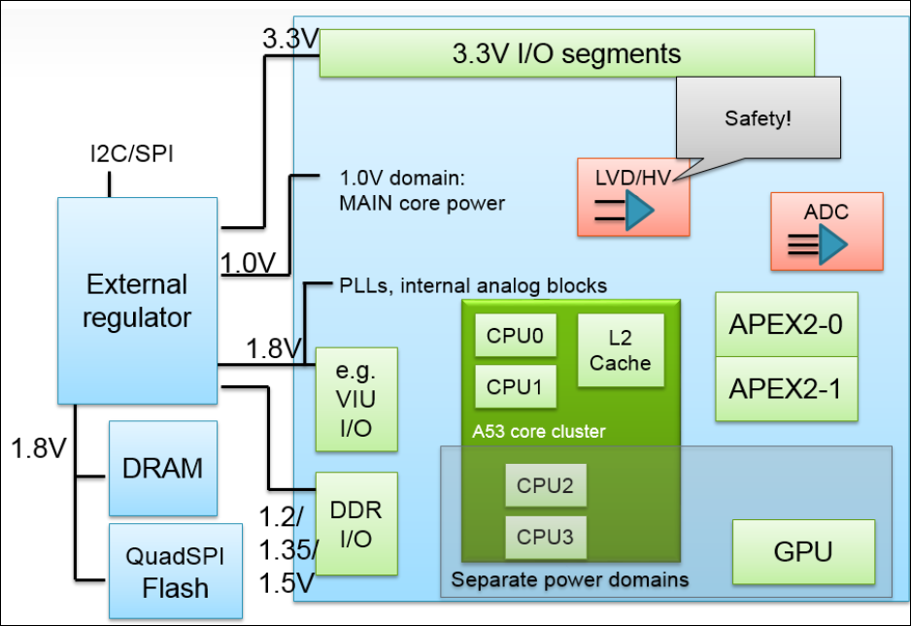

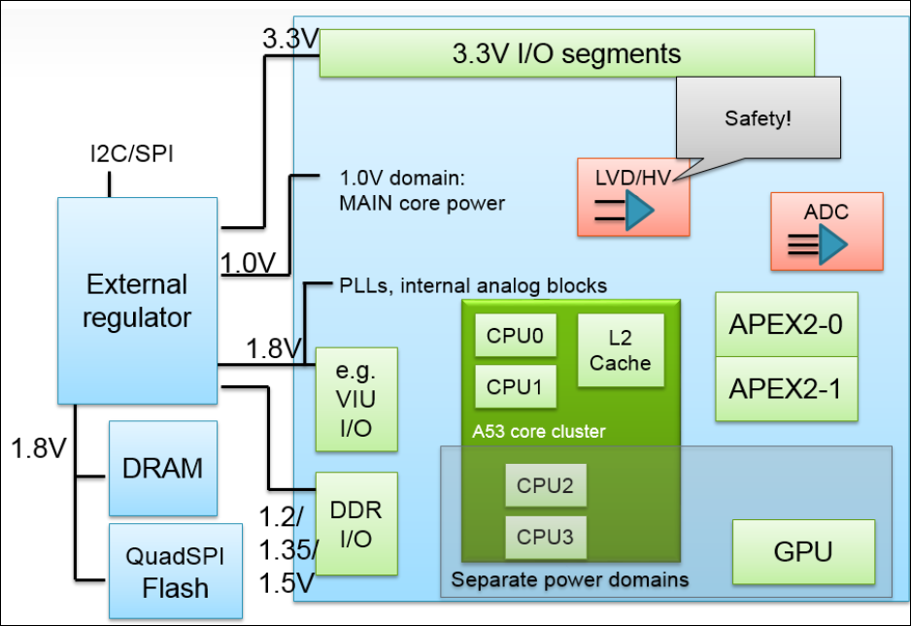

1.1 S32V234 最小系统电源框图

图 1.1 S32V234 Power supply concept

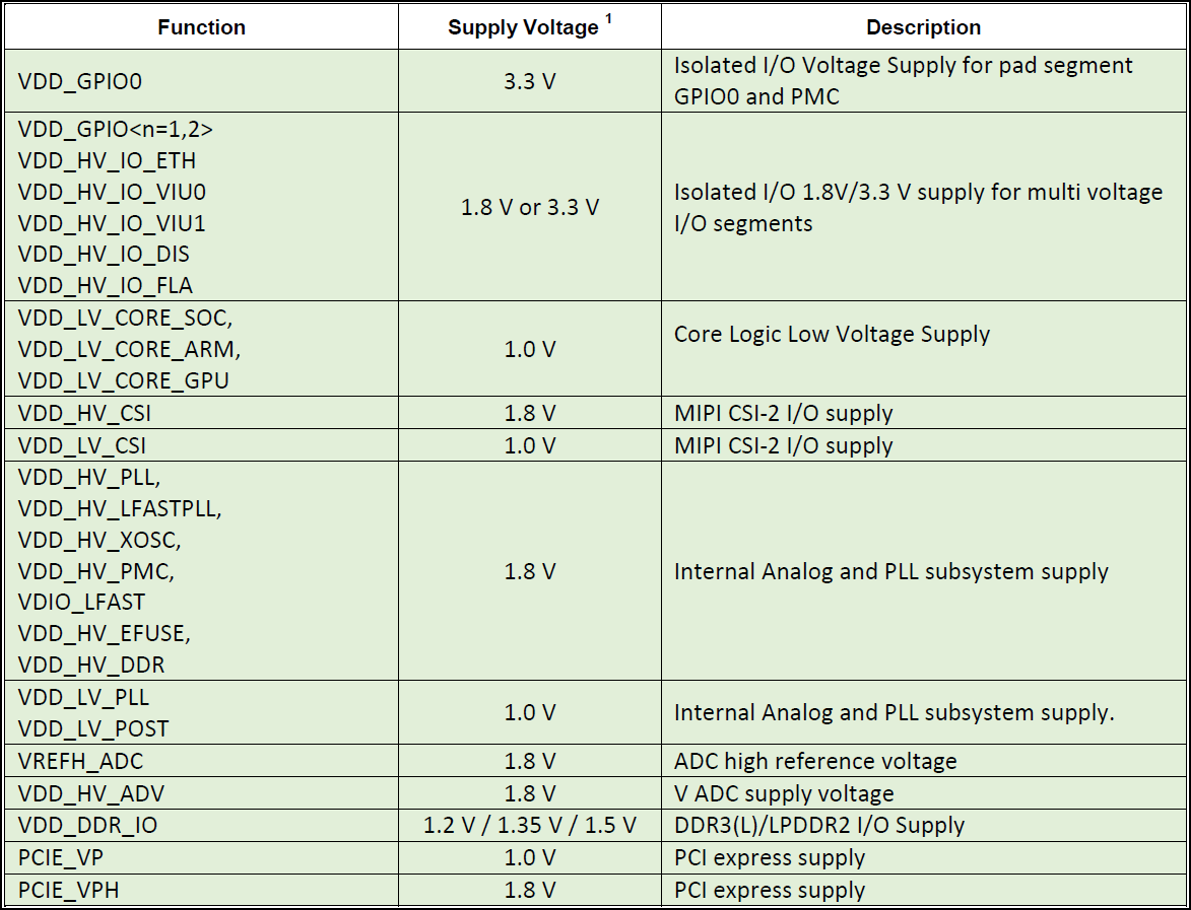

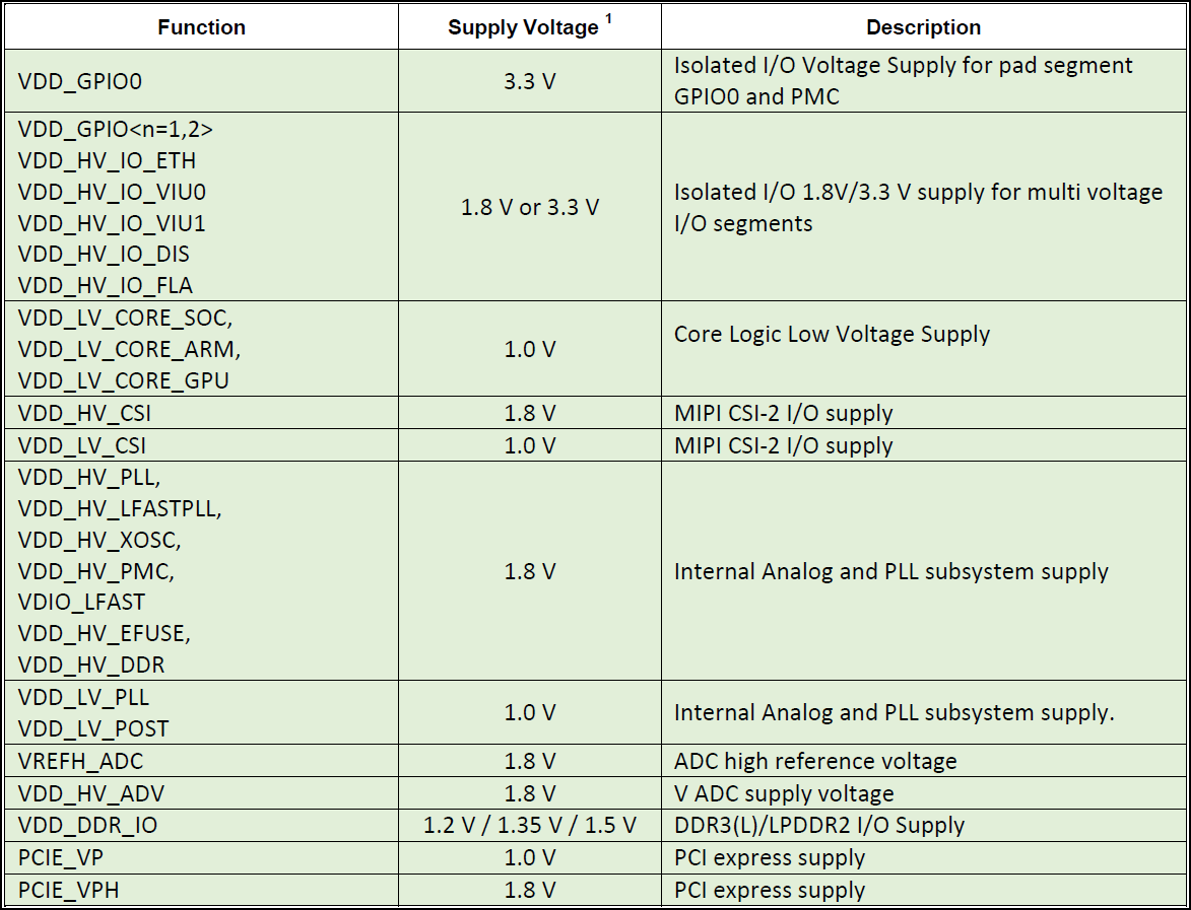

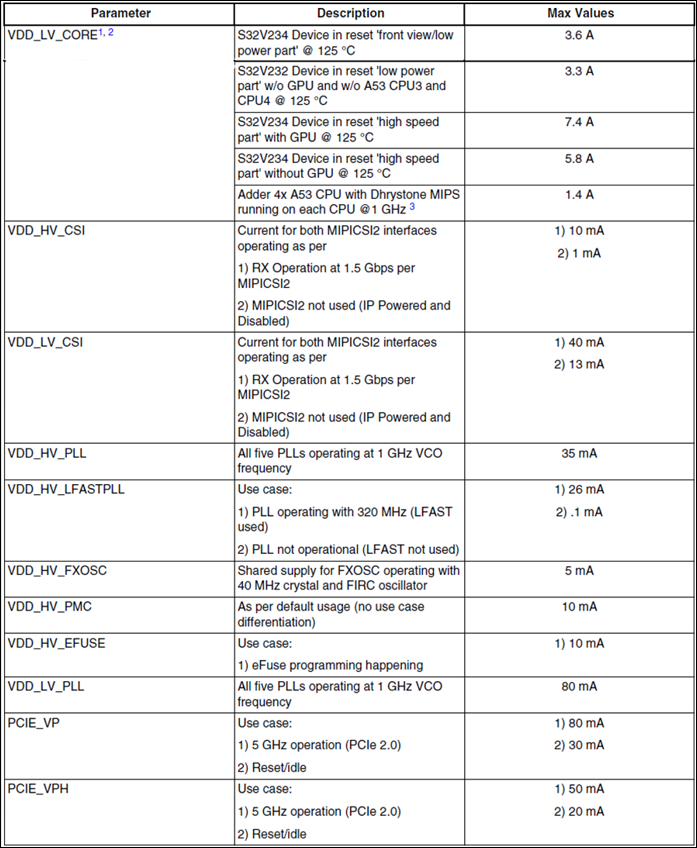

1.2 S32V234 Power List

图 1.2 S32V234 Power List

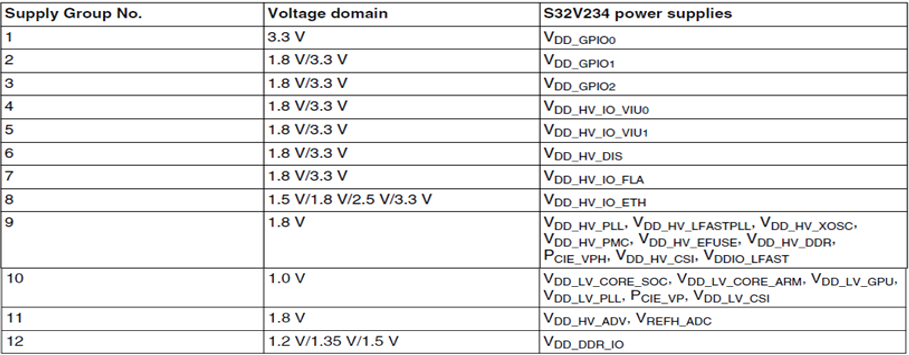

1.3 S32V234 电源时序需求

① PCIE_VP 和 PCIE_VPH 彼此之间应该在 50ms 内上电;

② VDD_HV_CSI 和 VDD_LV_CSI 彼此之间应该在 50ms 内上电;

③ VREFH_ADC 和 VDD_HV_ADC 在上下电时的电压差不能超过 100mV;

④ DDR0_VREF0 和 DDR1_VREF0 应该是跟随 VDD_DDR0_IO 和 VDD_DDR1_IO 变化的,且一直是这两个电压的一半,DDR0_VREF0 和DDR1_VREF0 峰值底噪应该在 +/- 15mV 以内;

⑤ 如果使用 LFAST 接口,VDD_HV_ADC 必须先上电。

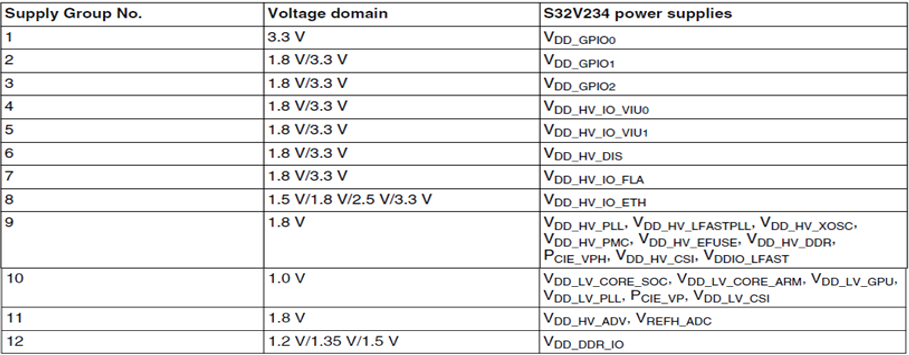

如下总结一些有相同电压域,且已通过测试在上下电时可以被同时控制的电源:

图 1.3 S32V234 supply groups tested for power sequencing

2. 电源设计建议

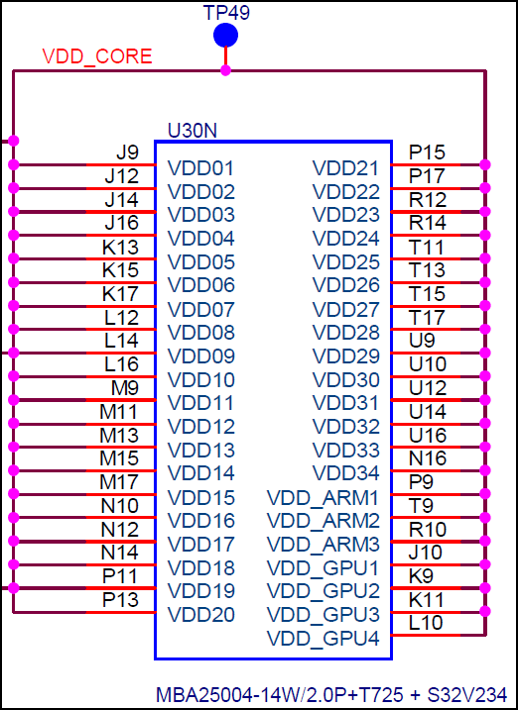

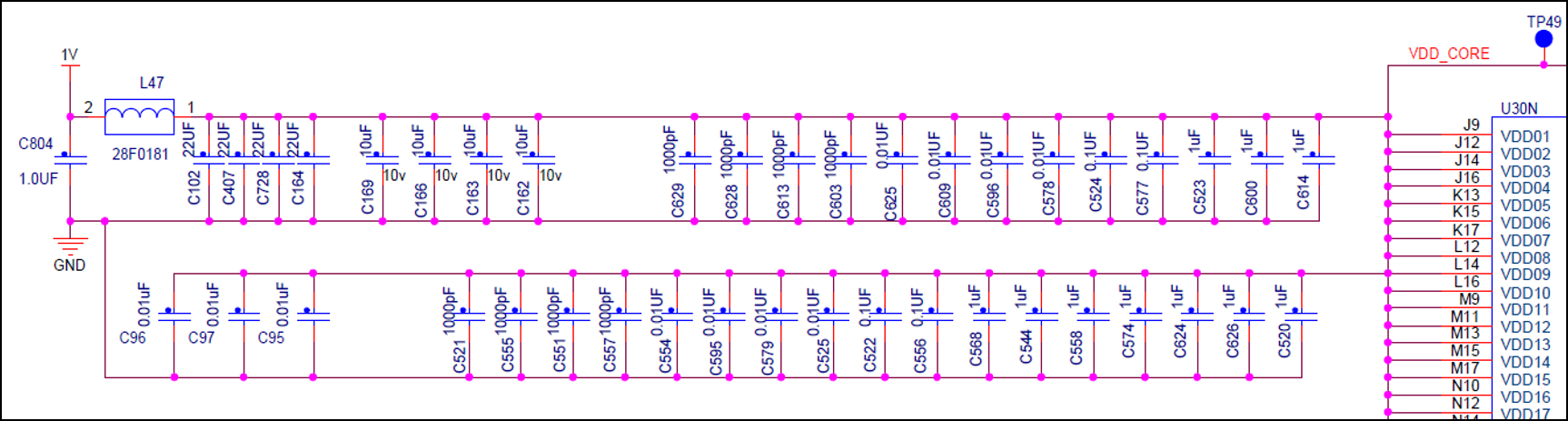

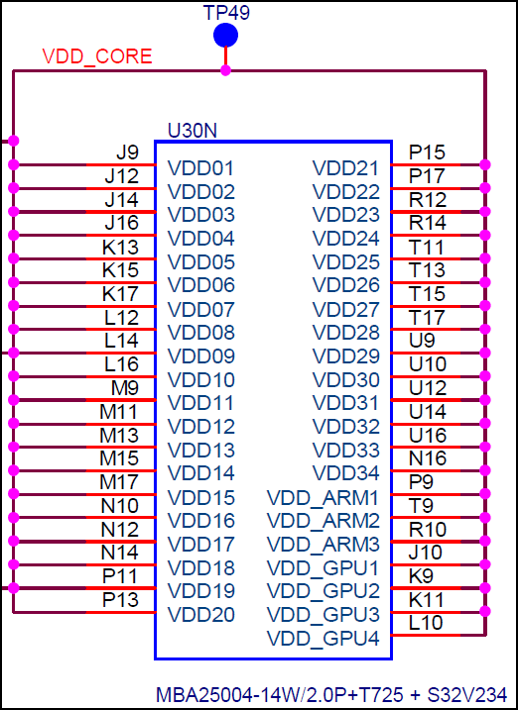

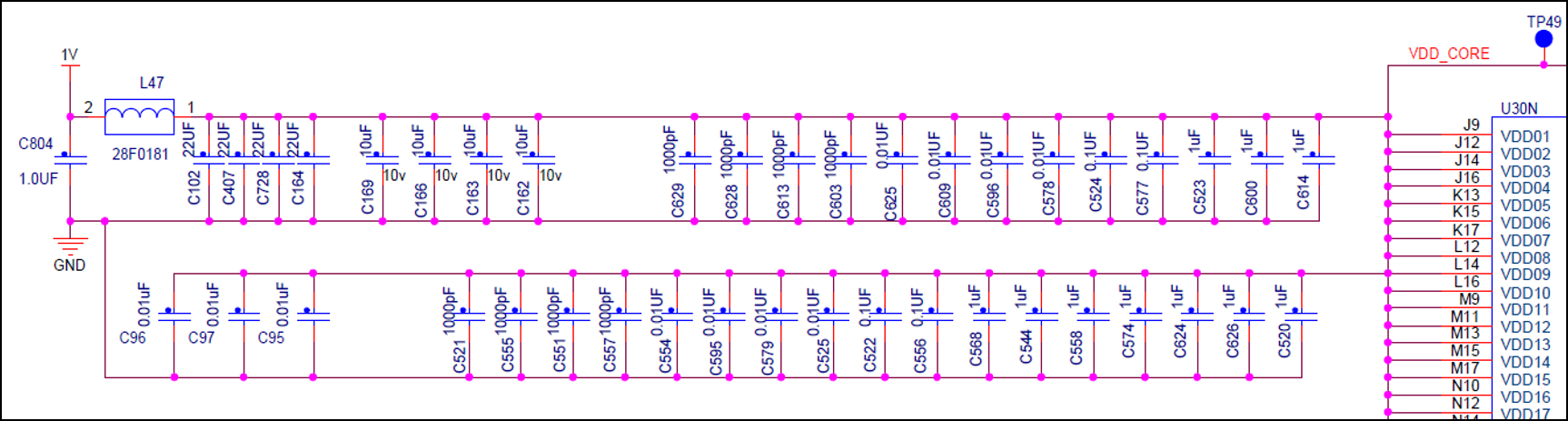

2.1 Core/CPU/GPU 电源

S32V234 的 Core/CPU/GPU 的电源都采用 1V 供电,电流最大时可以达到 10A,所以这里的电容不能删减,且 Layout 时一定要注意电源铺铜面积,保证大电流的通过。

图 1.4 S32V234 VDD_CORE 芯片管脚

图 1.5 S32V234 VDD_CORE 供电电路

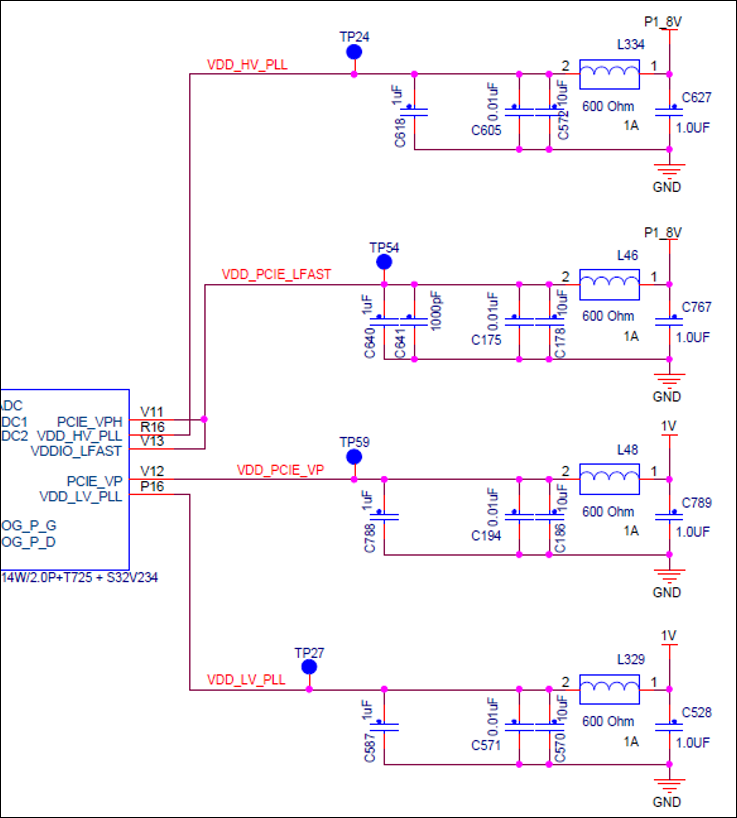

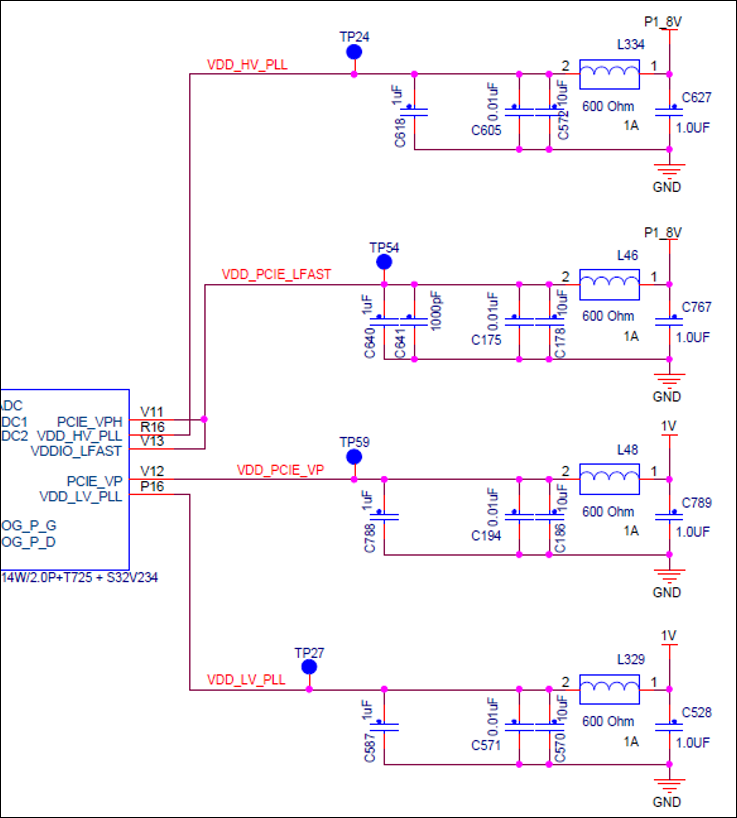

2.2 PLL 电源

S32V234 的 PLL 模块需要 1.8V 和 1V 两路电源供电。

图 1.6 S32V234 VDD_PLL 电路

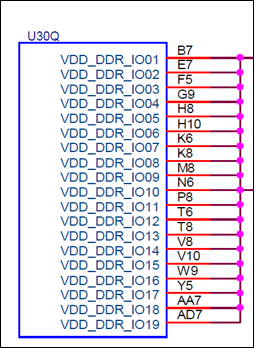

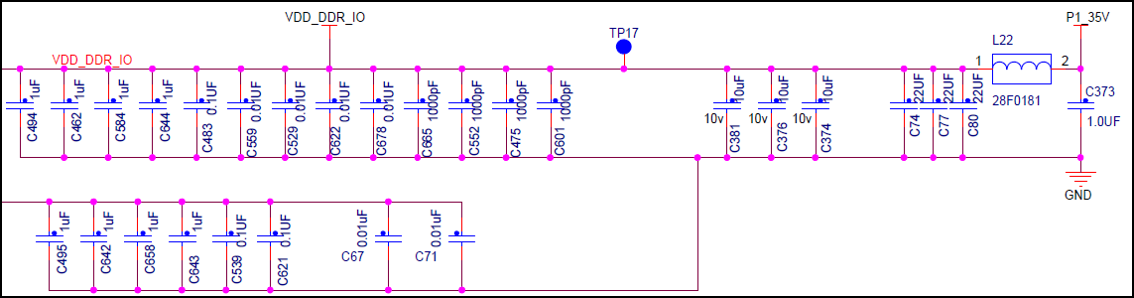

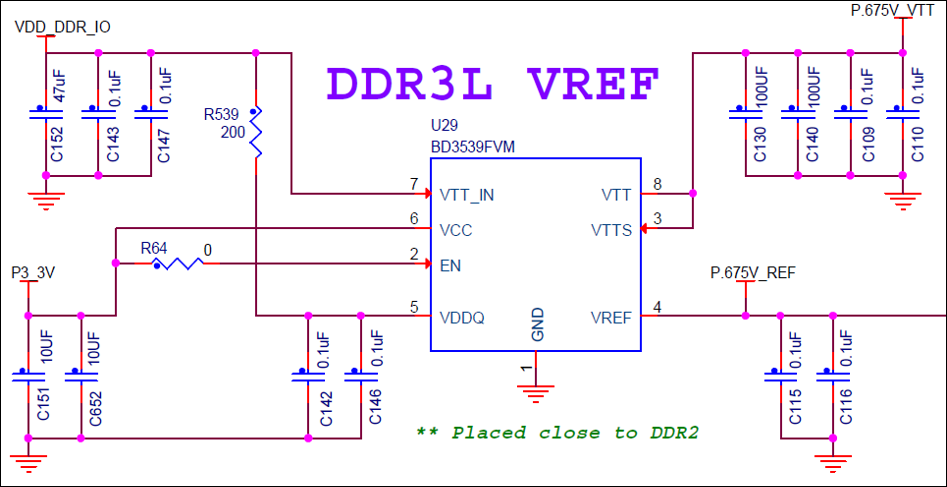

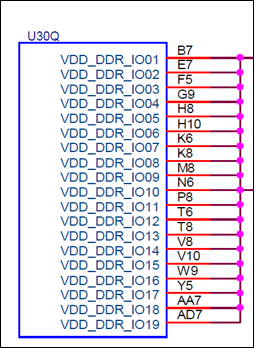

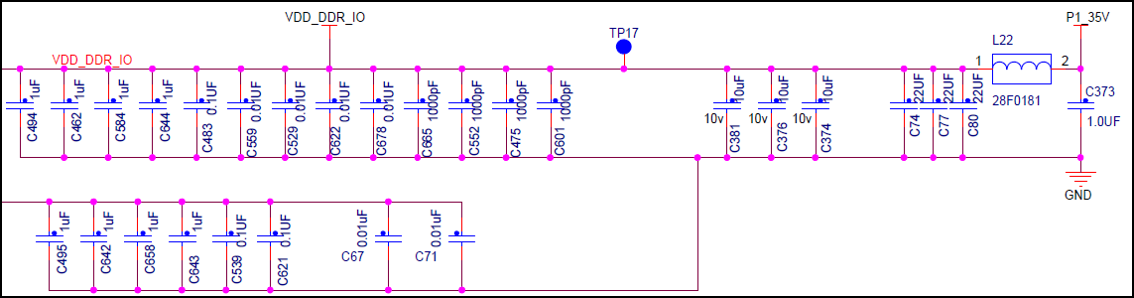

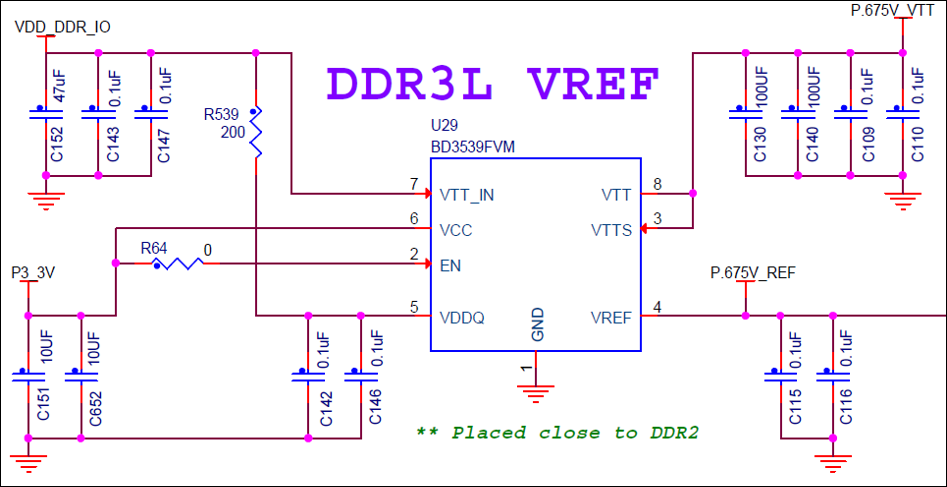

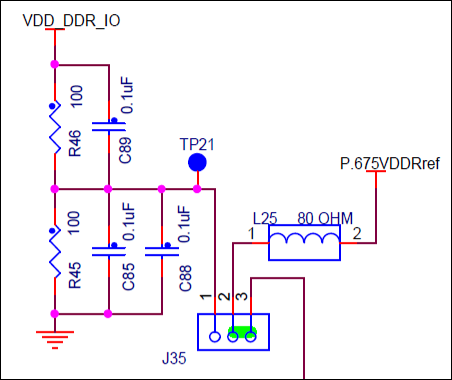

2.3 DDR 电源

S32V234 的控制器接口支持 LPDDR2/DDR3/DDR3L 电平标准。

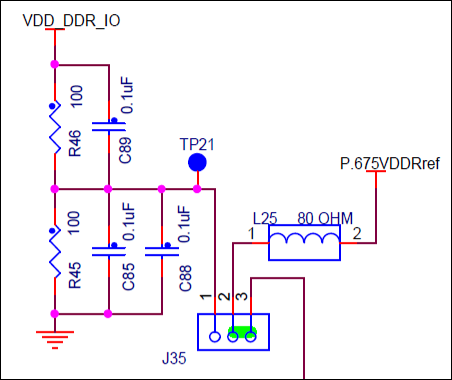

DDR_VREF=VDD_DDR_IO/2 需要用外部电源单独供电,可以用专用芯片或由VDD_DDR_IO 分压的方式获得。

如果有用到 0.675_VTT 电源,务必采用芯片单独供电,不能和 DDR_VREF 共网络。

图 1.7 DDR 控制供电管脚

图 1.8 DDR 控制器供电网络

图 1.9 用专用芯片产生 VREF

图 1.10 由分压电阻产生 VREF

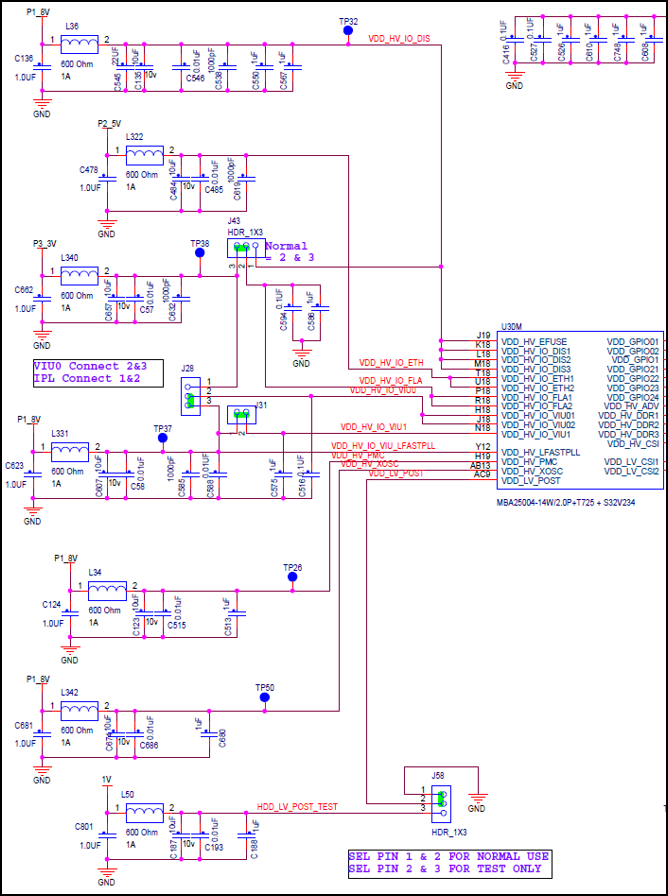

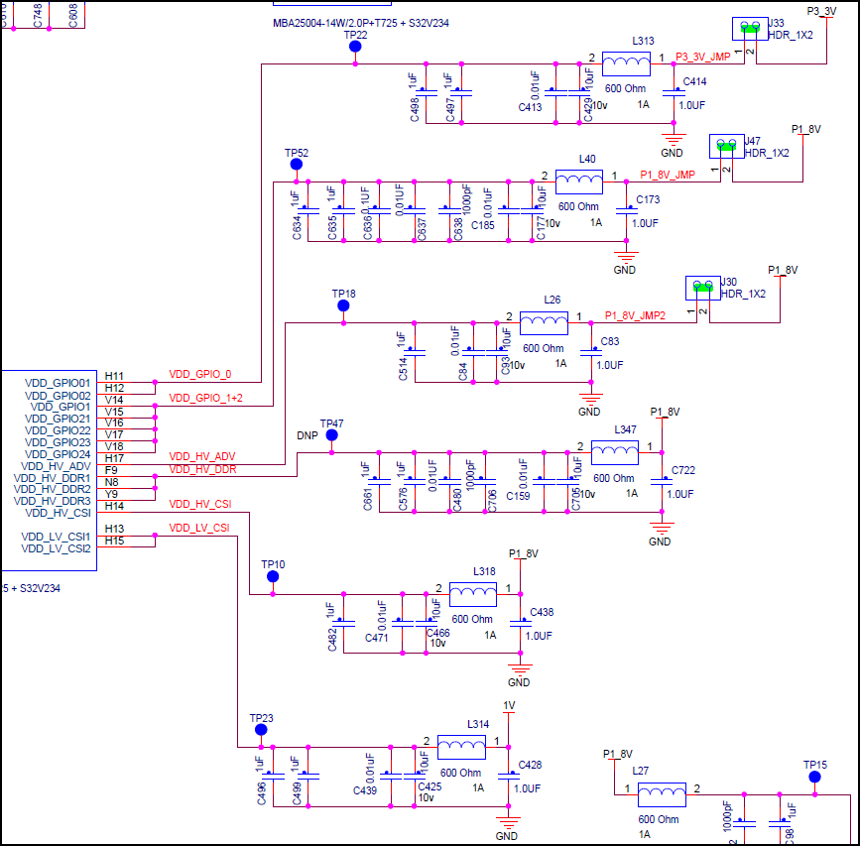

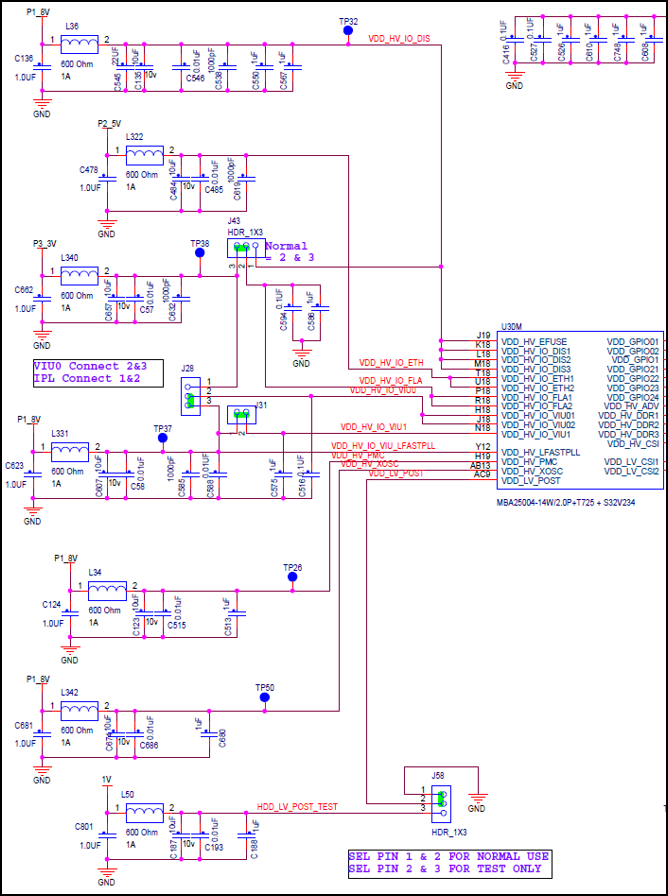

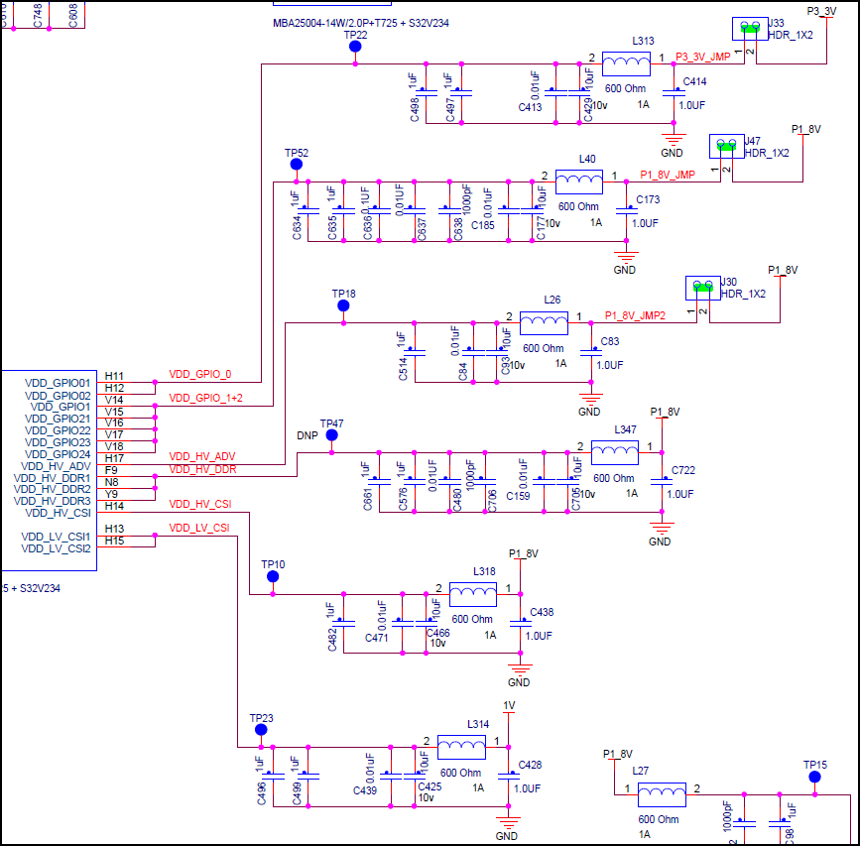

2.4 IO 电源

S32V234 的 IO 电压域可以配置成 1.8V 和 3.3V 两种,建议靠近相应管脚摆放去耦电容。

图 1.11 S32V234 IO 供电管脚(一)

图 1.12 S32V234 IO 供电管脚(二)

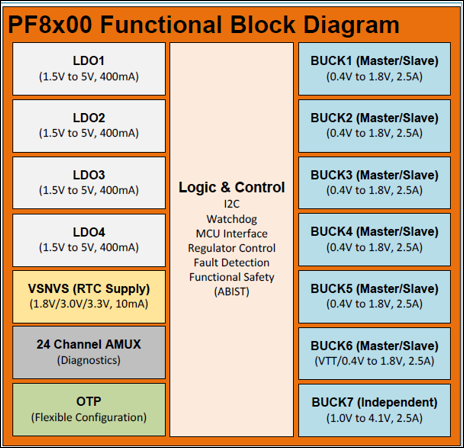

2.5 PF8X00 PMIC 方案

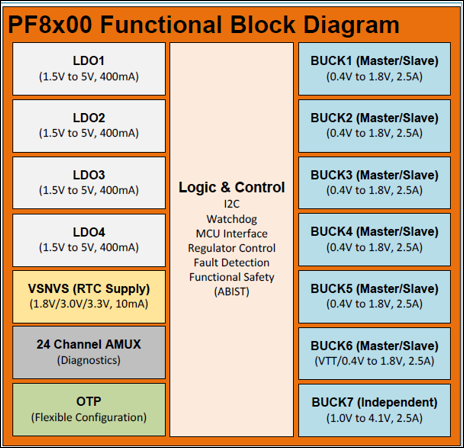

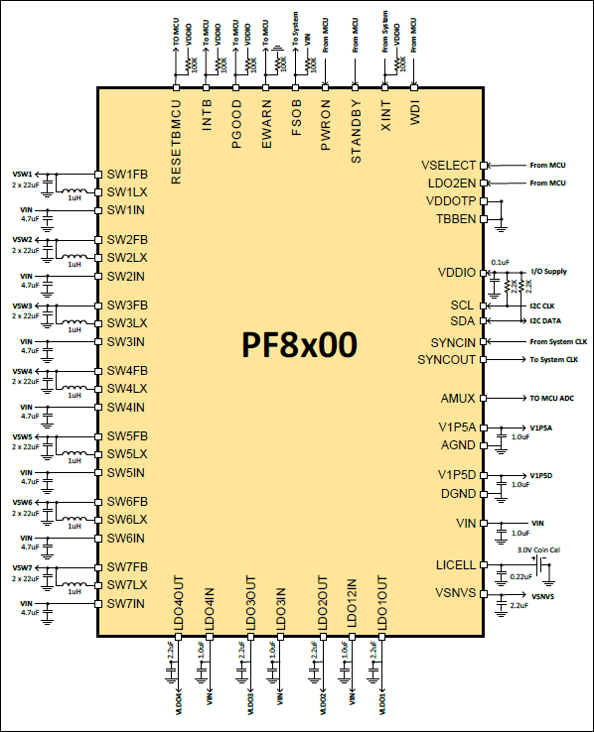

2.5.1 PF8X00 框图

图 1.13 PF8X00 框图

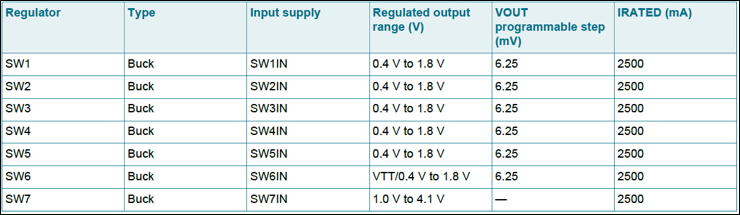

2.5.2 PF8X00 特征

① 输入电压范围:-0.3V ~ 6V;

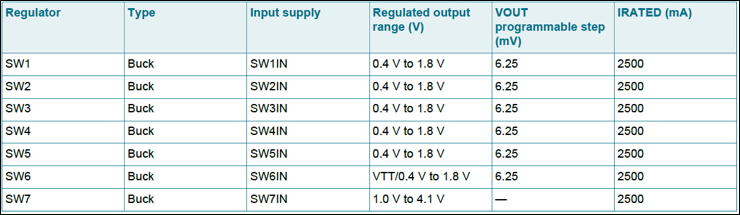

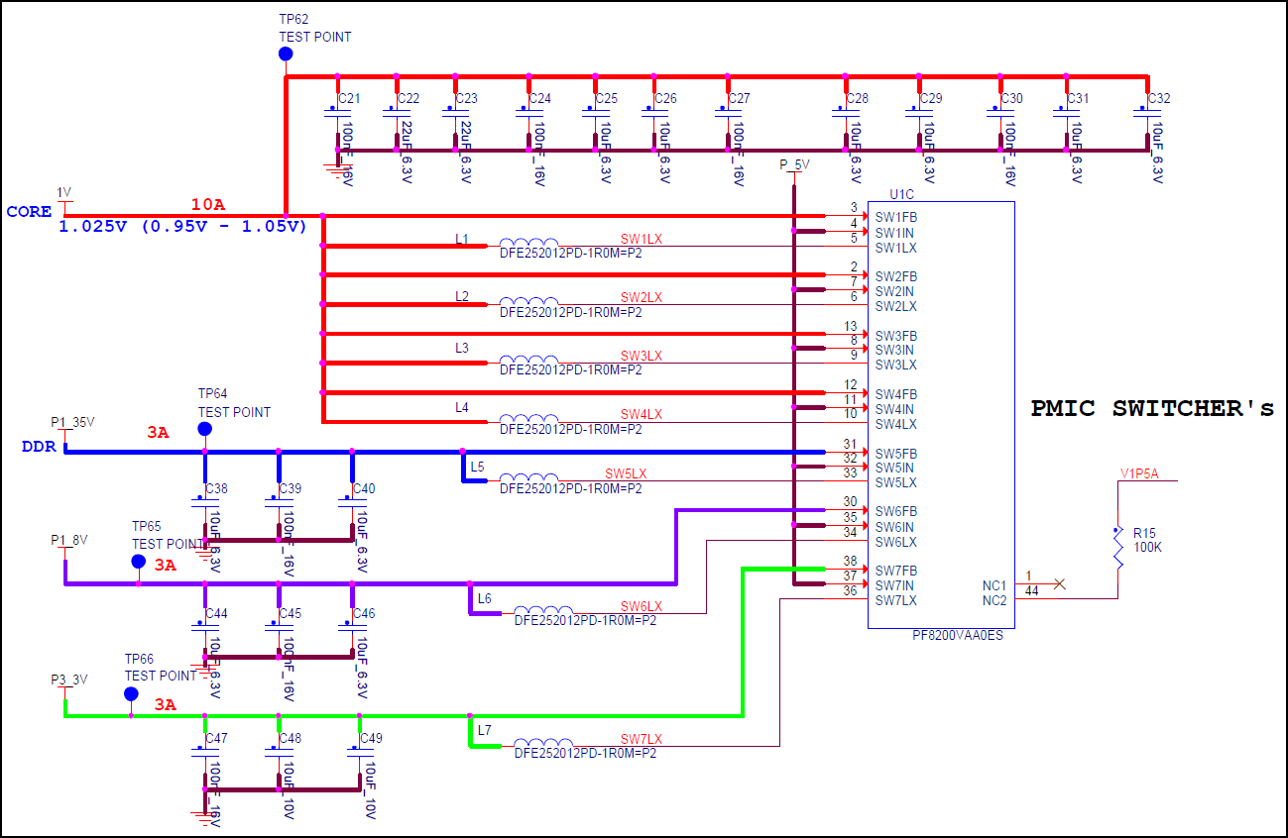

② 7 个高性能可配置 BUCK DCDC 转换器,如 图 1.13;

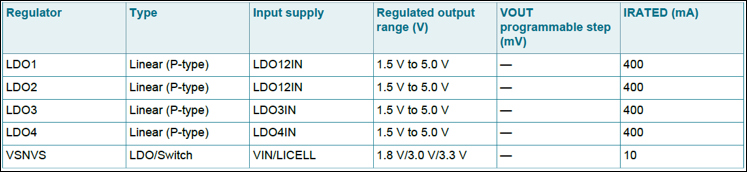

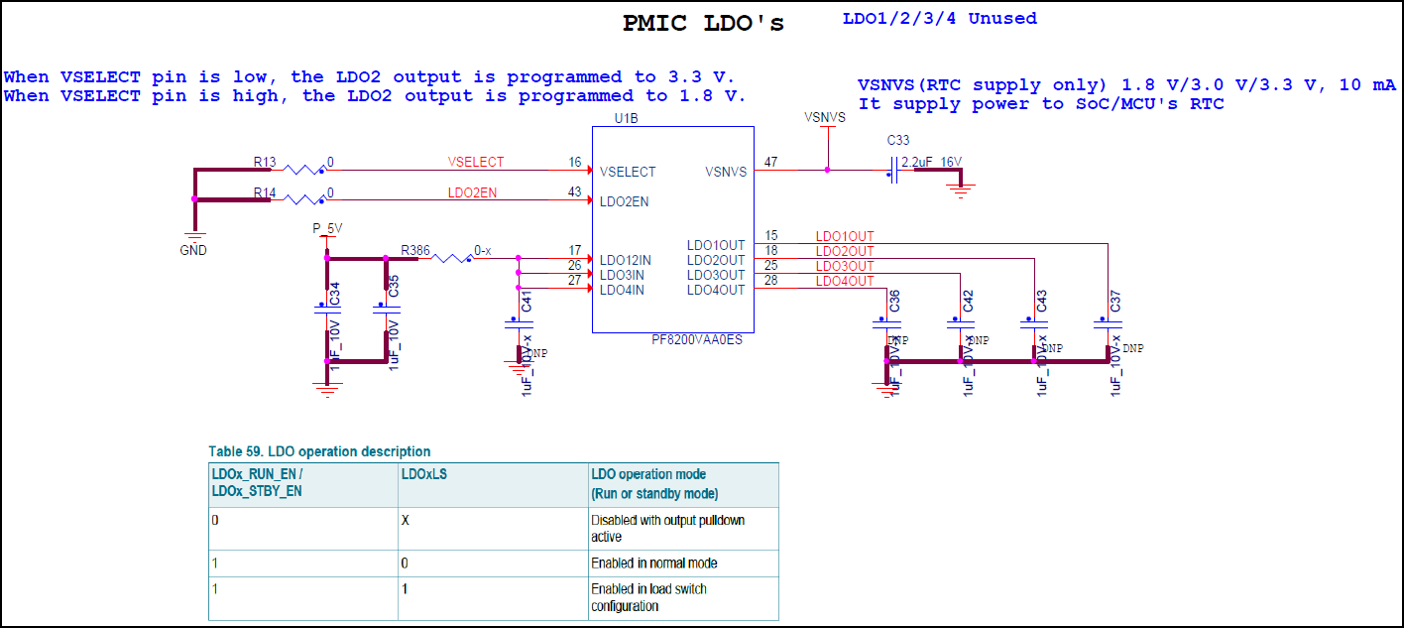

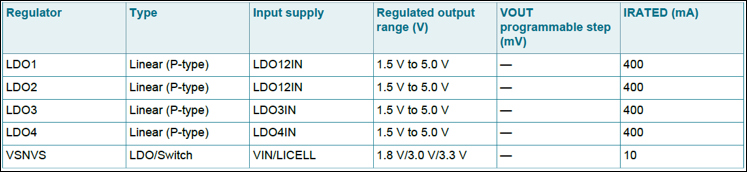

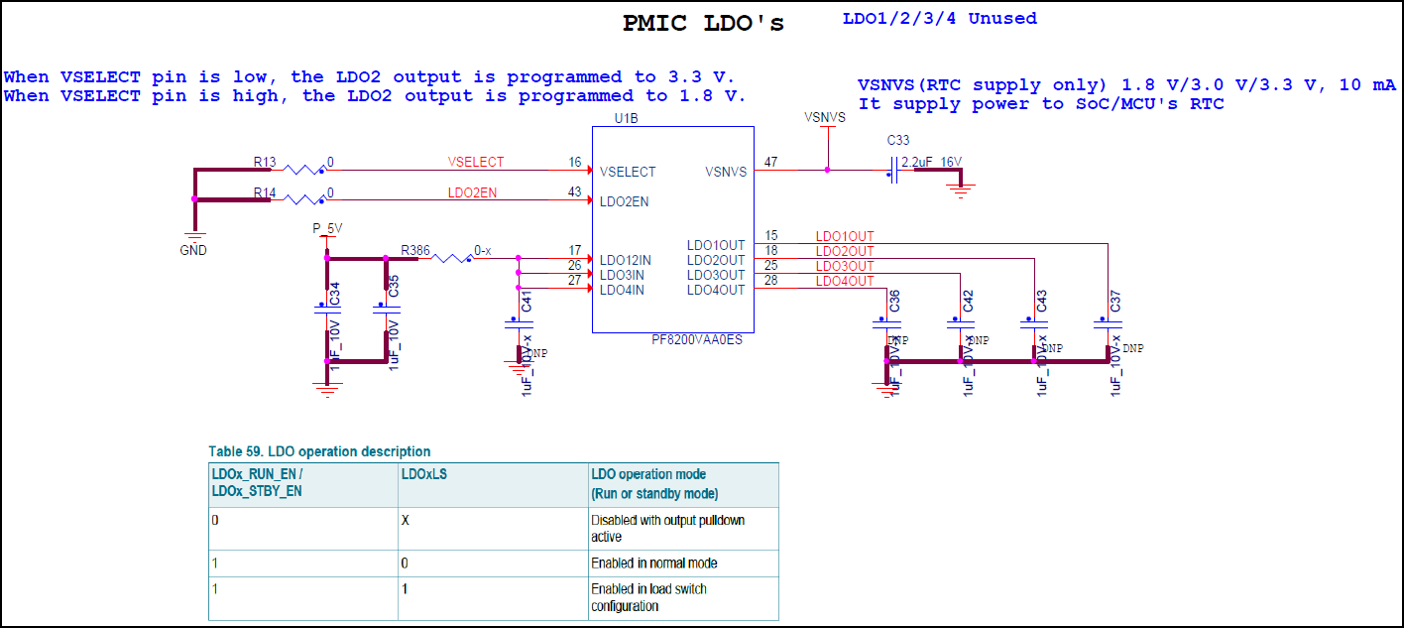

③ 4 个线性可配置 LDO,如 图 1.14;

④ 看门狗监控功能;

⑤ 安全等级监控电路;

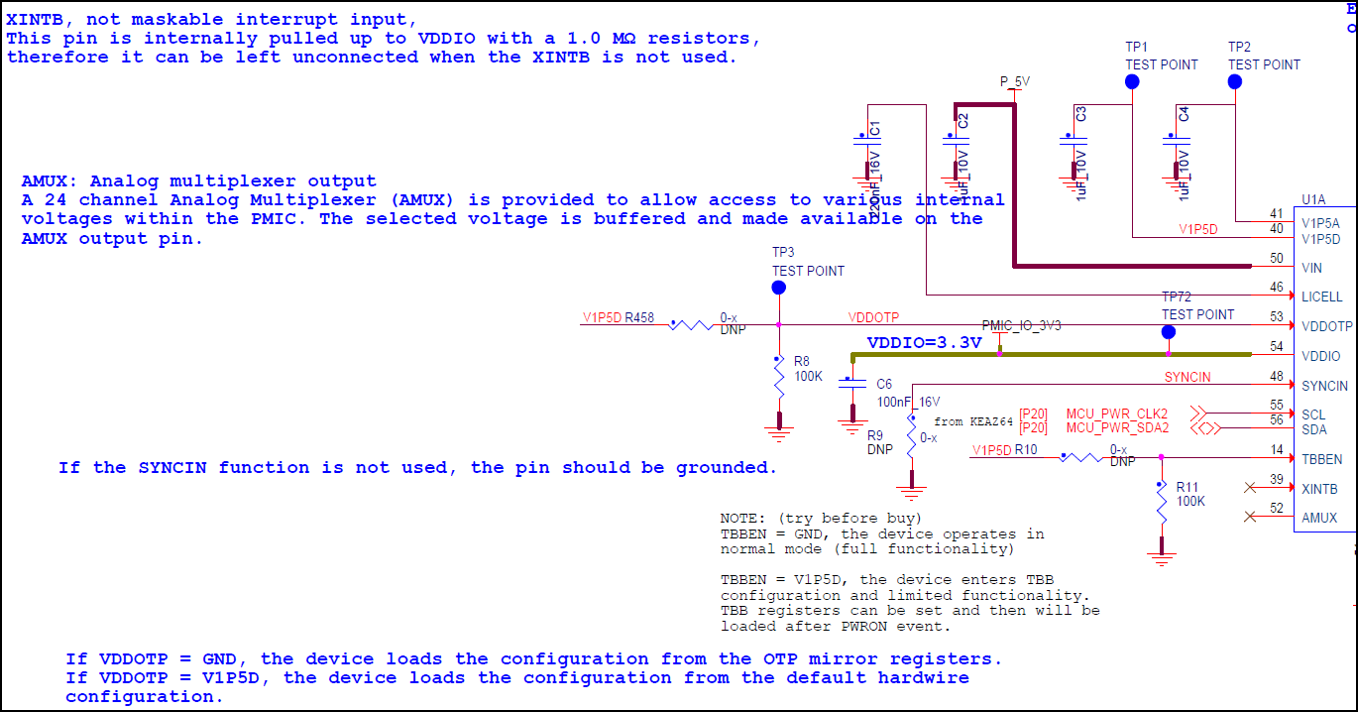

⑥ 3.4MHz I2C 通讯接口;

⑦ PGOOD 监控功能;

⑧ 可配置 OTP 存储。

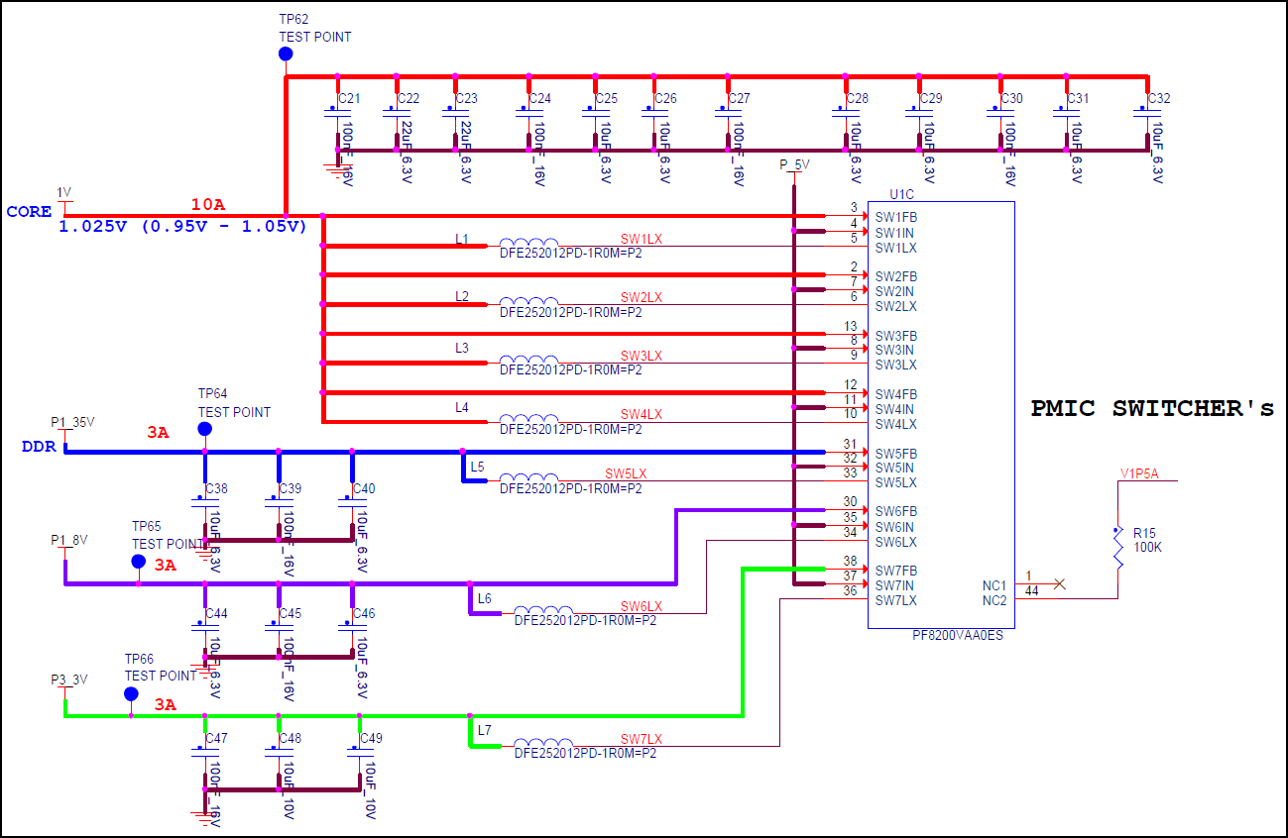

图 1.14 PF8200 BUCK DCDC 输出

图 1.15 PF8200 LDO 输出

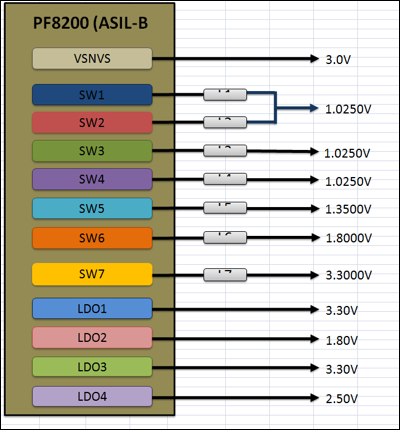

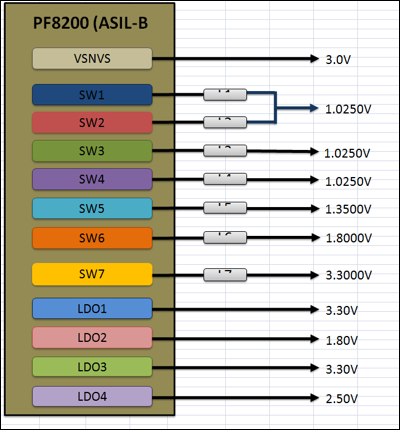

2.5.3 S32V234 + PF8200 Power Tree

S32V234 平台采用 PF8200 系列 PMIC,设计时需根据实际的电源分配情况给 PMIC 烧录对应的固件。

图 1.16 S32V234 + PF8200 推荐电源方案

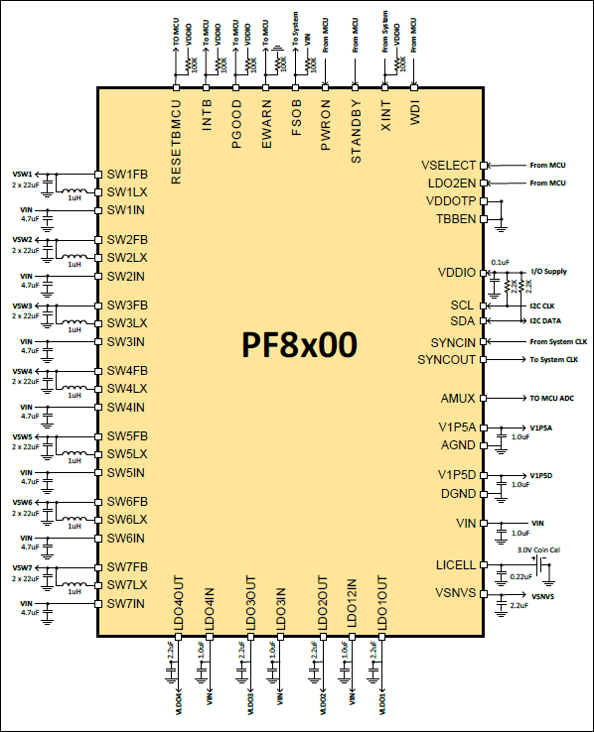

2.5.4 PF8X00 应用框图

图 1.17 PF8X00 应用框图

2.5.5 PF8X00 原理图设计注意事项

① 4 路 BUCK DCDC 的储能电感能够通过最大电流保证在 2.5A 以上,输出电容建议大于 30uF ,输入部分靠近对应管脚添加足够多的电容;

图 1.18 S32V234 + PF8200 BUCK DCDC 参考原理图

② 如果使用适配器直接给 PF8200 供电,建议在输入电源前端加 TVS 管;

③ LDO2 的输出可以通过外部管脚 VSELECT 来进行不同配置(1.8V & 3.3V);

图 1.19 S32V234 + PF8200 LDO 参考原理图

1. NXP S32V234 平台最小系统(CPU + DDR + Flash + Reset + Power)电源介绍

1.1 S32V234 最小系统电源框图

图 1.1 S32V234 Power supply concept

1.2 S32V234 Power List

图 1.2 S32V234 Power List

1.3 S32V234 电源时序需求

① PCIE_VP 和 PCIE_VPH 彼此之间应该在 50ms 内上电;

② VDD_HV_CSI 和 VDD_LV_CSI 彼此之间应该在 50ms 内上电;

③ VREFH_ADC 和 VDD_HV_ADC 在上下电时的电压差不能超过 100mV;

④ DDR0_VREF0 和 DDR1_VREF0 应该是跟随 VDD_DDR0_IO 和 VDD_DDR1_IO 变化的,且一直是这两个电压的一半,DDR0_VREF0 和DDR1_VREF0 峰值底噪应该在 +/- 15mV 以内;

⑤ 如果使用 LFAST 接口,VDD_HV_ADC 必须先上电。

如下总结一些有相同电压域,且已通过测试在上下电时可以被同时控制的电源:

图 1.3 S32V234 supply groups tested for power sequencing

2. 电源设计建议

2.1 Core/CPU/GPU 电源

S32V234 的 Core/CPU/GPU 的电源都采用 1V 供电,电流最大时可以达到 10A,所以这里的电容不能删减,且 Layout 时一定要注意电源铺铜面积,保证大电流的通过。

图 1.4 S32V234 VDD_CORE 芯片管脚

图 1.5 S32V234 VDD_CORE 供电电路

2.2 PLL 电源

S32V234 的 PLL 模块需要 1.8V 和 1V 两路电源供电。

图 1.6 S32V234 VDD_PLL 电路

2.3 DDR 电源

S32V234 的控制器接口支持 LPDDR2/DDR3/DDR3L 电平标准。

DDR_VREF=VDD_DDR_IO/2 需要用外部电源单独供电,可以用专用芯片或由VDD_DDR_IO 分压的方式获得。

如果有用到 0.675_VTT 电源,务必采用芯片单独供电,不能和 DDR_VREF 共网络。

图 1.7 DDR 控制供电管脚

图 1.8 DDR 控制器供电网络

图 1.9 用专用芯片产生 VREF

图 1.10 由分压电阻产生 VREF

2.4 IO 电源

S32V234 的 IO 电压域可以配置成 1.8V 和 3.3V 两种,建议靠近相应管脚摆放去耦电容。

图 1.11 S32V234 IO 供电管脚(一)

图 1.12 S32V234 IO 供电管脚(二)

2.5 PF8X00 PMIC 方案

2.5.1 PF8X00 框图

图 1.13 PF8X00 框图

2.5.2 PF8X00 特征

① 输入电压范围:-0.3V ~ 6V;

② 7 个高性能可配置 BUCK DCDC 转换器,如 图 1.13;

③ 4 个线性可配置 LDO,如 图 1.14;

④ 看门狗监控功能;

⑤ 安全等级监控电路;

⑥ 3.4MHz I2C 通讯接口;

⑦ PGOOD 监控功能;

⑧ 可配置 OTP 存储。

图 1.14 PF8200 BUCK DCDC 输出

图 1.15 PF8200 LDO 输出

2.5.3 S32V234 + PF8200 Power Tree

S32V234 平台采用 PF8200 系列 PMIC,设计时需根据实际的电源分配情况给 PMIC 烧录对应的固件。

图 1.16 S32V234 + PF8200 推荐电源方案

2.5.4 PF8X00 应用框图

图 1.17 PF8X00 应用框图

2.5.5 PF8X00 原理图设计注意事项

① 4 路 BUCK DCDC 的储能电感能够通过最大电流保证在 2.5A 以上,输出电容建议大于 30uF ,输入部分靠近对应管脚添加足够多的电容;

图 1.18 S32V234 + PF8200 BUCK DCDC 参考原理图

② 如果使用适配器直接给 PF8200 供电,建议在输入电源前端加 TVS 管;

③ LDO2 的输出可以通过外部管脚 VSELECT 来进行不同配置(1.8V & 3.3V);

图 1.19 S32V234 + PF8200 LDO 参考原理图

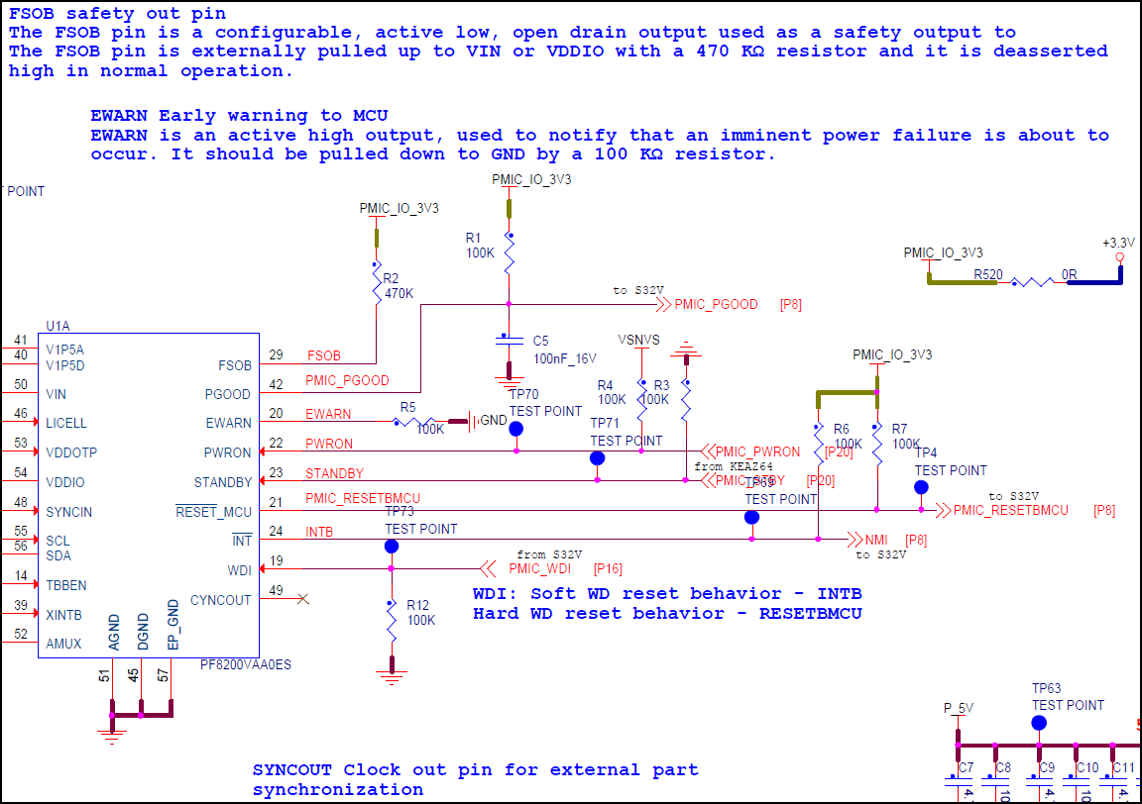

④ 输出状态脚有 PGOOD 、EWARN、FSOB,如果需要使用,需要在 OTP 文件中配置,硬件上接到相应的模块(GPIO、指示灯电路);

⑤ 输入管脚 PWRON、STANBY、XINBY、WDI 需要根据具体设计要求进行设计,外围的上下拉电阻需要和 OTP 文件中的配置对应。

图 1.20 S32V234 + PF8200 控制及指示端口参考原理图(一)

图 1.21 S32V234 + PF8200 控制及指示端口参考原理图(二)

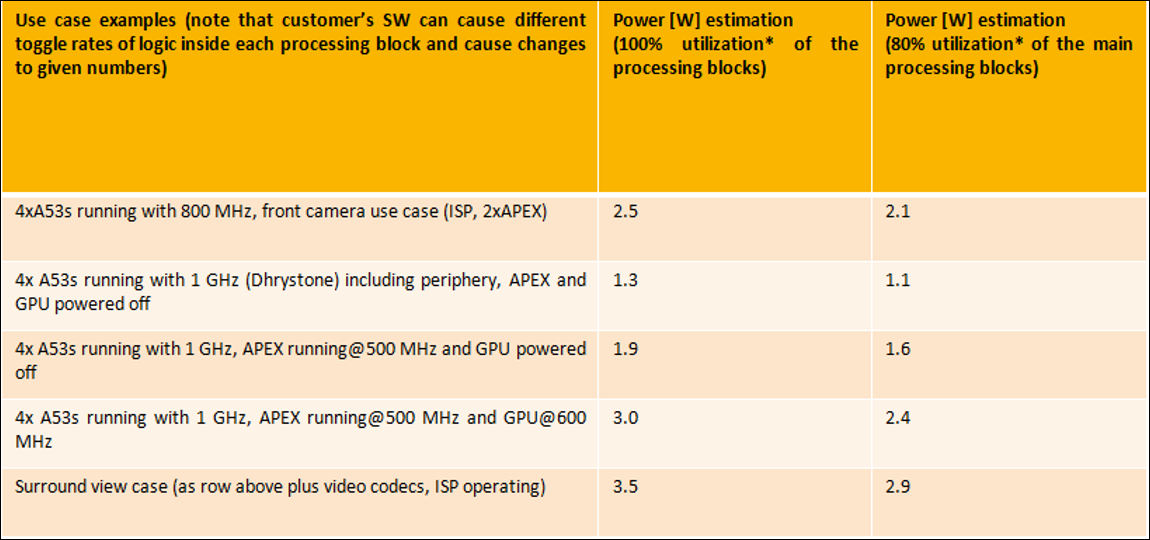

3. S32V234 功耗情况

3.1 S32V234 功耗表

图 1.22 S32V234 功耗表

图 1.23 S32V234 不同工作情况下的参考功耗表

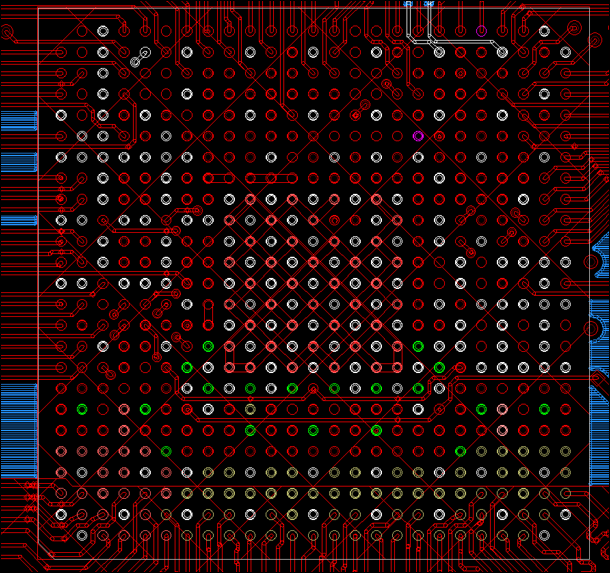

二、PCB Layout 部分

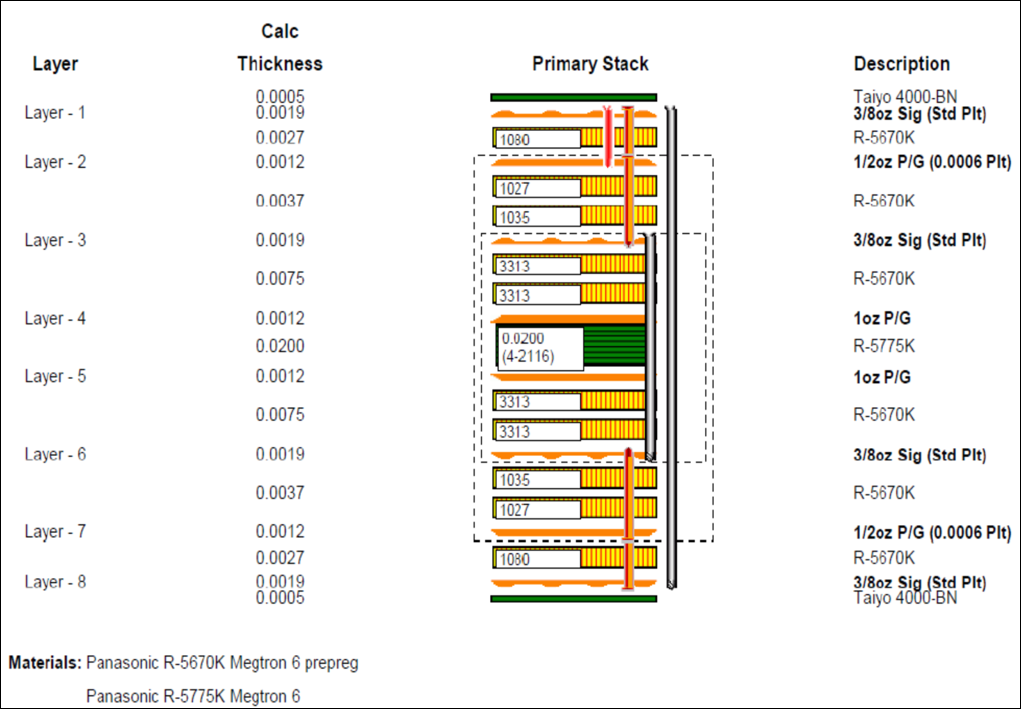

1. 为了保证 S32V234 有更高的性能表现,推荐使用 8 层或以上的 PCB 叠层结构,同时建议器件采用双面贴片设计,以下 S32V234-EVB2 PCB 叠层结构可作为参考。

图 2.1 Layer stack S32V234-EVB2 board

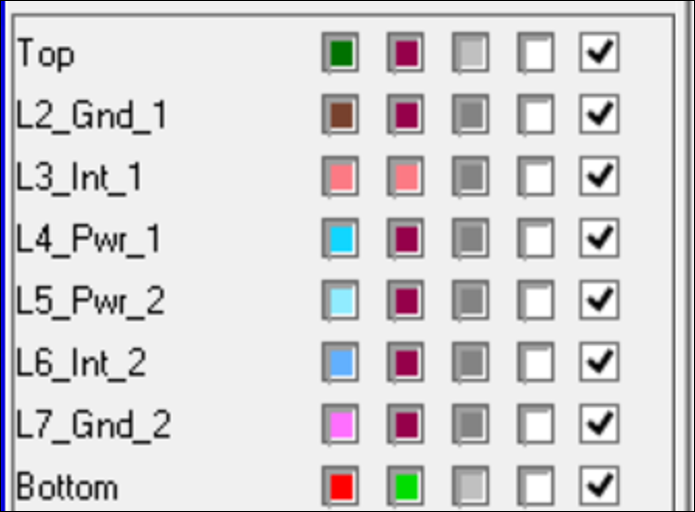

2. 层的定义设计原则

① 器件面下层(第二层)为地平面,为器件面布线提供参考平面;

② 所有信号层尽可能与地平面相邻;

③ 主电源层尽可能与对应地层相邻;

④ 建议采用对称结构设计。

图 2.2 PCB 层定义参考

3. GND 的处理

① PCB 上必须有一层完整的 GND 层,用于散热和保证信号完整性;

② 保证芯片每一个 GND PAD 有对应的过孔,连接到主地上。

图 2.3 S32V234 GND PAD 上的盲孔

4. 电源处理

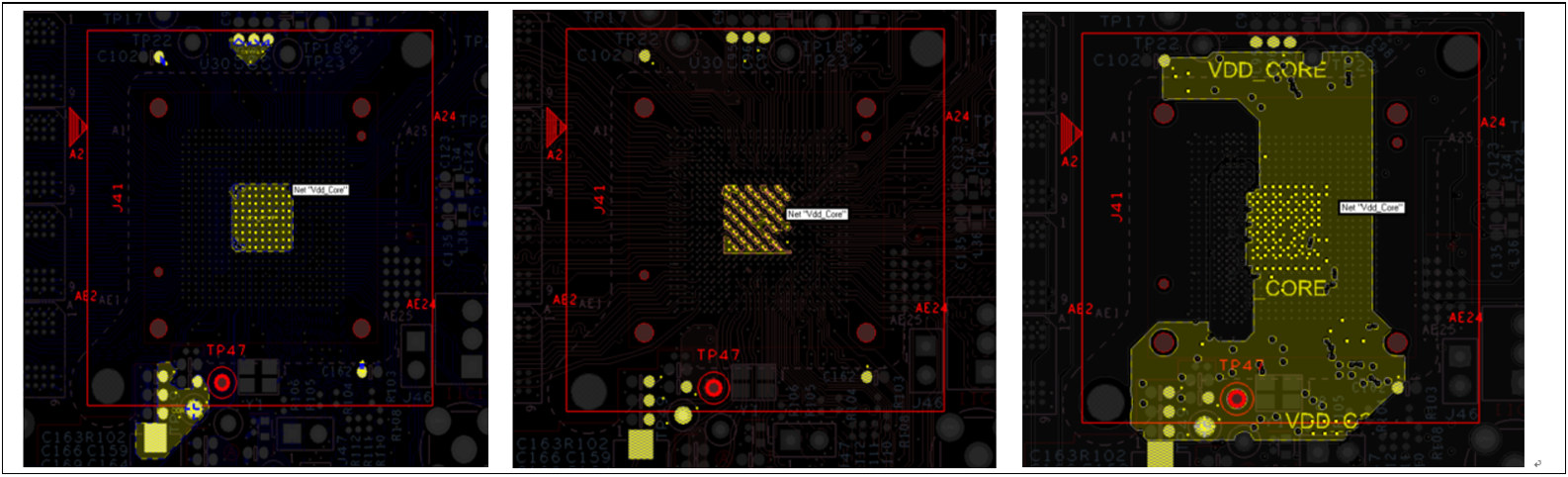

4.1 VDD_LV_CORE 给芯片的计算单元供电,为主要电源;在使用前视功能时,预估达到 5W 的功耗;在使用环视功能应用时,预估达到 10W 的功耗;

所以在设计时对此网络建议如下处理:

① 电源网络采用覆铜处理;

② 采用多层网络供电;

③ 每个 VDD_LV_CORE PAD 有对应的一个过孔连到电源平面。

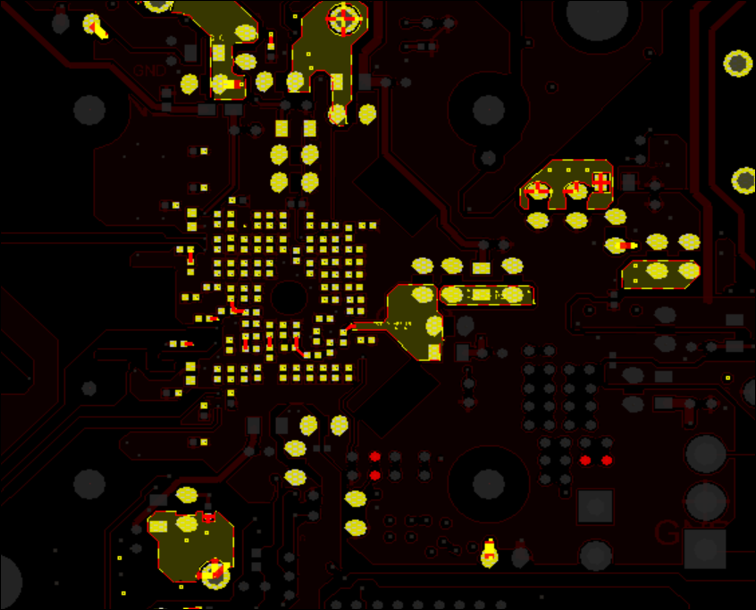

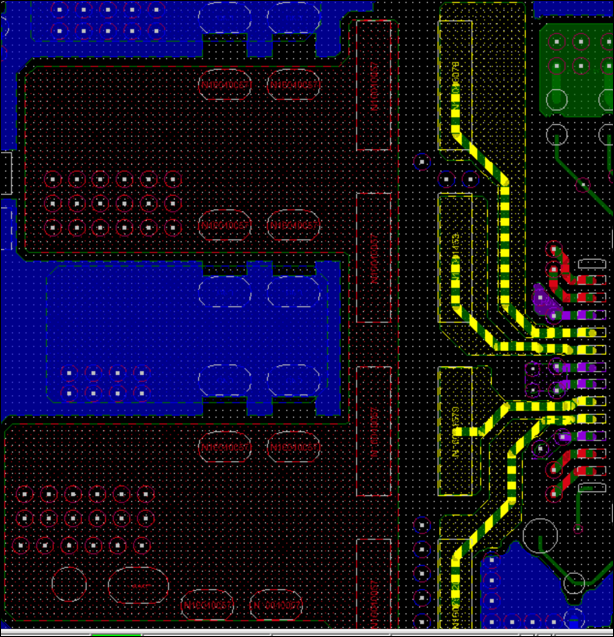

图 2.4 VDD_LV_CORE 覆铜处理(L1、L3、L5)

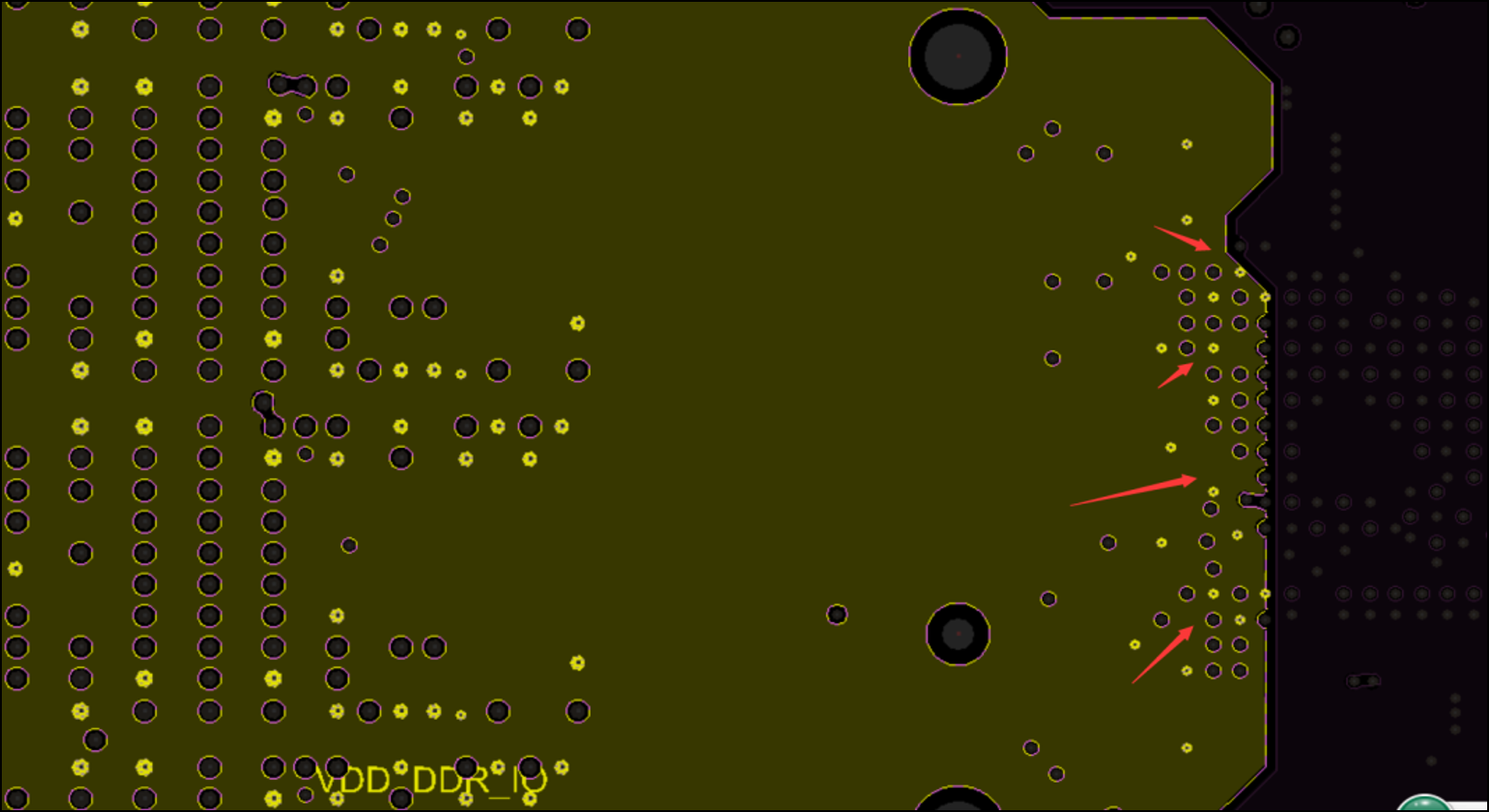

4.2 VDD_DDR_IO 从电源输出端到 S32V234 和 DDR 的相关引脚要有大面积覆铜,降低大电流时铜皮带来的压降;同时注意其它信号过孔的放置,避免出现密集区以致覆铜面积减少。

图 2.5 VDD_DDR_IO 覆铜处理

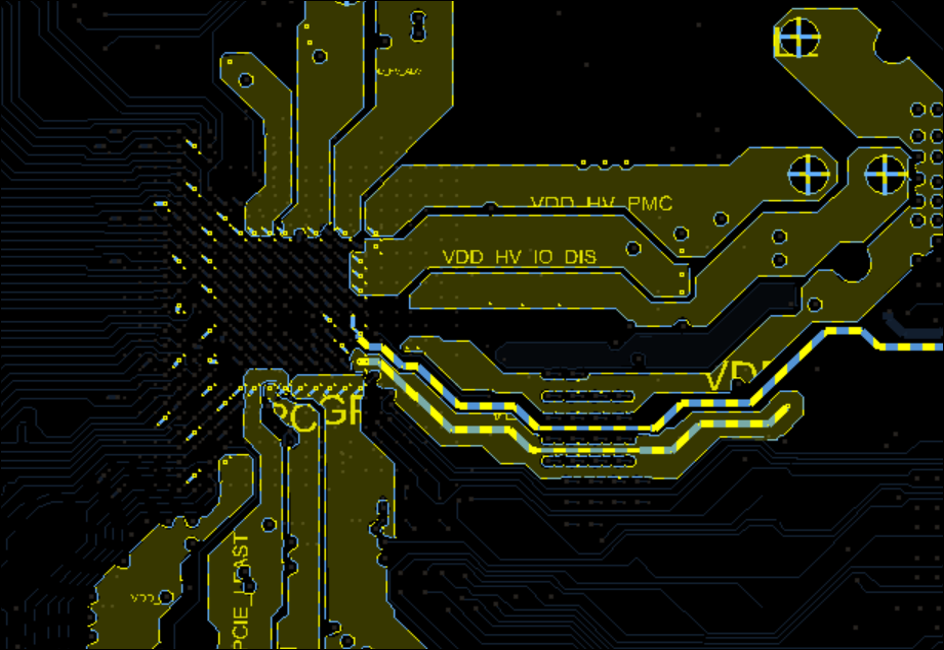

4.3 VDD_HV_PLL、VDD_LV_PLL、VDD_GPIO 等相关电源引脚保证有尽量宽的供电网络(根据 电源功耗表 中的电流大小来设定铜皮宽度,预留至少 20% 余量),以减少走线阻抗,提高电源的稳定性。

图 2.6 S32V234 相关电源处理

4.4 S32V234 位置的 PCB 背面放置必要的 0201 封装大小滤波电容;针对 VDD_CORE、VDD_DDR_IO、VDD_PLL、VDD_CSI 等网络上的大电容尽量靠近芯片放置,以改善电源质量,提高产品性能。

图 2.7 S32V234 电源滤波电容

4.5 建议电源层采用 1oz 铜皮厚度。

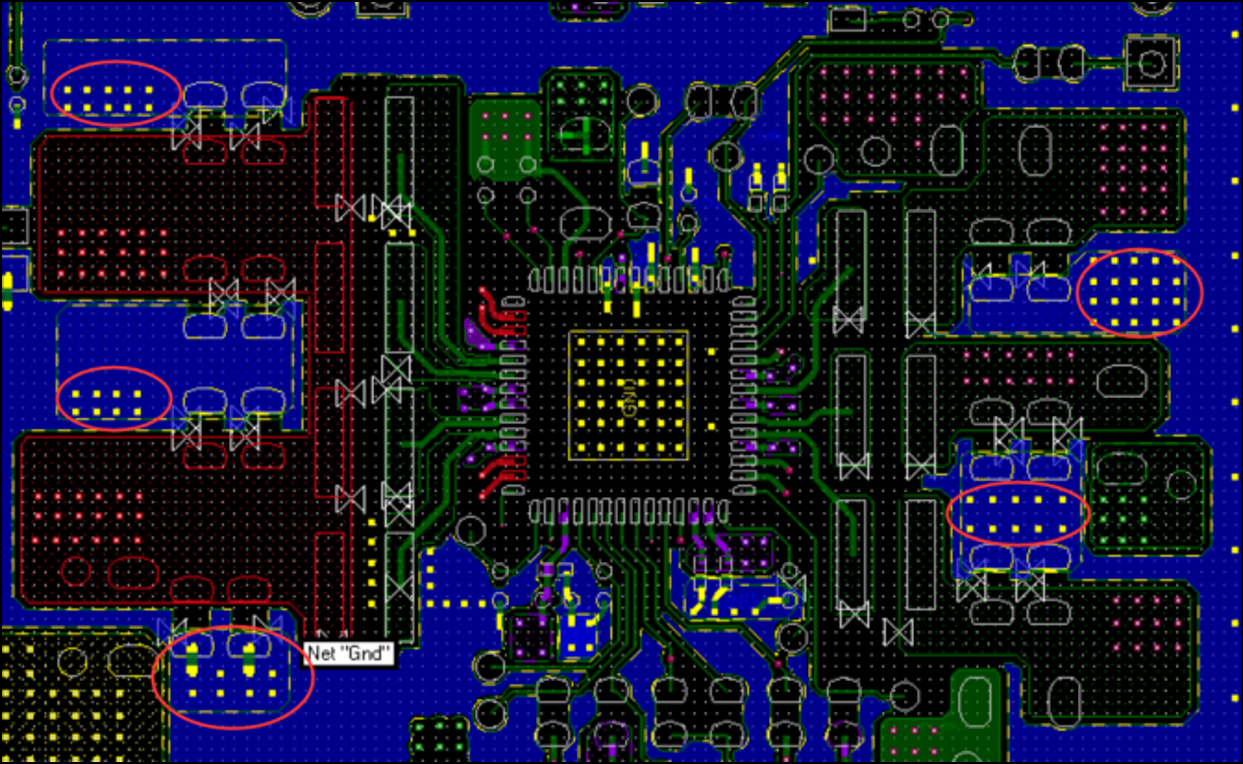

4.6 PCB 直线宽度允许最大电流的经验计算公式:

公式中 K 为修正系数,覆铜线在内层时取 0.024,在外层时取 0.048;T 为允许的最大温升,单位为 ℃(摄氏度);A 为覆铜的截面积,单位为平方 mil;I 为容许的最大电流,单位为 A(安培)。

4.7 PMIC(PF8X00)处理

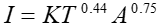

4.7.1 各路 DCDC 的输入要打尽量多的过孔连接到供电网络,特别是 DCDC1~4 的输入端。

图 2.8 DCDC(P5V)输入电源

4.7.2 DCDC 输入电源的去耦电容靠近 PMIC 端,输出电容靠近电感端,并保证电容负极端有足够的地过孔,保证去耦效果。

图 2.9 DCDC 去耦电容过孔

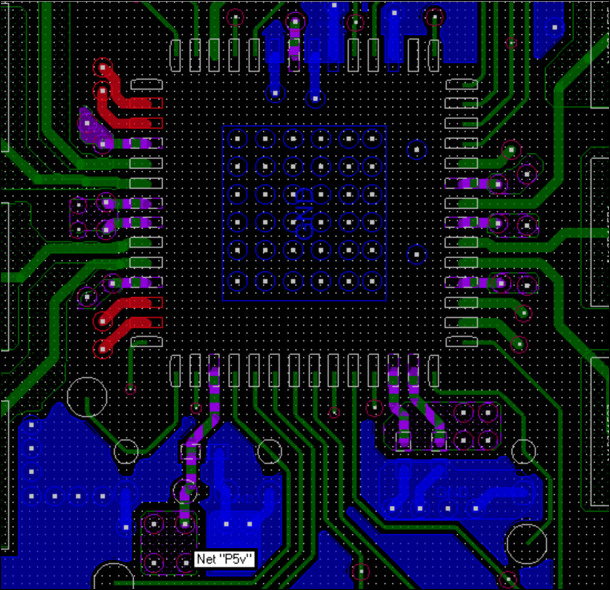

4.7.3 由于 DCDC1~4 是供给 S32V234 的 Core 电压,所以电源网络必须做尽量宽的覆铜处理,有利于减少阻抗和增强散热效果。

图 2.10 DCDC1~4 输出覆铜处理

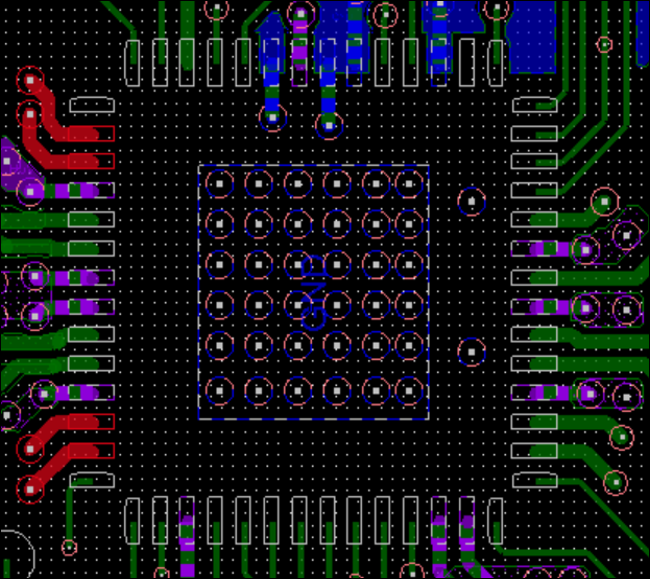

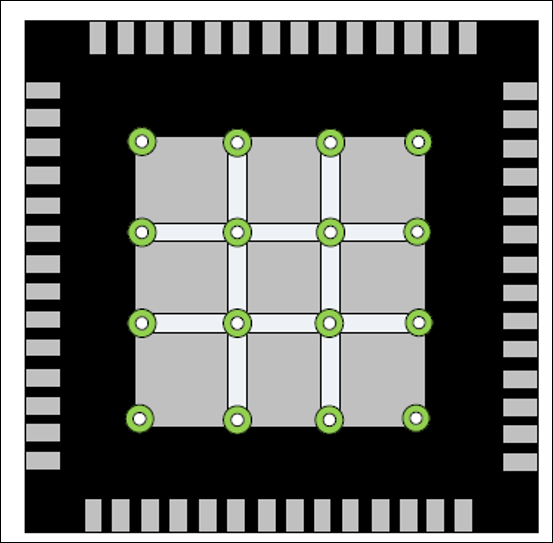

4.7.4 PF8X00 EPAD 焊盘上至少有 4*4 个 0.4-0.2mm 的过孔,以增强芯片的散热效果。

图 2.11 EPAD 焊盘上的散热过孔

图 2.12 PF8X00 建议焊盘孔排列

5. 如需具体的技术交流讨论,请在 大大通 上关注我,并给我留言。

三、参考文献

1. 《 AN5349_S32V234_Hardware_Design_Guide 》

2. 《 PF8x00 》

评论