目录

1. 概述

1.1 功能描述

配置 MPC5744P 各时钟,在 BMS 板子上,通过 Clock out 功能输出时钟信号。

大大购相关商品 DVK2002_NXP MPC5744P EVM >> 查询存货及售价

1.2 硬件开发工具

BMS 板子

PEmicro 烧录器

1.3 软件开发工具

S32 Design Studio for Power Architecture Version 2017 R1

1.4 相关程序工程

…/Code Examples/MPC5744P_02_ClockOut_Demo

2. 原理

2.1 内部原理

在 MPC5744P 里,对时钟的配置需要使用到 3 个模块:

- 时钟产生模块(clock generation module):MC_CGM

- 双路数字 PLL 接口(dual PLL digital interface):PLLDIG

- 模式控制模块(mode entry):MC_ME

时钟信号源分为:

1、内部时钟源(IRCOSC)为 16 MHz

2、外部时钟源(XOSC)可自行电路设计为 8-44 MHz (BMS 为 40 MHz)

3、PLL0 两路整数锁相环输出(需要软件配置,可达 200 MHz)

4、PLL1 单路小数锁相环输出(需要软件配置,可达 200 MHz)

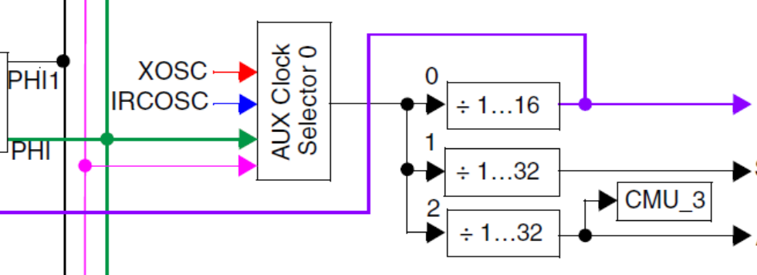

时钟产生的逻辑图中,AUX Clock Selector 为时钟源选择器,控制输送到选择器后面的模块的时钟源,部分选择器不是 4 种时钟源都能使用,请确认能不能选中。对应MC_CGM模块中寄存器为 ACx_SC (x=0,1,2…)。

后面分频器通过MC_CGM模块中 ACx_DCn/SC_DCn 来控制。

(System clock selector 需要通过 MC_ME 模块中的 xxx_MC 寄存器来控制,其中 xxx 为模式名(DRUN、RUN0、RUN1…))

PLL 时钟源的配置

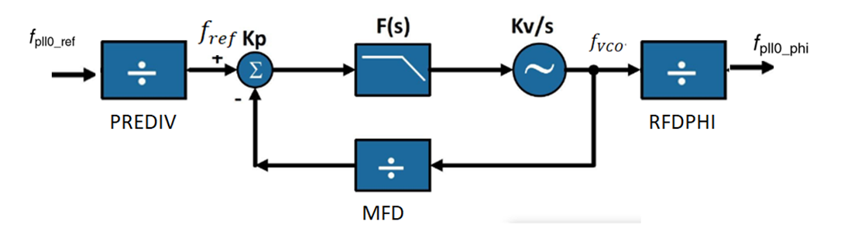

下图为 PLL 的原理图

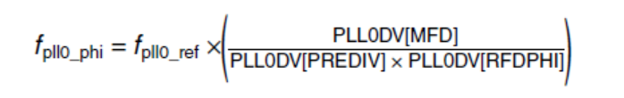

其中 PREDIV、MFD和RFDPHI 的值可以通过 PLLDIG 模块的 PLL0DV 和 PLL1DV 寄存器控制,PLL1 中可以在 MFD 值加入小数部分,通过上面的原理可以计算出,PLL0 稳态输出值与 PREDIV、MFD 和 RFDPHI 之间的关系如下:

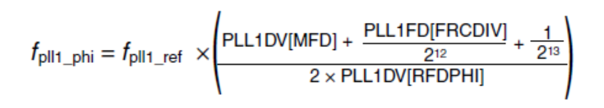

而在 PLL1 中,PREDIV 恒为 2,而 MFD 可以包含小数部分。则其稳态输出为:

每次改完 PLL 设置以后,通过 MC_ME 模块的 xxx_MC 来选择 PLL 的开关,并通过 MCTL 寄存器重新进入模式才能实现 PLL 的更新。

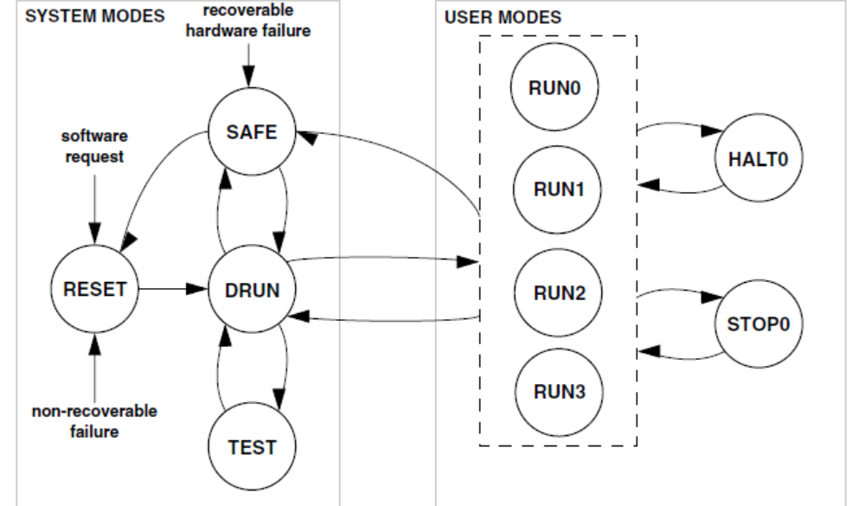

MC_ME 模式控制:

以上是 MC_ME 可选的模式,其中 HALT 和 STOP 模式为低功耗模式,RUN0-3 为用户普通使用模式,DRUN 为系统级使用模式(能操作 Flash),TEST/RESET/SAFE 是特殊功能的系统模式。

ME_MC 可以通过 PCTLn 寄存器来控制在该模式下能否使用某一外围功能(UART、SPI、PWM 等)。

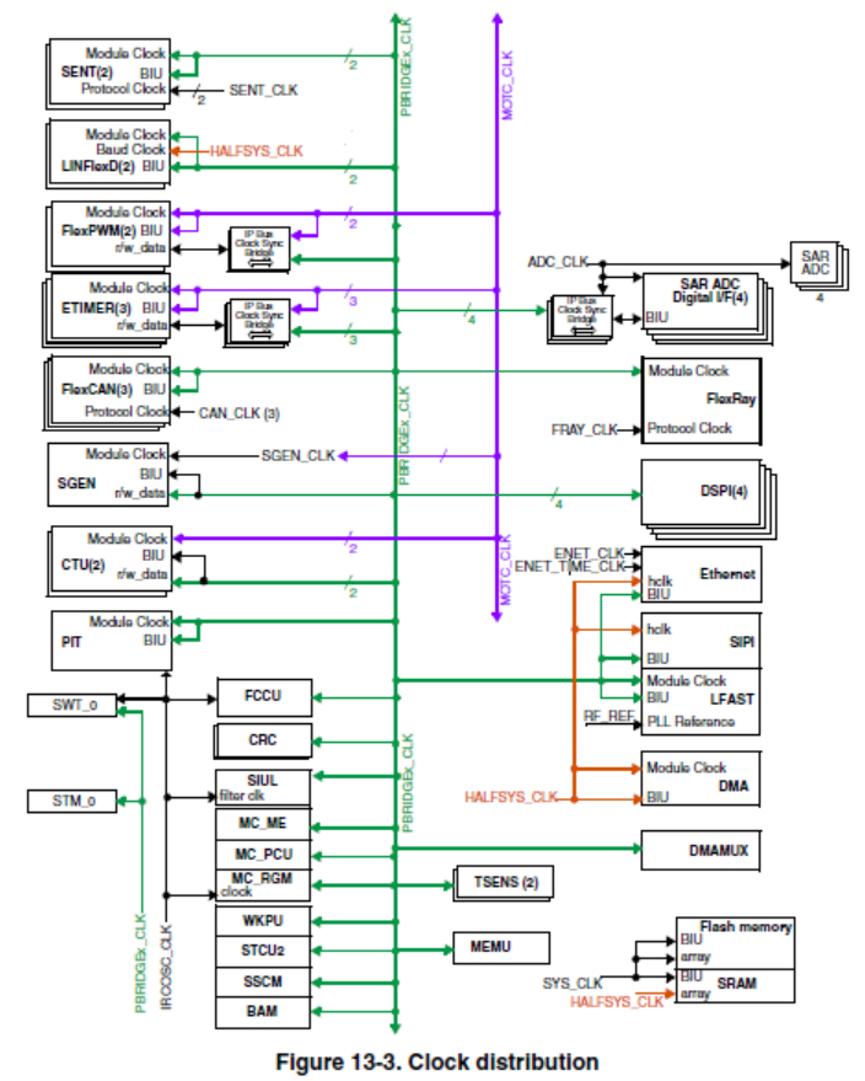

时钟产生的逻辑图:(高清图可在 MPC5744PPRM.pdf P337 & P347 中找到)

在 Figure 13-1.Clock generation 中可以通过配置时钟的输入源,在 MPC5744P 中,其输入时钟源来自于内部时钟(IRCOSC 16 MHz)或者外部的晶振(XOSC 8-40 MHz)。然后再通过两个锁相环(PLL0、PLL1)进行时钟倍频,以提升整个 MCU 的性能,其主频最高可以达到 200 MHz。

在 Figure 13-3.Clock distribution中体现了 MCU 中每个模组的时钟来源主要是以 PBRIDGEx_CLK 和 MOTC_CLK 为主;除此之外,模组正常工作还需要 Module Clock、r/w data、BIU 或者 Protocol Clock 等时钟的正常运作,而这些时钟主要来自于 XOSC、IRCOSC、PLL0、PLL1 这些时钟的倍频或者降频。

通过上面这两张图片尚的时钟跳动从而使这颗 MCU 处于正常的运算、计数、比较等等功能,通过软硬结合的方式来完成一次又一次的任务功能实现。

以 CLKOUT0 为例,为了使 CLKOUT0 输出 1 MHz 频率的时钟可以进行以下设计思路,在 AUX Clock Selector 6 选择 IRCOSC 为输入源时钟,IRCOSC 的时钟是 16 MHz,然后在预分频那里除以 16 就得到了 1 MHz 频率的时钟。

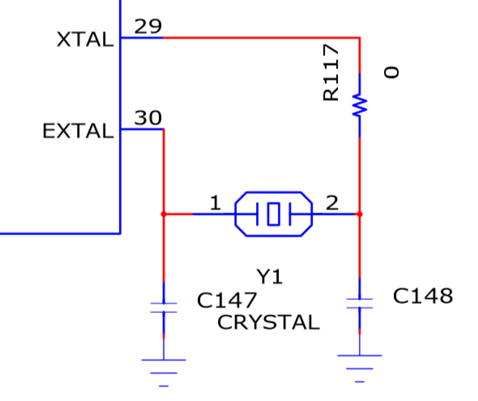

2.2 硬件原理

下图为 BMS 中的外部时钟源电路,其中晶振的频率为 40 MHz。

3. 程序功能描述

3.1 功能概述

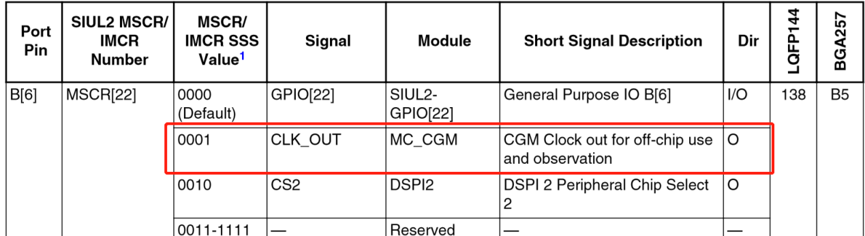

对 MPC5744P 的时钟进行分配,并将输出时钟 CLOCK OUT 设为 1 MHz,直接通过引脚输出时钟信号。对应引脚信息如下:

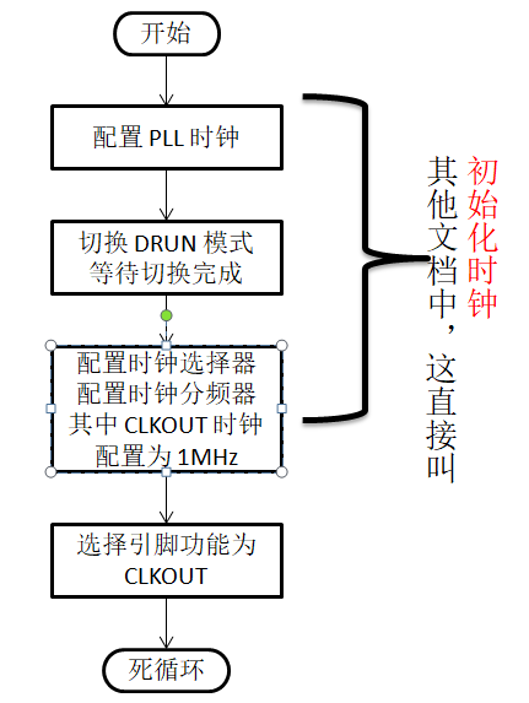

3.2 程序流程图

4. 相关函数介绍

4.1 MC_ME_Init

4.1.1 功能描述

本函数用于初始化时钟,配置如下。

系统时钟:160 MHz(PLL0PHI)

PBRIDGE: 40 MHz(SC_DC0)

CLKOUT0: 1 MHz(AC6_DC0)

MOTC_CLK: 5 MHz(AC0_DC0)

SGEN_CLK: 5 MHz(AC0_DC1)

ADC_CLK: 5 MHz(AC0_DC2)

CAN_PLL_CLK:40 MHz(AC2_DC0)

LFAST PLL: 40 MHz(AC5_DC0)

FRAY_PLL_CLK: 80 MHz(AC1_DC0)

SENT: 20 MHz(AC1_DC1)

ENET_CLK: 40 MHz(AC10_DC0)

ENET_TIME_CLK: 40 MHz(AC11_DC0)

4.1.2 API 原型

void MC_ME_Init(void)

5. 测试结果

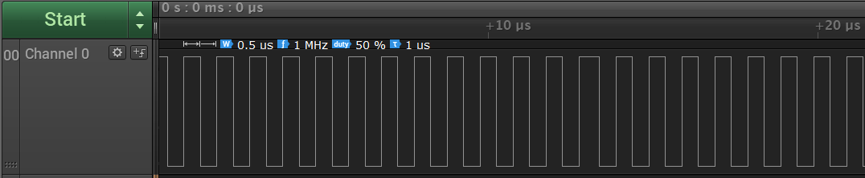

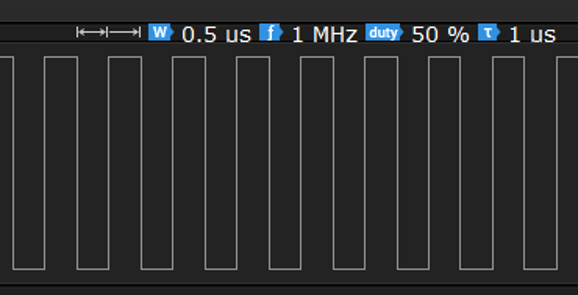

烧录代码运行后,使用逻辑分析仪抓取 B6 引脚的结果如下。

如图中所示,B6 引脚抓取出来为图示的时钟信号。

其中,它的频率符合设定要求的 1 MHz 时钟信号。

6. 参考资料

[1] MPC5744P Reference Manual,NXP Semiconductor Document Number: MPC5744PRM

评论