HDMI2.1 FRL (Fixed Rate Link) mode 運作原理

目前市面上HDMI主流標準是1.4b和2.0,對應支持的最大分辨率/刷新率分別是4K@30Hz和4K@60Hz。

隨著對更高分辨率和刷新率需求的增加,HDMI協會於2017年11月推出了HDMI2.1版本,增加了FRL(Fixed Rate Link)模式,

支援8K@60Hz和4K@120Hz。

FRL (Fixed Rate Link) Mode

FRL具體的變化:

1)HDMI接口的獨立時鐘信號改為嵌入在數據中,在接收端使用時鐘恢復單元恢復出時鐘;

2)用於傳遞音視頻數據的通道最多為4個,每個通道最高支持12Gpbs的速率;

3)編碼方式從8b/10b 變為16b/18b,編碼效率更高。HDMI接口形式沒有變化,

原來的TMDS Clock channel重定義為FRL lane3; TMDS Data 0/1/2 分別對應FRL lane 0/1/2,如下圖所示。

FRL模式,只有3 lanes 和4 lanes 工作模式, 3 lanes 工作模式下, 僅僅支持3 Gbps和6Gbps 兩種速率;

未使用的Lane3, source 和sink 都需要使用差分50Ω~150Ω端接(Termination) ;

4 lanes 工作模式下, 支持6/8/10/12 Gbps 四種速率。

HDMI2.1 Source和Sink的Link Training Procedure

Source首先要讀取Sink的EDID(EDID是I2C 地址為0xA0/0xA1,長度為256字節的存儲空間,包含Sink所支持的分辨率和最高速率等信息),

輸出sink所支援的分辨率/速率。Source不能輸出Sink EDID 未支援的分辨率/速率。支援HDMI2.1 的Sink,一定要在EDID 的HF-VSDB

對應字節把SCDC_Present 設置為1, Max_FRL_Rate 設置範圍是1到6,數字0代表不支援FRL 模式,其他值為保留值。在SCDC中把Sink version 設置為1。

Max_FRL_Rate 值具體含義如下:

=> 1 代表僅僅支持3 lanes 模式下的3Gbps 速率,其他速率和lane 配置不支援;

=> 3 代表支持3 lanes 模式下的3Gbps和6Gbps 速率;4 lanes 模式下僅僅支持6Gbps速率,其他速率不支援。其他數字的含義類推。

SCDC 是I2C地址為0xA8/A9的存儲空間, 用於Source和Sink溝通交換狀態和控制信息, 部分字節Source和Sink都可以讀寫。

與EDID不同, EDID對source是只讀的。HDMI2.1 Source和Sink溝通過程中,會使用到Sink version,Update Flags,Sink Configuration,Status Flags等信息。

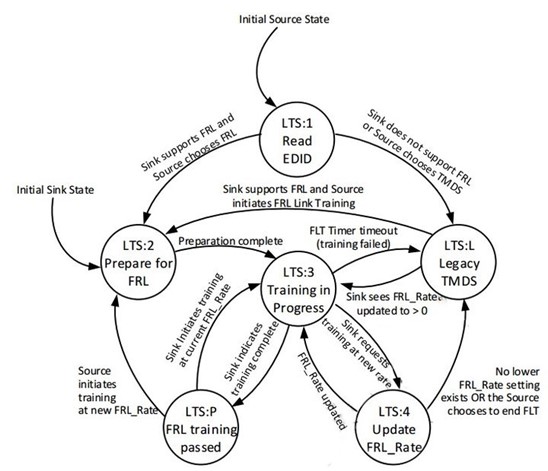

支援FRL 模式的Source和Sink首次建立連接,需要進行Link Training,更新FRL rate 也需要進行Link Training。

首次Training會依次經歷4個link training state (LTS):

|

LT state (LTS) |

Source Behavior |

Sink Behavior |

|

LTS:1 Read EDID |

讀取解析EDID後,判斷Sink 是否支援FRL mode 當滿足以下三個條件時,判定為支援: 1. FRL_Max_Rate>0 2. SCDC present=1 3. Sink version !=0 |

提供EDID 設定SCDC |

|

LTS:2 Prepare for FRL |

Source 反覆查詢,直到SCDC FLT_ready 為1,設定FRL_Rate 及 FFE level |

Sink 準備好Link Training 時,把SCDC FLT_ready設為1 |

|

LTS:3 Training in progress |

根據Ln(x)_Ltp_req暫存器,發出相對應的pattern,Ln(x)_Ltp_req=0 ,進入下一個LTS:P狀態 |

設定FRL_Start=0,並透過Ln(x)_Ltp_req暫存器,為每一lane請求pattern |

|

LTS:P FRL training pass |

開始FRL 傳輸,查詢FRL_Start=1時,才開始傳輸音視頻 |

檢測到FRL 傳輸後,設定FRL_start=1,並準備接收音視頻. |