對於恩智浦(NXP)的 i.MX 處理器系列中,與一 般微處理器(MCU)不同的,i.MX 處理器屬於效能強大的處理器(MPU)。i.MX 處理器的主板設計,需要額外的的DDR,來當作暫存與資料運算。因此,i.MX 處理器的與DDR之間的溝通,就特別的重要。

針對i.MX 處理器,恩智浦(NXP)了解DDR的重要,在設計主板時,特別重視DDR的Layout。因此在設計之前,一定要求設計者一定要遵守每一系列的i.MX 處理器的開發指南(Development guide):

1. 主板疊構(Stack) 2. 佈局指南(Layout Guide) 3. DDR 訊號模擬(SI)

除此之外,恩智浦(NXP)也提供一個軟件工具"DDR Stress Test Tool",讓開發者可以透過這個軟件,來驗證已完成的開發版與DDR溝通的效能。

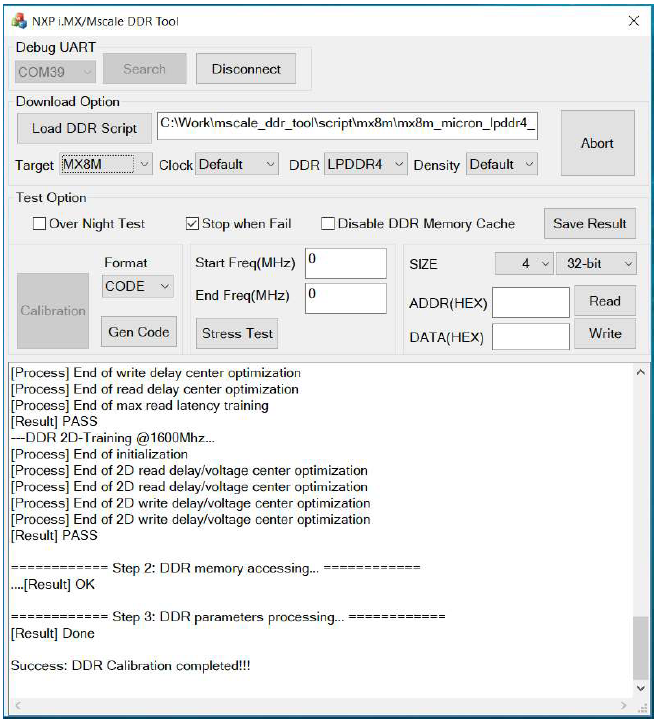

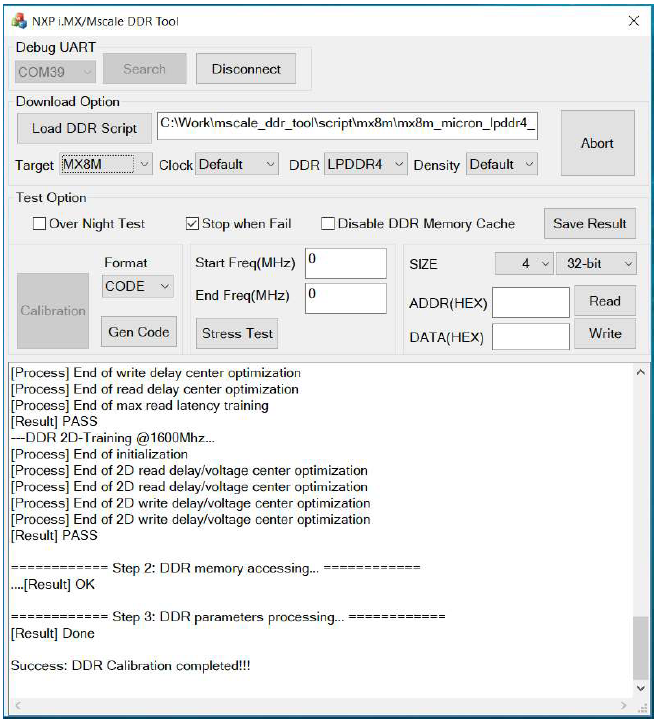

舉例i.MX8M "DDR Stress Test Tool" 如下:

使用方法可以參考 https://community.nxp.com/t5/i-MX-Processors-Knowledge-Base/i-MX-8M-Family-DDR-Tool-Release/ta-p/1104467

除了依照恩智浦(NXP)提供的測試方法之外,在這我們將教導大家基於DDR Stress Test Tool,執行更深入"極限"的DDR Stress test。

這個方式即:在DDR Stress Test Tool下,設定不同的測試電壓(SOC/DDR)

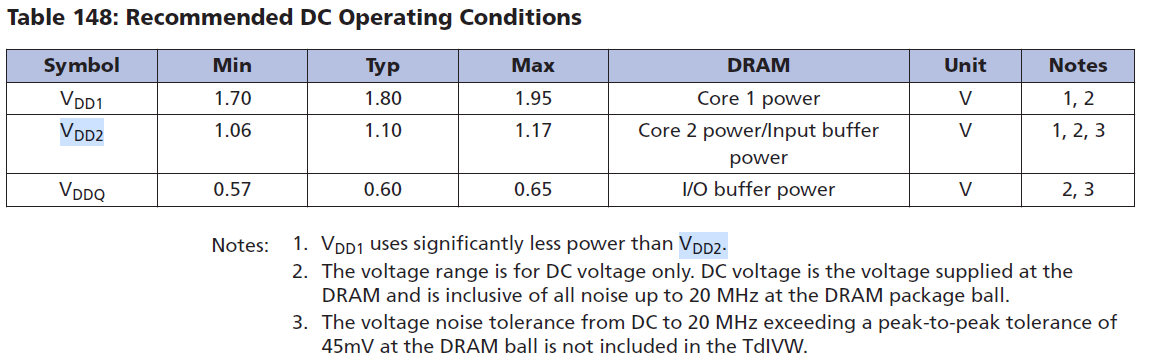

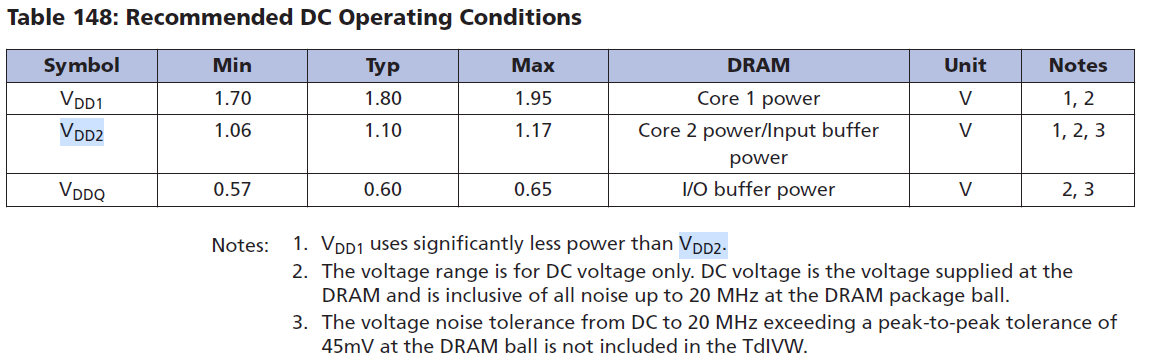

1. DDR 不同電壓的設定:舉例來說 LPDDR4的推薦的電壓為1.1V (Recommended)。但是其實在每個LPDDR4的電壓都可以接受一個範圍 1.06V(Min)~1.17V(Max)

針對i.MX 處理器,恩智浦(NXP)了解DDR的重要,在設計主板時,特別重視DDR的Layout。因此在設計之前,一定要求設計者一定要遵守每一系列的i.MX 處理器的開發指南(Development guide):

1. 主板疊構(Stack) 2. 佈局指南(Layout Guide) 3. DDR 訊號模擬(SI)

除此之外,恩智浦(NXP)也提供一個軟件工具"DDR Stress Test Tool",讓開發者可以透過這個軟件,來驗證已完成的開發版與DDR溝通的效能。

舉例i.MX8M "DDR Stress Test Tool" 如下:

使用方法可以參考 https://community.nxp.com/t5/i-MX-Processors-Knowledge-Base/i-MX-8M-Family-DDR-Tool-Release/ta-p/1104467

除了依照恩智浦(NXP)提供的測試方法之外,在這我們將教導大家基於DDR Stress Test Tool,執行更深入"極限"的DDR Stress test。

這個方式即:在DDR Stress Test Tool下,設定不同的測試電壓(SOC/DDR)

1. DDR 不同電壓的設定:舉例來說 LPDDR4的推薦的電壓為1.1V (Recommended)。但是其實在每個LPDDR4的電壓都可以接受一個範圍 1.06V(Min)~1.17V(Max)

在一般的條件下,LPDDR4的電壓的都會設定在1.1V,為LPDDR4的中心電壓。

在此為了達到LPDDR4的極限測試,我們可以嘗試將LPDDR4的電壓設定在最小值(MIN)的1.06V或是最大值(MAX)的1.17V,在這樣的測試過程中,可以了解這塊開發版在LPDDR4的極限。

設定方法:

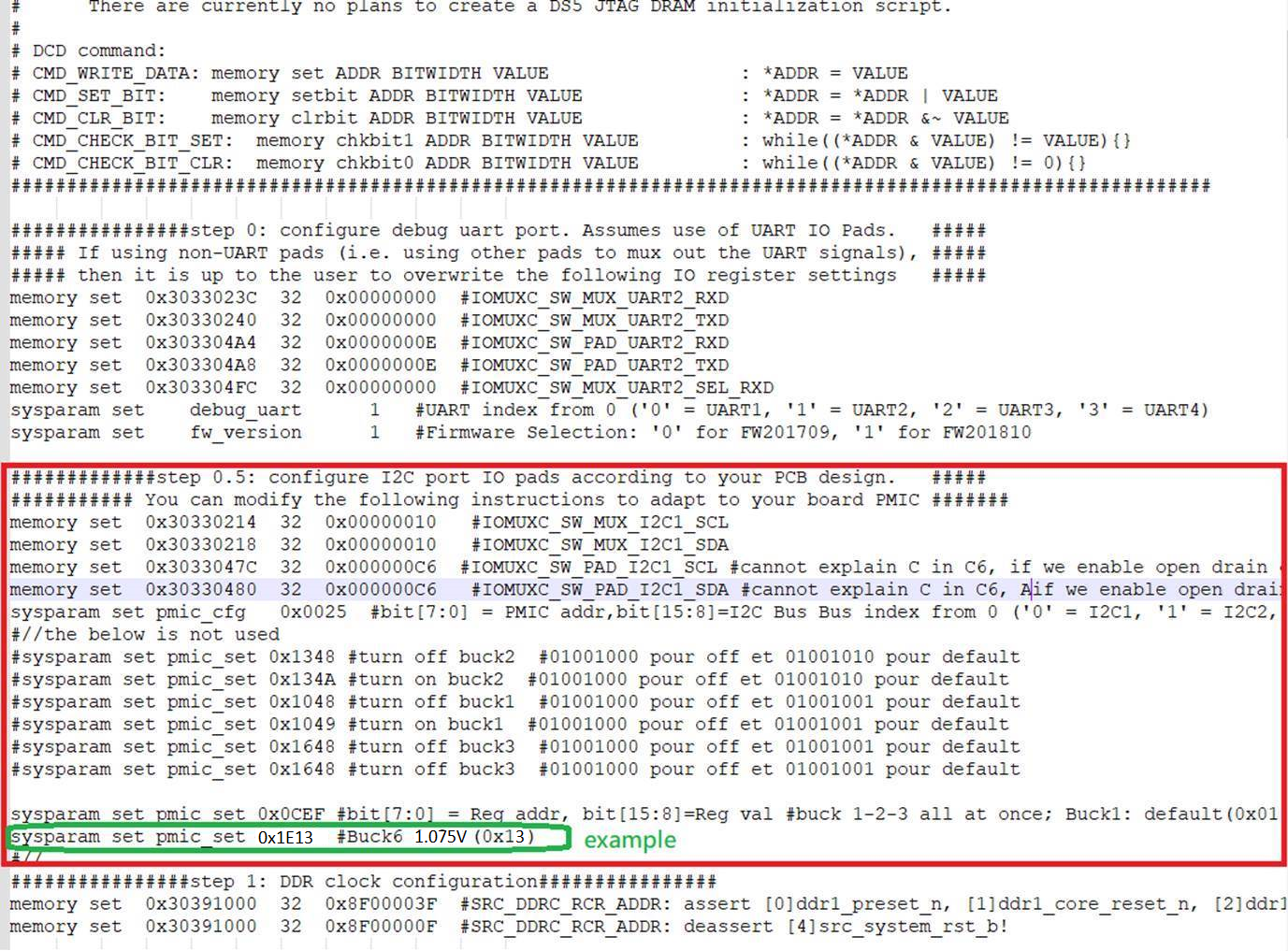

1. 打開 DDR Stress Test Tool中的Script file,例如i.mx8m nano搭配LPDDR4的Script file"mx8mn_micron_lpddr4_2gb_2d_1600m_200m_50m_2cs_RPAv3.ds"

2. 在Script file中加入針對LPDDR4的電壓調整參數(透過I2C,調正PMIC"PVA9450B"的電壓輸出至LPDDR4)

由以上的方法,就可以驗證LPDDR4在電壓為1.075V(低電壓)的情形下的極限測試。

同理,我們也可以依照此方法,將PMIC的BUCK6設定值,設為 0x16, LPDDR4在電壓為1.15V(高電壓)的情形下的極限測試。

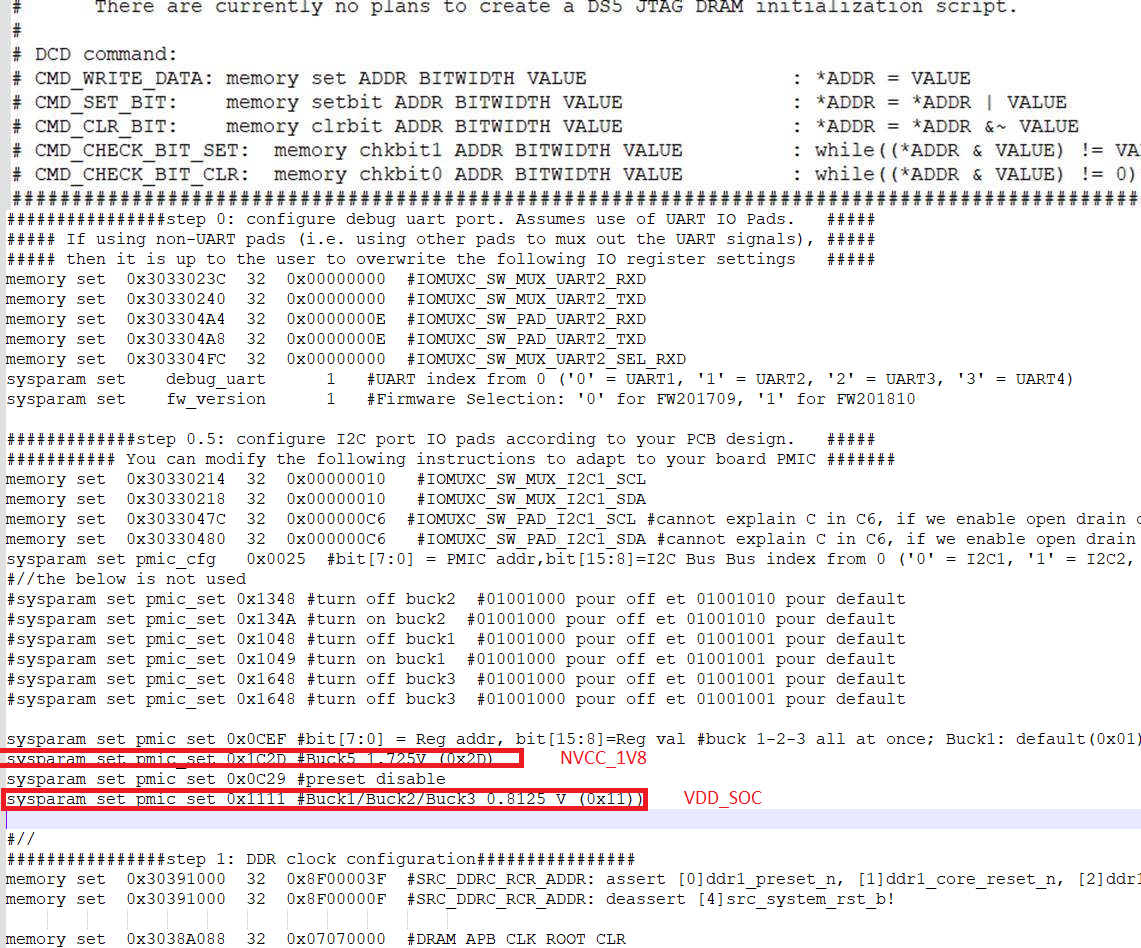

3. 針對i.MX8M系列,也可以運用此方式調整其電壓,進行壓力測試。

由以上的方法,就可以調正 i.MX8M Nano每一組電源的電壓。

如上圖 將PMIC的BUCK5設定值,設為 0x2D, 將.MX8M Nano 在NVCC_1V8的電壓改為1.725V(低電壓)的情形下的極限測試。

將PMIC的BUCK1設定值,設為 0x11, 將.MX8M Nano 在VDD_SOC的電壓改為0.8125V(低電壓)的情形下的極限測試。

評論