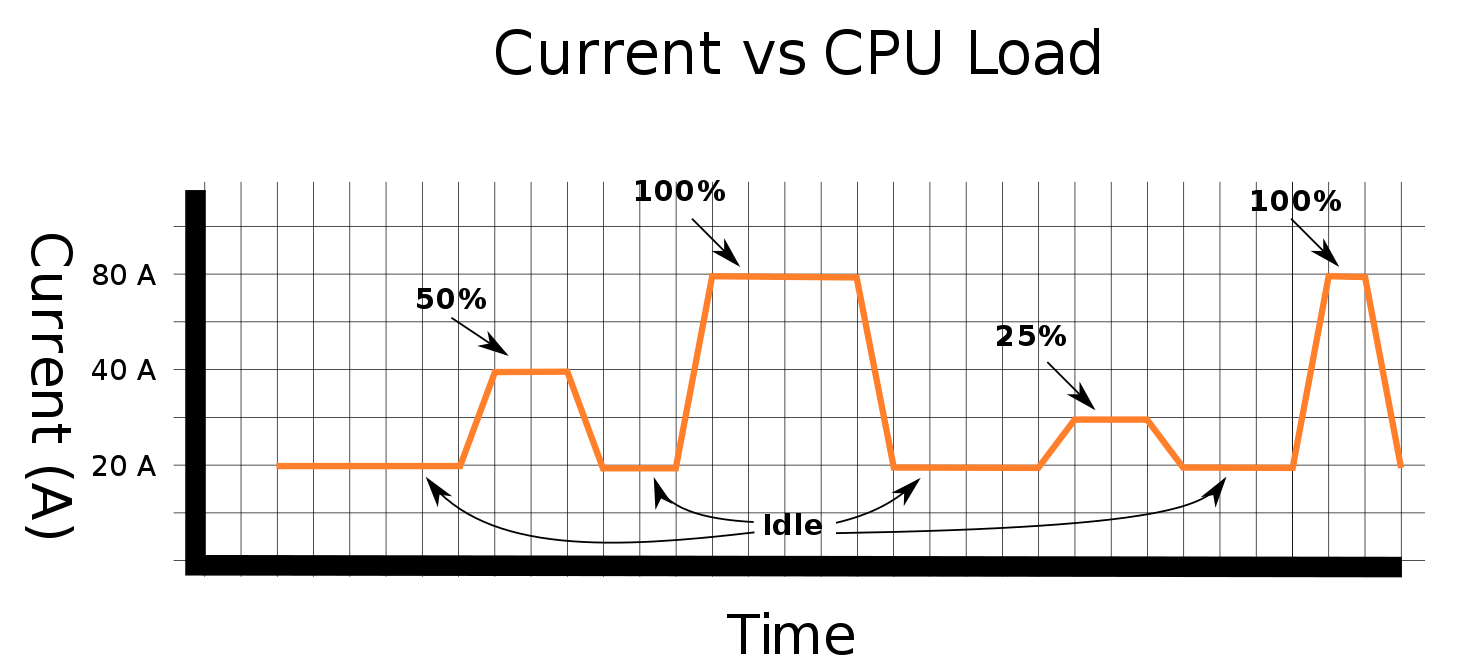

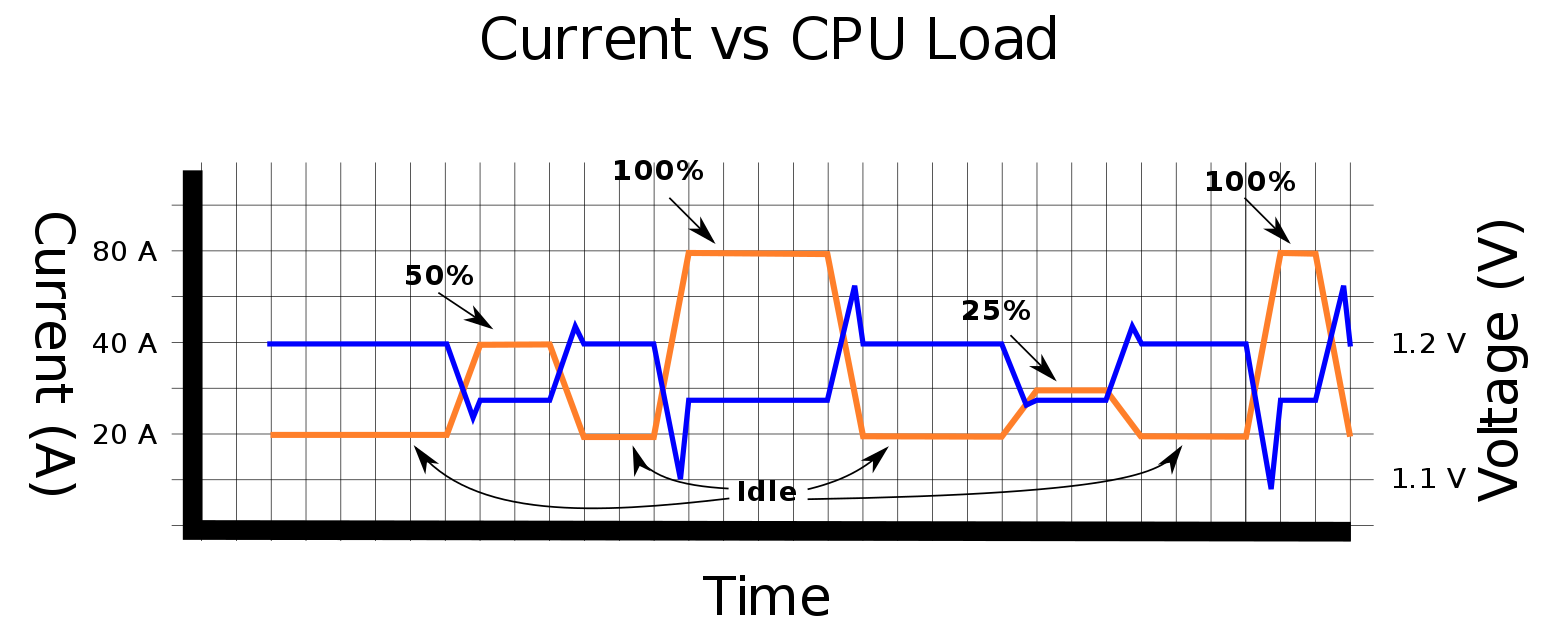

現代計算機系統永遠不變。 為了提高效率和性能,CPU將在非常低和非常高的時鐘頻率之間跳變,具體取決於正在執行的工作負載的要求。 當CPU正在競爭睡眠時,這通常可以非常迅速地完成。 當沒有任何有效執行且CPU空閒時,電流也相對較低。 但是,當CPU負載不足且頻率上升時,電流也會上升。 示例圖如下所示。

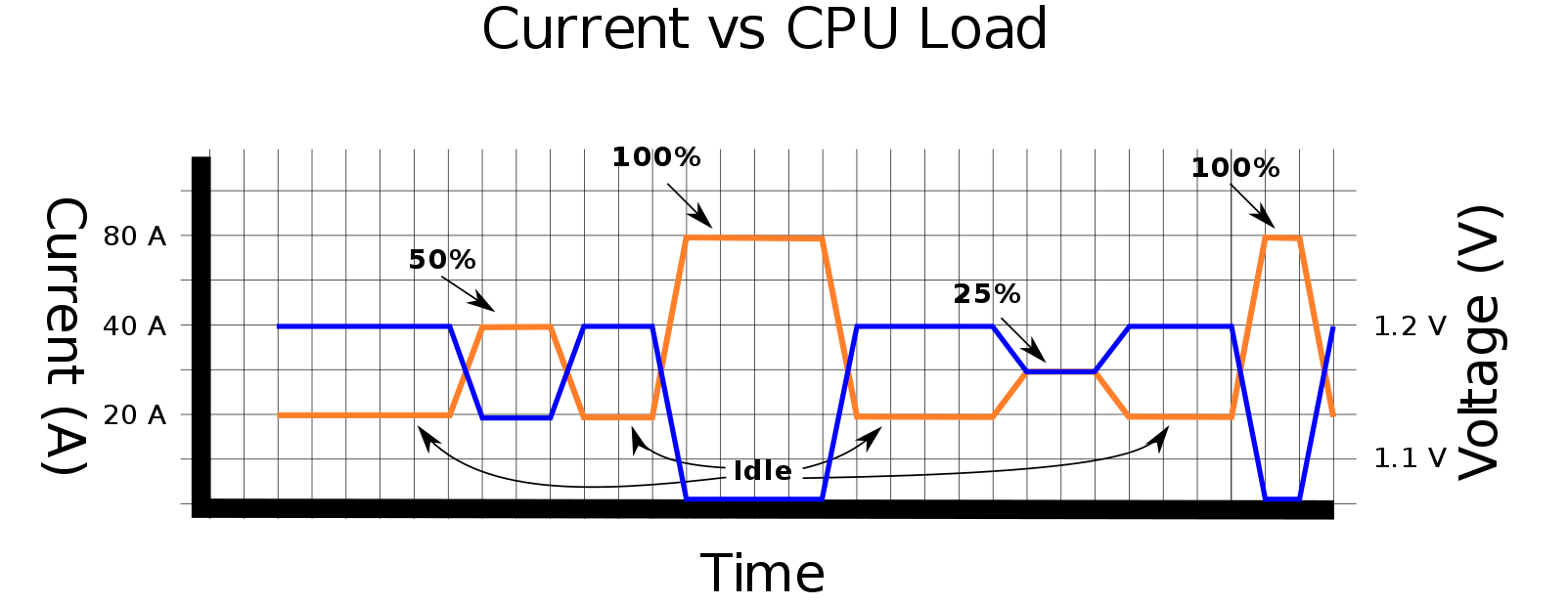

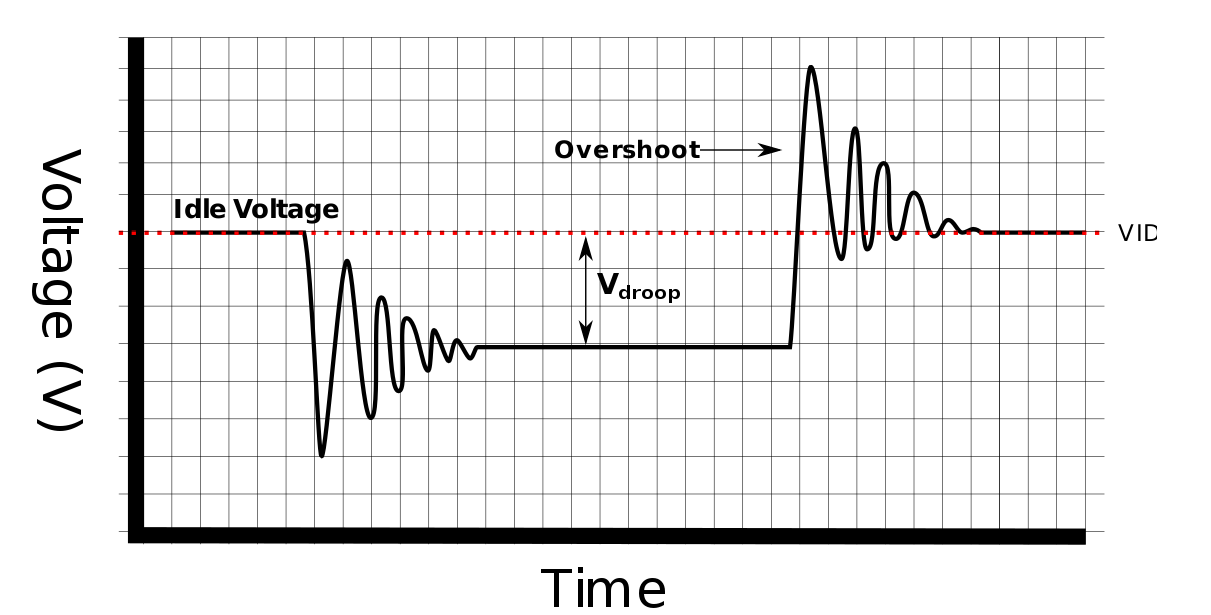

在具有靜態POn的系統上,具有驅動電壓調節器模塊的靜態PWM控制器的系統,存儲的能量是恆定的。 當系統從空閒進入負載時,沒有足夠的能量來維持預定電壓,從而導致電壓下降。 例如,以恆定的10%佔空比工作的VRM在空閒時提供1.2 V,

如下所示:

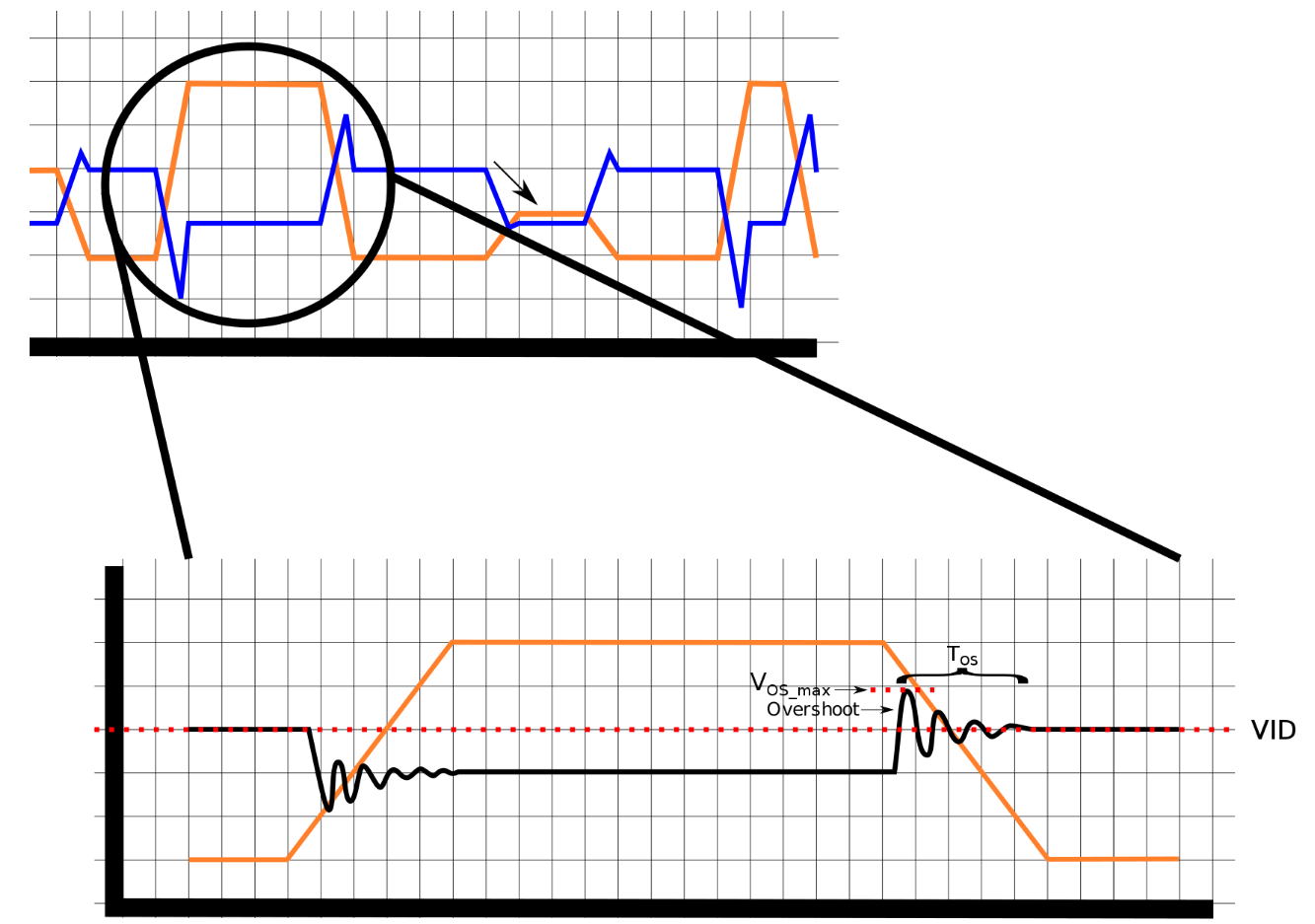

為了防止這種下降,大多數現代VRM都有某種形式的反饋用於感應電壓和電流。 當發生這種情況時,電路會嘗試通過調整佔空比來對其進行補償。 例如,假設先前顯示的VRM在檢測到跌落時從10%動態調整為12%佔空比,

電壓變化看起來與此類似:

可以看出,負載電壓現在比以前好得多,可以保持穩定的電壓,適用於理想和負載時的電壓。

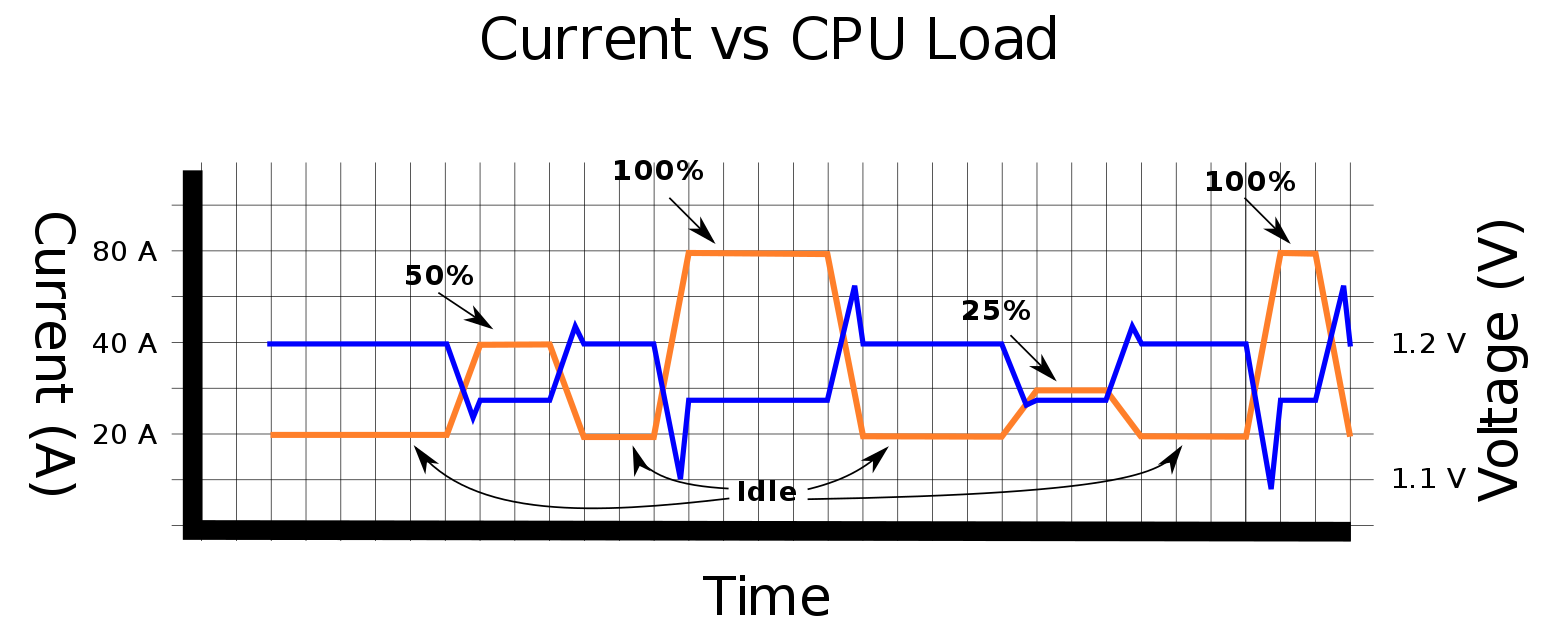

這種技術存在明顯的問題,即過度使用。 當PWM控制器檢測到增加的負載和電壓降時,它將嘗試通過增加佔空比來補償它。 然而,當處理器返回空閒狀態時,由於控制器無法預測未來,因此將存在延遲,直到PWM檢測到另一次下降並重新調整佔空比。

因此,在負載電流下降的短時間內,電壓會出現尖峰。

電壓變化看起來與此類似:

可以看出,負載電壓現在比以前好得多,可以保持穩定的電壓,適用於理想和負載時的電壓。

這種技術存在明顯的問題,即過度使用。 當PWM控制器檢測到增加的負載和電壓降時,它將嘗試通過增加佔空比來補償它。 然而,當處理器返回空閒狀態時,由於控制器無法預測未來,因此將存在延遲,直到PWM檢測到另一次下降並重新調整佔空比。

因此,在負載電流下降的短時間內,電壓會出現尖峰。

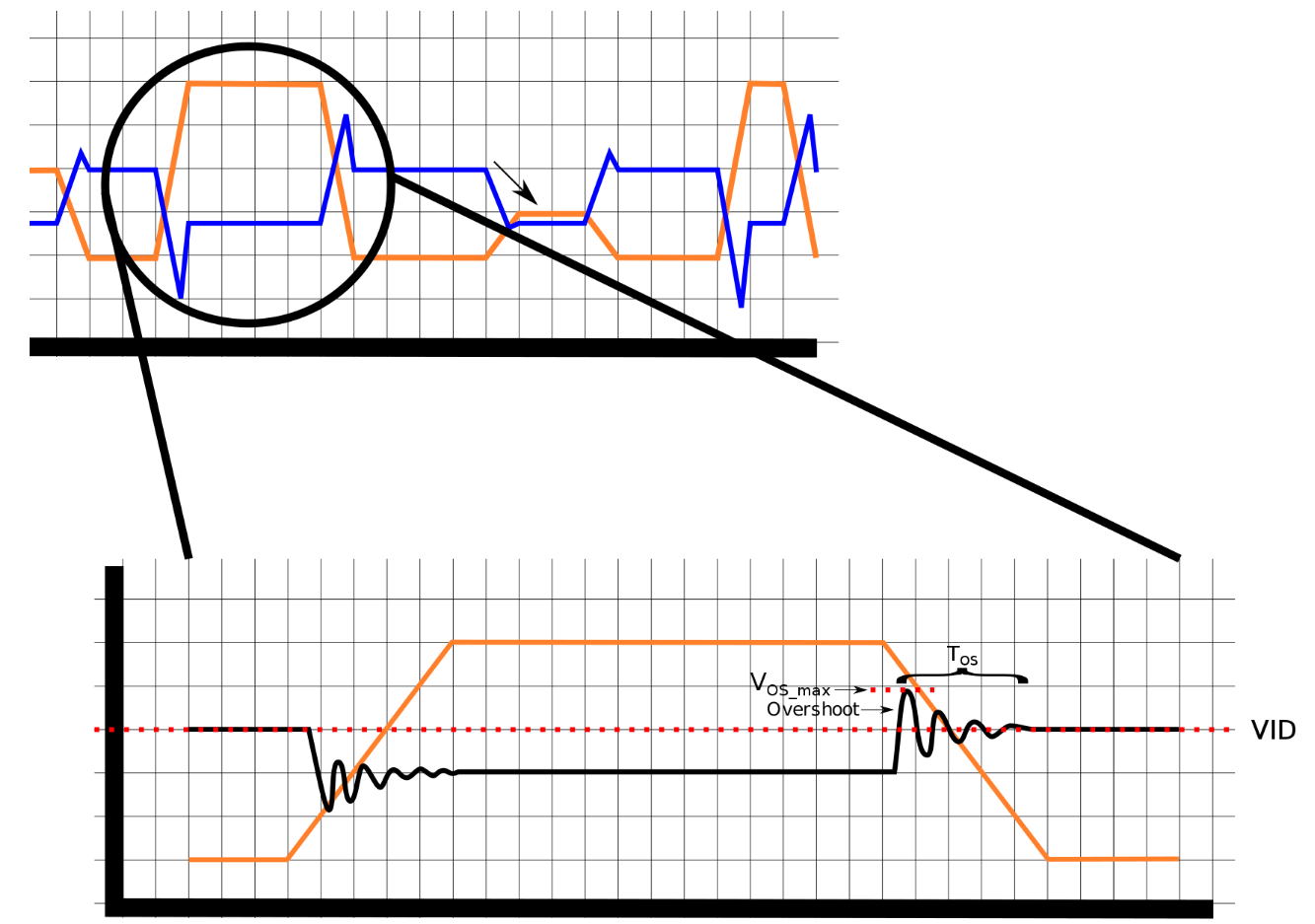

這種稱為過衝的尖峰超過了所需的參考電壓。 電壓尖峰太大會降低芯片上的晶體管。 極高的電壓會導致晶體管的災難性故障。 英特爾等公司發布了VRM規範,規定了允許的最大過衝電壓(VOS_max)以及允許的持續時間(TOS)。

由於主板製造商不能超過這些額定值,因此在超過這些額定值之前,他們可以更改佔空比的高度存在限制。 因此,VRM具有一定量的Vdroop是很自然的,以確保它們不會超過允許的過衝電壓。

換句話說,故意添加Vdroop以防止對CPU有害的電壓過衝。

減少過衝

有多種方法可以減少現代系統的過衝。 最簡單的方法是使用能夠儲存更多能量的更大的組件 - 儘管這會起作用,但效率會降低。 更好的方法是可以增加PWM控制器的頻率和採樣率。 隨著採樣率的提高,它可以在峰值激增之前更快地補償電壓尖峰。

值得指出的是,增加開關頻率會影響電路 - MOSFET需要能夠跟上頻率,同時非常高端的PWM控制器也變得太昂貴而無法在主板上使用。 最終,設計決策歸結為妥協。

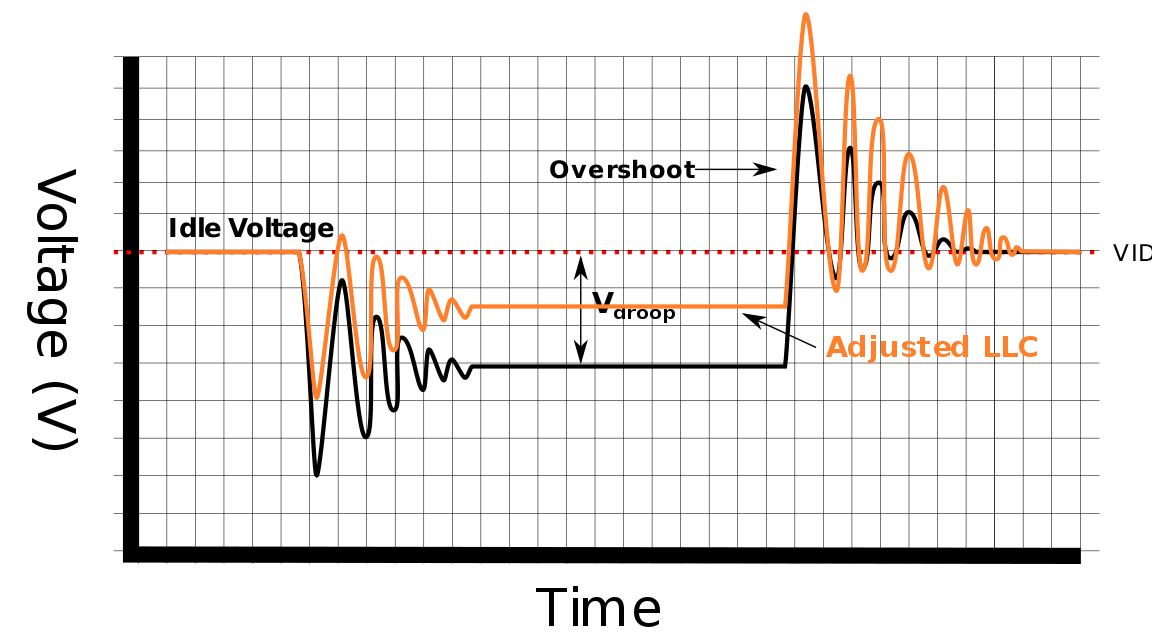

負載線校準

超頻系統可能使用相對較高的電壓設置。 當空閒電壓較高時,CPU在滿載期間電壓下降本身較大。 為了防止由於超頻引起的大電壓下降導致的系統不穩定,許多主板都帶有負載線校准設置。 施加LLC電壓將允許VRM在感測到更高負載時施加更高的電壓。 換句話說,LLC調整VRM從完全空閒到滿負載時預期會遇到的Vdroop數量。

值得注意的是,LLC對過衝電壓有非常顯著的影響,因此通常最好保證LLC偏移電壓的施加量。 確切的影響和過衝將在很大程度上取決於主板以及PWM和VRM電路以及它們對電壓和電流變化的感知和反應。

一個良好的PWM,速度快,反應良好,可以在達到最大過沖之前足夠快地調整,從而進一步調整LLC。 選擇正確的配置在很大程度上取決於主板的功能。

有些主板提供“極端”或“超高”LLC設置,實際上會提供比理想情況更高的電壓,導致高過衝(取決於主板)。

一般來說,除了極限超頻玩家(例如,LN2超頻玩家,禁用C狀態的人等等)之外,沒有人應該使用這個。

評論