對於高速訊號,PCB 的設計要求會更多,因為高速訊號很容易受到其他外在因素的干擾,導致實際設計出來的東西和原本預期的效果相差很多。

所以在高速信號PCB設計中,需要提前考慮整體的佈局與布線,良好的佈局可以很好地決定布線的走向和結構,電源與地之間的分割,以及電磁干擾和噪聲的控制。

不過在理解高速PCB設計之前,需要知道什麼是高速信號。

一般如果符合以下幾點,那它就可以被認為是高速信號(Cadence公司所做的定義):

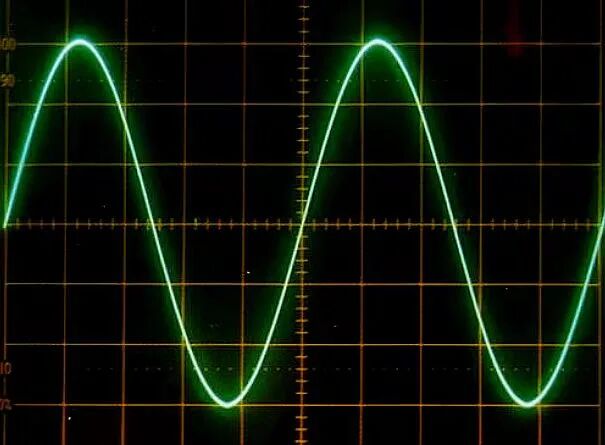

頻率大於50MHz的信號,就是高速信號

(2)信號是否為高速不僅僅取決於頻率,而是當信號的上升/下降沿小於50ps時,就認為是高速信號。

(3)當信號沿著傳輸路徑傳輸時,若發生了嚴重的趨膚效應(電流集中在導線外表薄層的現象)和電離損耗,就認為是高速信號。

在佈局之前,首先必須清楚系統原理圖,將各個電路進行劃分,比如分為數位、類比、混合數位類比,特別注意各晶片電源和信號引腳的位置擺放。

在劃分完各部分電路之後,初步規劃數位電路、類比電路之後的佈線區域,讓各部分電路至少盡量相互遠離。在實際中的佈局,也會有先後順序,依次是混合型元件==>類比元件==>數位元件==>旁路電容。

數位電路部分和類比電路部分一定要分開,那混合數位類比電路部分要放哪裡?

它通常需要放置在數位信號區域和類比信號區域的交界處。

所以在擺放時,數位部分的引腳盡量靠近數位電路部分,模擬部分的引腳盡量靠近模擬電路部分。

對於用來產生特定頻率的晶振,應盡量將相關晶振電路放置在其驅動器件旁。為了保證時序信號的正常,因此需要確保在下一個時鐘週期到來之前,前一個數據能夠穩定地傳輸並被讀取。

噪聲是電路設計中常見的現象,在高頻高速信號設計中,對於對噪聲敏感的元件要遠離高速信號。

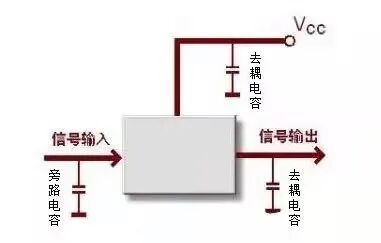

旁路電容通常用來濾除混有高頻電流和低頻電流的交流電中的高頻成分,因此在設計旁路電路時,應盡量將其靠近電源引腳放置,特別是對於高頻電路。此外,在電源接口附近放置大容量電容,可以穩定電源並降低噪聲干擾。

良好的佈局可以為PCB的佈線帶來事半功倍的效果。

--------------------------------------------------------------

轉載自MPS官網

評論