隨著電動汽車動力總成和能源基礎設施對碳化矽(SiC)功率元件需求的增加,市場增長得以加速。在這一過程中,終端用戶需求的不斷提高以及日益增大的盈利壓力促使各企業在其電力電子應用中考慮採用SiC溝槽技術(Trench)MOSFET,部分原因是基於傳統矽功率元件的經驗,認為溝槽技術是實現最佳功率密度的唯一途徑。然而,在決定溝槽技術是否為當前合適選擇之前,至關重要的是要考慮下一代SiC MOSFET技術的進步,這些技術很可能會帶來好處,同時避免其固有風險。

在電力電子應用中,平面技術(Planar)和溝槽技術(Trench)的關鍵差異

在電力電子應用中,功率密度固然重要,但可靠性同樣至關重要,甚至在某些應用中可能更為關鍵。儘管工程師通常專注於性能限制問題,但那些可能導致計劃外停機或維修的實際故障則較難被接受,因為它們可能對業務產生不可預見的重大影響。因此,溝槽技術的潛力需要進行更全面的評估。雖然溝槽技術有望成為電力電子工程工具箱的標準配置,事實上也已經被採用,但採用這種技術的人對其提供可靠性能的能力仍抱有相當多的「大膽一試」的想法。

在半導體生產的典型研發過程中,實現工藝的全面優化需要相當長的時間。故障可能來自意想不到的原因,而且可能要等到大量元件在現場部署數月乃至數年後才會顯現出來。溝槽技術正在開闢新的道路,而基於相對有限的現場經驗,供應商對可靠性的預測往往無法得到充分的驗證。

相比之下,眾多供應商在平面技術方面累積了數十年的行業經驗,為其性能和耐用性提供了有據可查的廣泛依據。換句話說,在當前發展階段,溝槽技術相較於其他方案仍然具有更大的風險。。

溝槽技術供應商正在努力尋找既能提高管芯(unit cell)密度,又能保持高可靠性的設計。

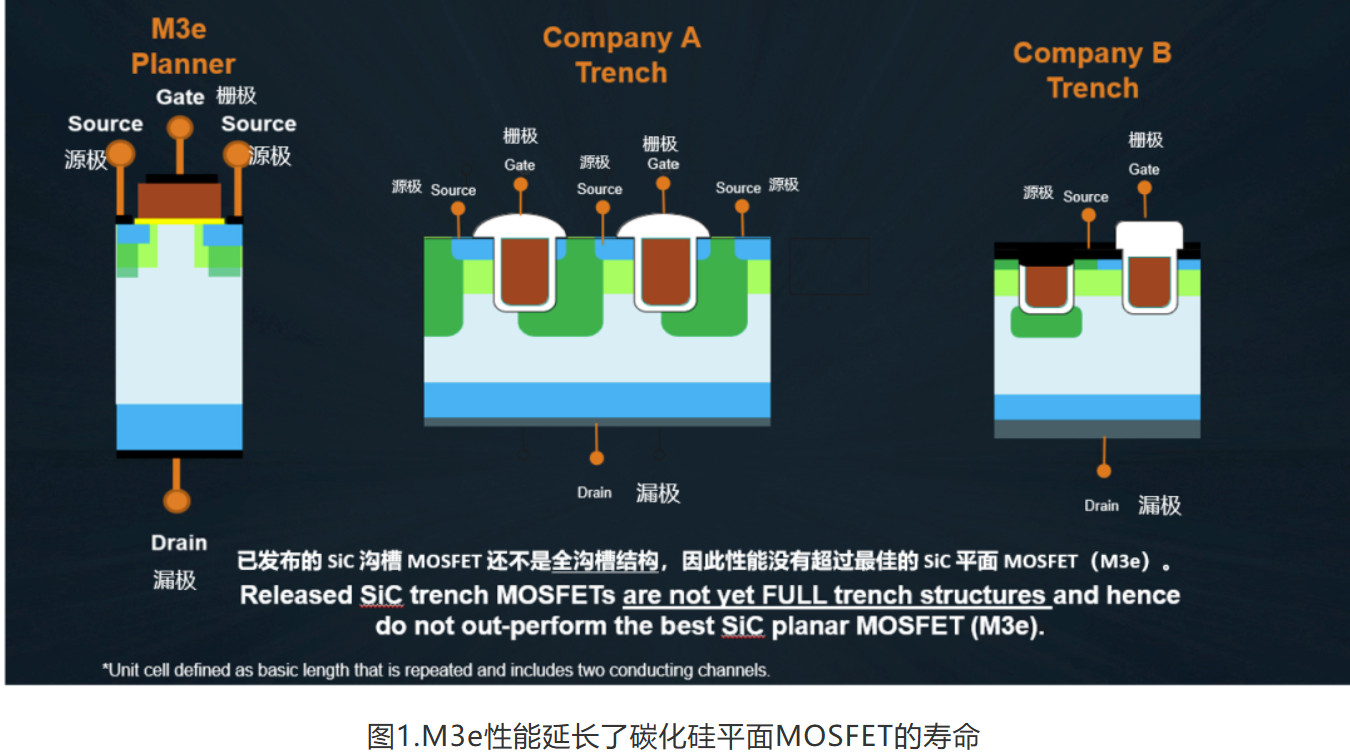

溝槽技術的基本問題之一(如上圖左側所示)是溝槽底部的強氧化物電場。當MOSFET阻擋高壓時,該電場會從相鄰的強電場SiC放大。此外,溝槽底部拐角處的氧化物變薄和場擁擠效應也加劇了這一現象。這不是一個孤立的問題,而是業界一直面臨的挑戰。

一個解決方案的例子如中間圖片所示,該圖例展示了A公司的第三代溝槽技術。A公司通過在柵極溝槽兩側增加源極溝槽,並將保護性的p層下沉至SiC n漂移層內,從而解決了氧化物的難題。這些額外的源極溝槽使得晶片間距增大,實質上犧牲了溝槽的優勢,因此在給定面積下,其原始性能相較於最佳的平面MOSFET而言略遜一籌。溝槽電流利用率是評估SiC溝槽MOSFET性能的重要因素。

B公司的M1產品和A公司的第四代技術將溝槽利用率提高到50%,這代表了商業應用的SiC溝槽技術的最新水平,並逐漸接近最佳平面SiC MOSFET的性能。為了使SiC溝槽MOSFET的性能超越平面結構,溝槽電流利用率必須達到100%。

當前平面技術(Planar)的優勢

安森美(onsemi)如何打破維度壁壘,將成熟的平面技術提升到一個新的水平?

安森美在將溝槽技術作為自己「路線圖」上的一條重要技術路線的同時,還採取了兩條並行的策略來實現這一目標。一方面,安森美致力於攻克溝槽技術面臨的各項技術難題;另一方面,通過在非常成熟的平面技術基礎上進行深化研發,不斷提升性能,以實現與溝槽技術相當的性能。

平面元件建立在安森美公司及整個行業數十年的全球製造經驗基礎之上。這意味著平面元件比其他替代方案具有更高的性能、穩定性和可靠性。整個平面供應鏈經過不斷優化,以實現最佳效果。溝槽技術很可能最終達到這一水平,但目前相對較新,在實際應用中的長期部署案例還很有限。

另一個需要考慮的因素是從矽基板到SiC的過渡。大多數客戶都是第一次使用SiC,可能沒有意識到這種材料的可靠性風險更高。在矽基板平面MOSFET中,氧化物與矽結合在一起,這種界面已經過廣泛的研究和設計。在平面SiC中,頂部矽層發生氧化的情況與矽基板有一定程度的相似性。而對於溝槽SiC,碳在氧化過程中起著不可忽視的作用——這是一種不同的、更具挑戰性的情況,可能會導致界面形成物理上的鋸齒狀區域,從而可能導致電氣問題。對於許多供應商來說,這仍然是一個有待時間、豐富的現場經驗和工程驗證才能明確解決的問題。

正在採用平面技術製造,計劃向溝槽技術過渡

除了關注溝槽技術的可靠性之外,對於安森美來說,無論是從系統級的每安培成本還是每千瓦成本的角度來看,平面器件都具有成本優勢。

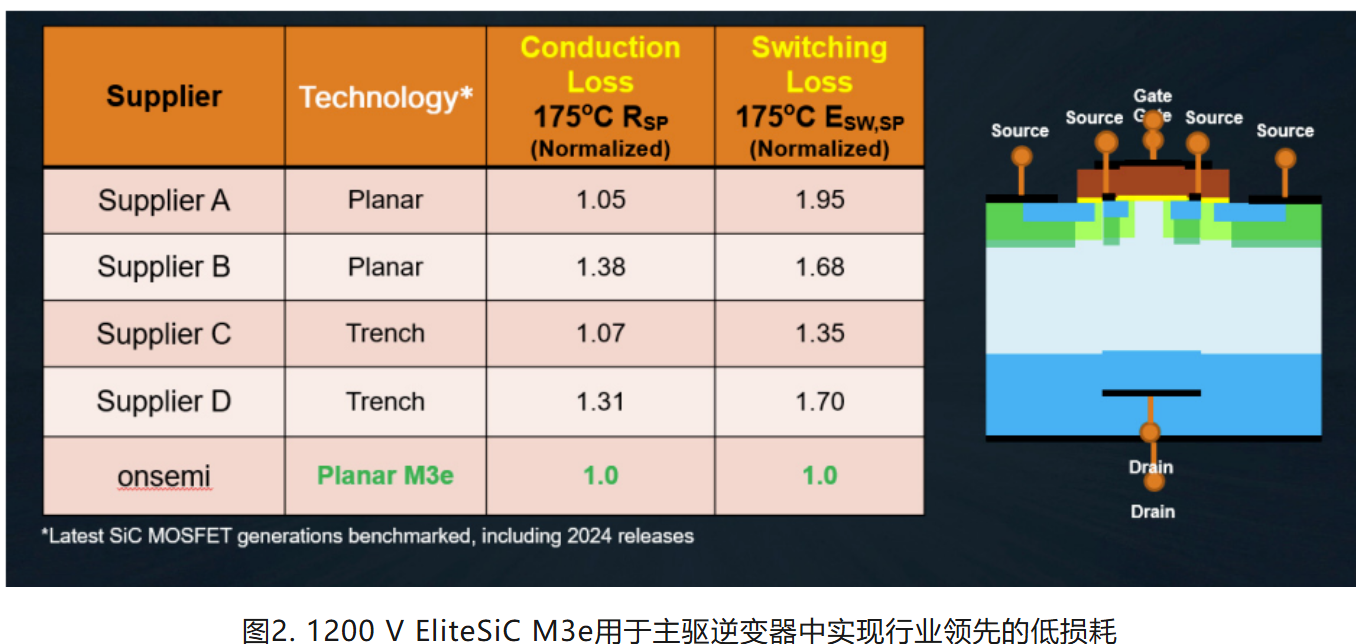

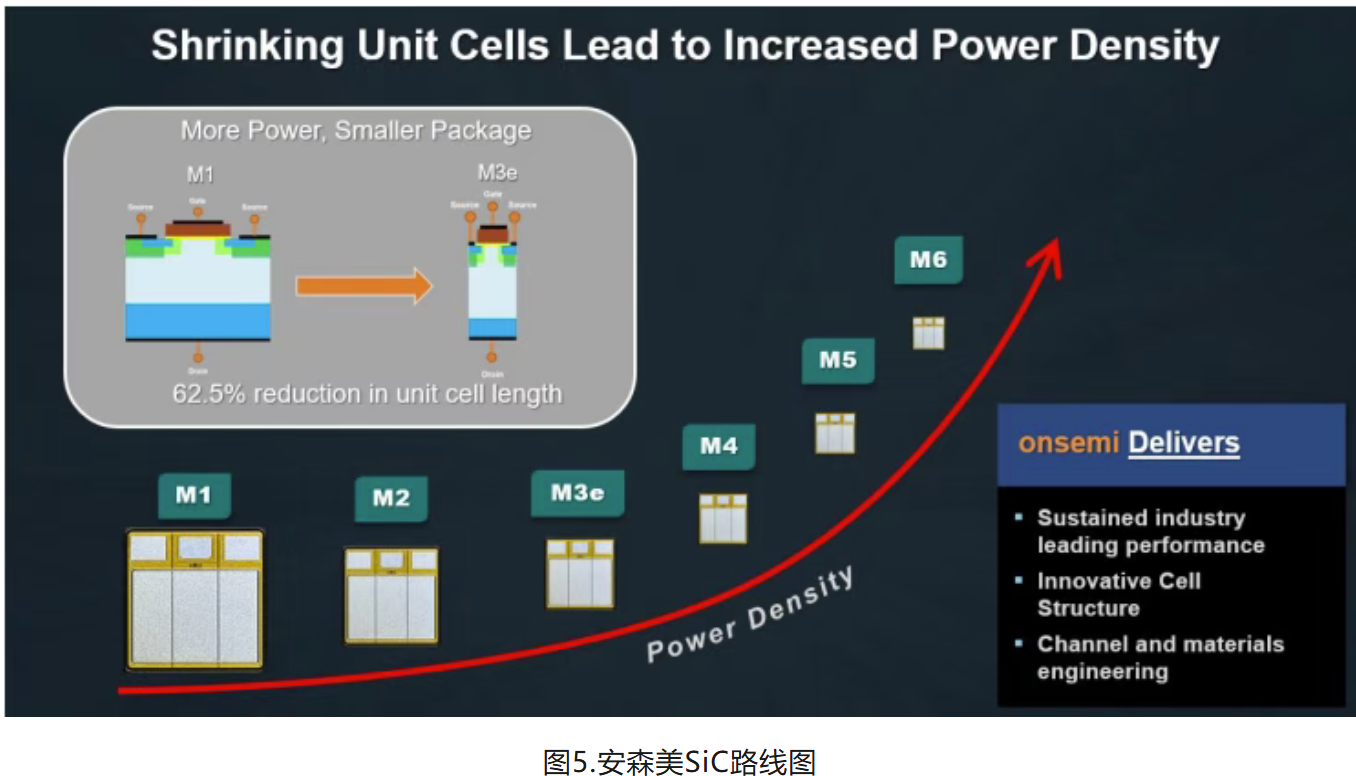

安森美EliteSiC MOSFET在溝槽技術上的路線圖始於M1/M2平面技術、方形/六邊形晶片元件。隨後推出的M3T和M3S平面技術、條紋晶片、薄晶圓技術顯著降低了晶片尺寸。不久前,安森美推出了...1200 V M3e採用了業界領先的薄晶圓平面技術,進一步適度減小了晶片體積。

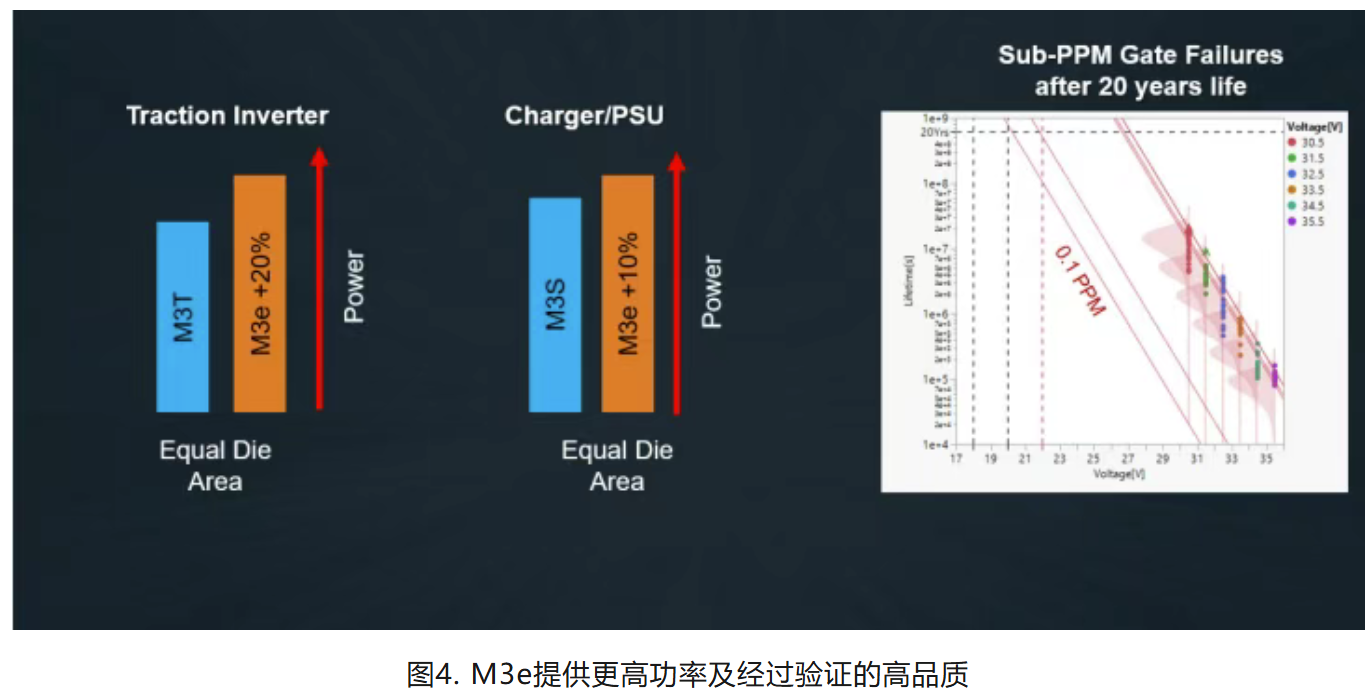

第三代M3e象徵著平面技術的終極發展,其管芯間距與M1相比減少了超過60%。它建立在平面結構的基礎上,這種結構經過數十年的發展,已具備高度的可製造性和更長的使用壽命。SiC平面MOSFET在現場已累計使用數萬億小時,具有極低的故障率。針對SiC材料的弱點,透過100%缺陷篩選和加速電氣測試進行了有效應對。特別是在閘極氧化層方面給予了特別關注,因為它們在導通狀態和關斷狀態下都會承受高電場應力。

除了初始性能外,安森美M3e還通過足夠高的閾值電壓和極低的臨界導通電阻(CRSS)實現了柵極電路的簡化設計,可避免在VGS,OFF=0V時的直通現象。這一特性使得M3e對寄生導通具有更強的抗干擾能力。用戶因此能夠受益於在柵極驅動電路中使用單電壓軌(single voltage rail)這一可行方案。

安森美下一代M4S和M4T產品將採用先進的溝槽設計薄晶圓技術,並進一步將晶片體積減小25%,從而提供業界領先的溝槽技術。最重要的是,第四代MOSFET將採用100%溝槽利用率設計以提供真正有別於傳統平面器件的性能。

結論

現實情況表明,電力電子應用領域仍在充分利用現有的最佳技術方案:平面技術。在溝槽技術不斷進步並趨於成熟的同時,安森美正在對平面技術進行完善,並為溝槽技術規劃了發展藍圖,旨在引導其在未來實現成功部署與應用(圖5)。

參考來源