碳化矽(SiC)模組的開關特性受到許多外部參數的影響,例如電壓、電流、溫度、閘極配置和雜散元件。本系列文章將重點討論。直流鏈路環路電感(DC−Link loop inductance)EliteSiC Power功率模組開關特性的影響。

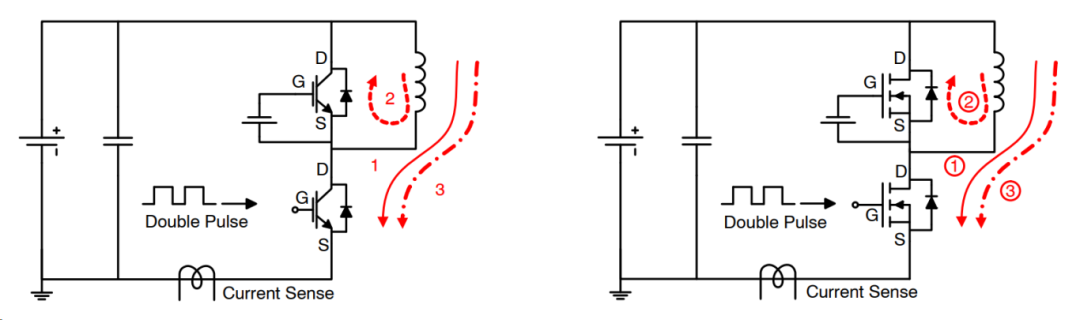

雙脈衝測試(Double Pulse Test,DPT)採用不同的設置來分析SiC的開關特性。如表1所示,針對直流鏈路迴路電感的影響分析,可在直流鏈路電容和模組之間添加母線進行測試。針對柵極迴路電感的影響分析,如表10所示,可在柵極驅動板和模組之間添加外部插座或電線。為了研究模組的開關特性,本次測試使用900V、1.7mΩ EliteSiC Power功率模組(NVXR17S90M2SPC)作為待測器件(DUT)。

圖 1. 雙脈衝測試設置

_20251106025919.png)

表1. 直流鏈路環路電感測試設置

SiC MOSFET開關特性與直流鏈路環路電感(LS)的關係

本節分析不同直流鏈路電感對SiC MOSFET開關特性的影響。對NVXR17S90M2SPC模組進行雙脈衝測試的條件如下:

- DUT: NVXR17S90M2SPC 低端

- VDC = 400 V

- ID = 600 A

- VGS = +18/−5 V

- RG(on) = 3.9 Q

- RG(關閉) = 1.8 Q

- Tvj= 25℃

圖6描述了不同直流鏈路環路電感在SiC MOSFET導通期間的對比波形,特性總結如表6所示。較高的環路電感設置會引起較高的感應電壓VDS壓降以及較慢的開啟速度di/dt。結果顯示,這將導致較低的導通損耗,因為損耗是VDS和ID隨時間的積分。

就二極體而言,反向恢復峰值電流之後,較高的迴路電感會影響二極體的峰值電壓。結果顯示,較高的迴路電感配置會影響具有快速恢復特性的二極體,導致更高的反向恢復損耗。由於快速恢復,增加RG(on)可能需要考慮與EMI相容性。此外,在SiC MOSFET的情況下,EMI相容性比IGBT更為關鍵,因為它具有更大的振盪幅度和頻率,能作為噪聲源運作。

_20251106030114.png)

圖 6. SiC MOSFET導通波形與直流鏈路環路電感的關係

_20251106030106.png)

表 6. SiC MOSFET導通特性與直流鏈路環路電感的總結

圖7描述了不同直流鏈路環路電感情況下,在SiC MOSFET關斷期間的對比波形,特性總結如表7所示。較高的環路電感設置顯示關斷期間di/dt較慢,VDS峰值較高是由於電感產生的電壓。結果顯示,較高的環路電感會導致較高的關斷損耗,因為損耗是VDS和ID隨時間的積分。然而,在大電流驅動情況下,較高的VDS峰值電壓可能會超過VDS的電壓限制。因此,強烈建議增加RG(off)以抑制峰值電壓和振盪。此外,應根據雜散電感和關斷速度考量的重要系統設計因素,遵循反向偏置安全工作區(RBSOA)以及與EMI法規的相容性。

_20251106030355.png)

圖 7.SiC MOSFET關斷波形與直流鏈路環路電感的關係

_20251106030400.png)

表 7. 總結:SiC MOSFET關斷特性與直流鏈路環路電感

SiC MOSFET開關特性與帶優化電阻RG的直流鏈路環路電感G) 的關係

較高的直流鏈路環路電感設置,在導通時通過較高的VDS電壓降具有較低的 E在同時,從系統層面考量,必須增加RG(開啟)以補償VSD電壓峰值/幅度和電磁干擾水平。此外,更高的VDS過壓會導致RBSOA性能變差,因此需要根據直流鏈路環路調整R。關(G關閉)電感設定。圖8描述了帶有優化的R。G(開啟)直流鏈路環路電感設置在SiC MOSFET導通期間的對比波形。調整RG(開啟),直到它具有與初始 23nH 測試設置相似的 VSD電平,因為VSD峰值和振盪是MHz範圍內重要的EMI噪聲源。因此,較高的直流鏈路環路電感設置顯示出較高的EMI噪聲。在和較慢的 di/dt。

_20251106030444.png)

圖 8. SiC MOSFET導通波形與帶優化電阻RG(on)的直流鏈路環路電感的關係

_20251106030449.png)

表 8. SiC MOSFET導通特性與帶優化電阻RG(on)的直流鏈路環路電感的總結

圖9描述了帶有優化柵極電阻RG(off)的不同直流鏈路環路電感在SiC MOSFET關斷特性之間的對比波形。保留VDS過衝電平類似於初始23nH設置,較高的RG(off)用於較高的環路電感設置。結果顯示,較高的直流鏈路環路電感設置顯示出較高的Eoff和較慢的dV/dt。

_20251106030459.png)

圖9. SiC MOSFET關斷波形與帶優化柵極電阻RG(off)的直流鏈路環路電感的關係

_20251106030506.png)

表 9. SiC 關斷特性與直流鏈路環路電感的總結

評論