新思SYN43752晶片在低速率下將功率設計得比較陡,這是因為IEEE對平坦度(flatness)的要求一直在放寬。低速率的尖峰設計是為了在頻帶邊緣(band edge)表現更佳,從而更容易通過FCC/CE等認證。如果客戶因平坦度指標超標而需要調整功率的形狀,可以按照以下步驟進行:

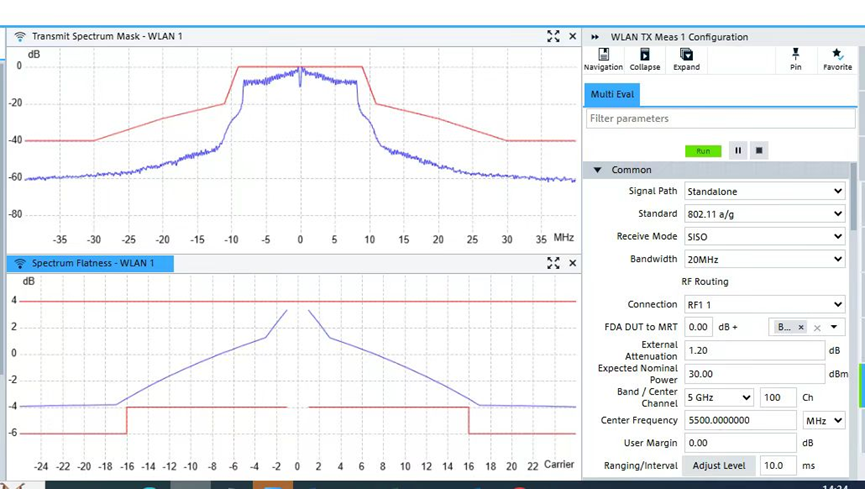

1,預設參數在低速率下的功率平坦度形狀如下圖所示:

圖1,測試儀器的數據

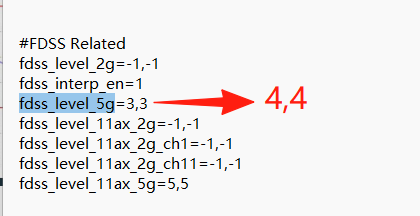

2,在 nvram 文件中找到以下參數,將其調整為 4,4,以 5G 為例。

圖2,nvram檔案中的參數

3,保存 NVRAM 文件,並推送到板子裡替換原來的 NVRAM 文件,重啟,並加載 MFGTEST 固件進入測試。

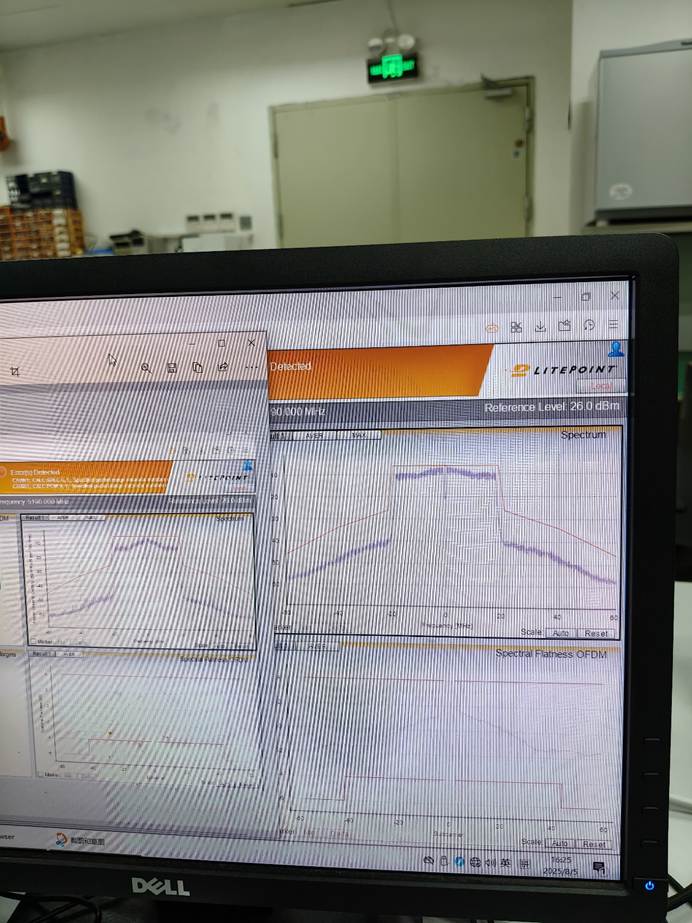

4,左邊是預設參數的功率曲線,右邊是新參數的功率曲線,可以看出功率更加平穩。

圖3,測試儀器的數據介面

常見問題解答(FAQ)

問題1:Flatness指標在SYN43752中的明確定義是什麼?

答案:

在SYN43752中,平坦通常指S21插入損耗(Insertion Loss)在目標頻帶內的峰峰值波動(Peak-to-Peak Variation)。

·定義在IP核的工作頻率範圍內(如0至Nyquist頻率),S21曲線的最大值與最小值之差(單位:dB)。

·典型場景適用於PCIe/CXL/USB等高速介面的通道響應平坦度評估,確保信號在傳輸過程中不因頻域失真導致時序抖動惡化。

·示例值數據手冊可能規定在 0-16 GHz 頻段內,平坦度 ≤ ±2 dB(具體需查證規格書)。

問題2:SYN43752的平坦度保證值及測試條件是什麼?

答案:

保證值:

·典型值±1.5 dB(如 8-16 GHz 頻段)

·最大值±3.0 dB(全頻段,取決於速率模式)

測試條件:

·參考負載50Ω單端或100Ω差分阻抗

·封裝模型包含IBIS/AMI封裝寄生參數(如2.5D/3D封裝)

·環境室溫(25°C)、標稱電壓(如0.8V)

·一致性標準需符合PCIe 6.0/CXL 3.0等協議規定的眼圖模板(例如3.5dB ILD容忍度)。

問題3:哪些設計因素對SYN43752的平坦度影響最大?

答案:

關鍵影響因素包括:

1. 封裝設計BGA焊球電感、基板走線阻抗不連續。

2. PCB通道過孔殘樁(Stub)、層間介質材料(Dk/Df值)。

3. 均衡器設定:

喔CTLE高頻增益補償可以改善平坦度,但過度補償會放大噪聲。

喔DFE對殘留峰峰抖動有抑制作用,間接優化平坦度。

4. 工藝角(PVT)高溫/低電壓下放大器的頻寬下降,導致高頻平坦度惡化。

問題4:如何透過模擬驗證SYN43752的平坦度指標?

答案:

推薦工具與流程:

1. 建模:

喔使用HFSS/Q3D提取封裝/PCB的S參數模型。

喔在PrimeSim HSPICE中整合SYN43752的IBIS-AMI模型。

2. 仿真設定:

喔激勵:PRBS31碼型,速率依照IP配置(例如112G PAM4)。

喔分析:執行通道頻域響應(S21)及時域眼圖模擬。

3. 平坦度提取:

喔從Touchstone文件(.s4p)中計算目標頻段(如0-32 GHz)的S21峰峰值波動。

喔腳本範例:使用Pythonscikit-rf庫處理S參數,輸出波動值。

問題5:若Flatness超標,新思提供哪些調試建議?

答案:

官方優化方案:

1. PCB層疊優化:

喔縮短高速信號參考層切換距離,減少阻抗突變。

喔選用超低損耗介質材料(如Megtron 6)。

2. SerDes配置調整:

喔啟用CTLE的「Peaking Mode」提升高頻增益(需權衡噪聲)。

喔調整DFE抽頭權重以補償特定頻點的凹陷。

3. 封裝改進:

喔採用矽中介層(Si Interposer)減少焊球電感。

喔優化BGA escape區域走線長度匹配。

4. 診斷工具:

喔使用Synopsys PrimeWave平台執行靈敏度分析,定位Flatness瓶頸。

評論