對於許多進行PCB佈局設計的人來說,射頻走線因涉及到類比信號、EMC(電磁相容性)、阻抗匹配等問題,通常在設計時會參考晶片手冊中提供的建議。例如,當射頻走線需要進行相容設計時,通常會採用兩個封裝重疊共享的方式來處理,目的是防止因射頻信號阻抗不連續而導致信號在邊角處輻射。

本文利用實際案例來分享射頻模組在PCB設計中應該如何處理co-layout(共佈局)問題。

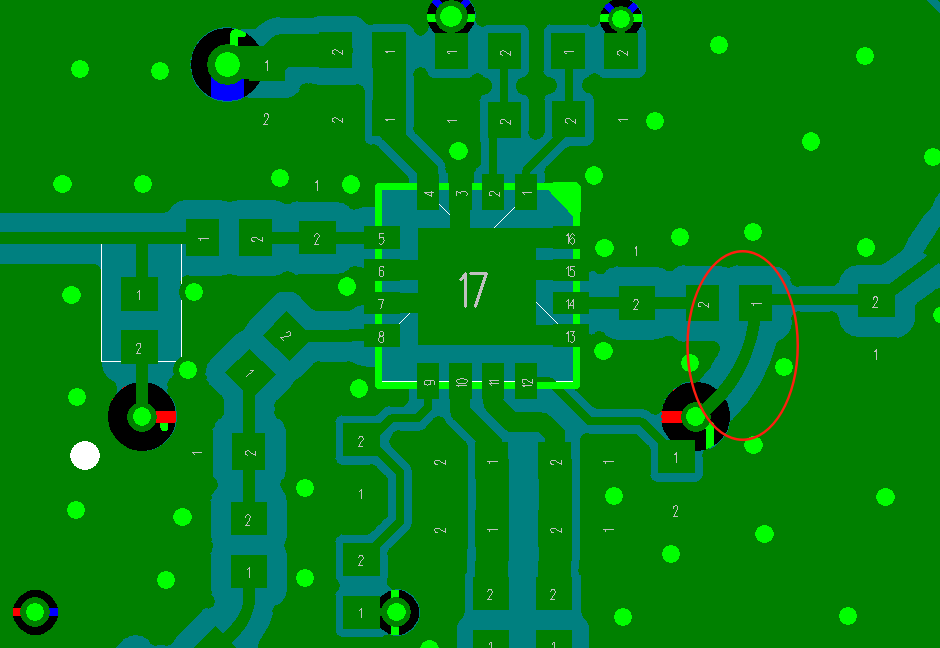

如下圖所示是A客戶產品中FEM射頻模組的佈局設計,FEM模組兩端都設計了一個分線的位置,主要作用是進行兼容設計,但關鍵問題是元件並未真正做到co-layout,只是透過射頻線調整其方向。這樣的處理方式相當於在RF路徑上多出一段導線,導致整段的特性阻抗失配,從而產生EMI問題。

如下圖所示,我們透過網路分析儀測量到目前的特性阻抗情況已經處於失配狀態,透過元件匹配調整已無法得到有效改善。

針對這種情況的調整策略就是在共佈局中多增加一個0歐姆電阻。在射頻電路中常採用共佈局方式,透過共享封裝(Footprint)來實現路徑重疊,避免因阻抗不匹配而導致的EMI干擾。如下面的圖所示,透過兩個同封裝的元件重疊焊盤的方式,不僅可以減少90度轉折的殘段,還能確保阻抗的連續性。

1.什麼是射頻Co-layout?

射頻Co-layout是指在設計和製造過程中,將多個射頻元件或系統元件在物理空間中合理安排,以確保它們之間的互連最小化,同時最大化信號傳輸的效率和可靠性。

2.為什麼射頻Co-layout很重要?

射頻Co-layout可以減少信號干擾、提高系統性能、降低功耗、優化空間利用率,並減少製造成本。

3.射頻Co-layout的主要挑戰有哪些?

挑戰包括元件間的電磁干擾(EMI)、熱效應管理、信號完整性以及互連的複雜性等。

4.如何評估射頻Co-layout的效果?

可以透過信號完整性分析、電磁相容性測試(EMC)以及實際性能測試來進行評估。

5. 射頻Co-layout對系統功耗有何影響?

合理的佈局可以減少不必要的訊號傳輸損耗,從而降低系統功耗。

評論