簡介與封裝說明

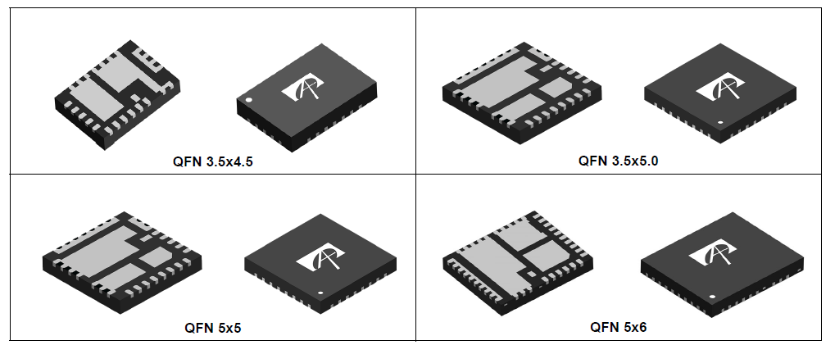

將多個矽晶元封裝於四方扁平無引腳(QFN)封裝中,已廣泛應用於系統電源供應領域。AOS(Alpha and Omega Semiconductor)的 Dr.MOS 和智慧功率級模組(SPS)產品,提供多種封裝尺寸,例如: QFN3.5x4.5、QFN3.5x5、QFN5x5 及 QFN5x6,以滿足各種電源需求。這些產品在同步降壓型 DC-DC 轉換器的應用中(如高效能運算、電信設備、高階顯示卡等),具備高效率、高功率密度與高切換頻率的優點。

DrMOS 和 SPS 的電路板組裝挑戰

下方列出了各種 QFN 封裝尺寸。這些封裝具有相似的特性,例如較細的間距引腳與裸露焊盤,用於 IC、上橋與下橋晶粒焊盤,以及下橋閘極。我們將以 QFN5x5 封裝為例,說明在表面黏著技術(SMT)組裝過程中可能面臨的挑戰以及應對方法。

QFN 封裝的引腳設計為細間距,引腳間距為 0.25 毫米。建議使用表面黏著元件(SMD)焊墊設計,以避免因焊料橋接而造成的短路問題。

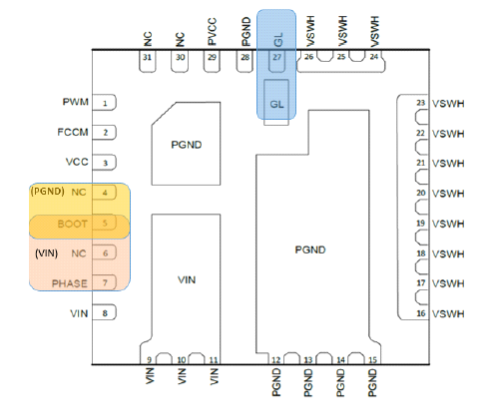

QFN5x5 封裝的 DrMOS 一般引腳配置說明如下:

如果第6腳或第8腳(VIN)與第7腳(PHASE)在PCB板上因錫橋而短路,第7腳的wire bonds會熔斷,導致上橋 MOSFET 以線性模式運作,並最終損壞。

如果第5腳(BOOT)與第4腳(PGND)或第6腳(VIN)短路,將會導致上橋 MOSFET 損壞。

如果第27腳(GL)與第28腳(PGND)或第26腳(VSWH)短路,則上橋和/或下橋MOSFET 有可能會損壞。

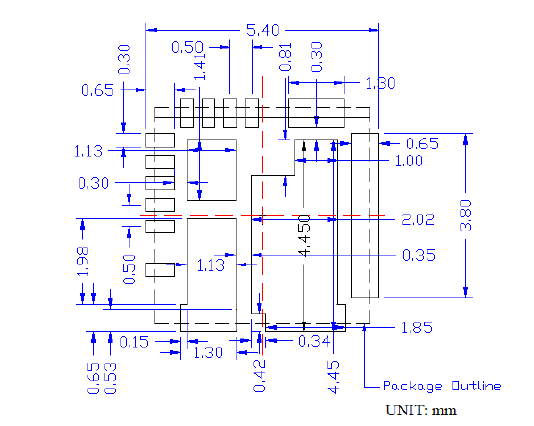

下圖顯示了 QFN5x5 封裝建議的焊墊佈局(Land Pad Pattern)。

隱藏第4腳(PGND)可以降低第5腳(BOOT)與 PGND 短路的風險。

隱藏第6腳(VIN)可以降低第7腳(PHASE)和/或第5腳(BOOT)與 VIN 短路的風險。

隱藏第27腳和 GL 可以避免 GL 與 GND 或 VSWH 短路。

建議的land pad pattern考慮了 PCB 製造過程中的公差以及組裝時 Dr.MOS 元件的定位誤差。為了避免迴焊後出現對位不良,這些公差最多可達 0.10 毫米。

PCBA 考量事項

錫膏

在安裝 DrMOS 和 SPS 封裝時,常用的錫膏類型為 Type 3 和 Type 4,金屬含量介於 88% 至 90%。建議使用免清潔助焊劑(No-clean flux),例如 ROL0 類型的松香基、低活性、無鹵配方。由於焊點的間隙高度較低,免清潔助焊劑可避免需清潔包裝底下的助焊劑殘留。

錫膏對儲存條件與暴露時間非常敏感。如果錫膏超過其可接受的暴露時間限制,可能會導致氣孔(void)以及焊點可靠性問題。儲存條件也會影響錫膏品質,因此遵循錫膏製造商的處理與儲存建議是非常重要的。

目前電子組裝中最常用的無鉛焊料合金為 96.5Sn/3.0Ag/0.5Cu(SAC305)。在使用前,應先評估鋼網(stencil)開孔設計與電路板表面處理,以避免產生焊球、氣孔或濕潤性不佳等不良現象。

鋼網設計(Stencil Design)

引腳與裸露焊盤(Exposed Pad)的開孔設計

引腳與裸露焊盤的開孔應設計得比電路板焊墊略小。

裸露焊盤的開孔比例

裸露焊盤的開孔大小約為電路板焊墊面積的 50% 至 60%。

引腳的開孔比例

引腳的開孔應小於焊墊面積,以平衡與裸露焊盤形成的焊點厚度。

建議的鋼網厚度

建議的鋼網厚度為 0.125 毫米。

鋼網通常採用雷射切割製成。對於建議的開孔尺吋,開孔面積比與長寬比應符合鋼網製造的一般最低可接受標準。

Q1: Dr.MOS and SPS為何是目前市場的主流元件?

Ans: Dr.MOS / SPS是以MOSFET搭配Driver的整合型的元件,可以提升效率以及整合度,減少控制路徑的長度,且操作頻率可以拉升,也更能因應CPU/GPU瞬間所需的動能電流,目前高階伺服器以及新電腦平台高階機種大多選用Dr.MOS / SPS晶片。

Q2: Dr.MOS使用上的優勢為何?

Ans: 因為Dr.MOS是封裝在一個QFN package中,可以大幅降低控制訊號的傳遞路徑,因此,將可以提高操作頻率,提至550KHz-850KHz之間,提供CPU/GPU足夠的動態電流。

Q3: Dr.MOS封裝內部常用的整合技術有哪些?

Ans: Dr.MOS裡面的驅動電路和MOS的整合一般分為兩種: 一種是單片集成,即驅動電路和MOS管是做在一起的,該方法製程對可靠性要求較高,成本也隨之提高。另一種是透過封裝進行集成,MOS是採用專門的工藝,而處理作業比驅動電路減少很多,可靠性及成本顯著降低。

Q4: DR.MOS以及SPOS 最大的差異點?

Ans: SPS主要是在Dr. MOS基礎上增加了「溫度監測」和「電流監測」功能,適合用於高功率AI伺服器、電信設備和5G高頻資料傳輸等應用。

Q5: 使用SPS的設計優勢為何?

Ans: SPS系列向設計人員提供高溫監控、可程式設計過溫關斷、過零檢測(Zero Cross Detection, ZCD) 電路以及災難性故障檢測。溫度監控(TMON)可精確報告模組溫度,方便設計人員移除負溫度係數(NTC)電路,從而依次減少PCB空間、零件數量,並降低物料清單(BOM)總成本。可程式設計熱關斷(P_THDN)具有可調節門檻值,便於設計人員設定過溫保護 (OTP) 以滿足系統需求。

參考來源