負載電容和CMOS輸出接腳的連接問題

將負載電容連接到CMOS積體電路(IC)的輸出接腳時,須謹慎選擇電容的大小。具體來說,大電容會增加CMOS輸出的傳輸延遲,且電容的充/放電過程會增加進出的電流,這可能導致電路中的雜訊問題,甚至可能因電流過大而損壞連接引線。此外,由於電流在掉電時會流向輸出寄生二極體,因此大負載電容無法直接連接到CMOS IC。

若需將電容器直接連接到CMOS IC的輸出端以增加其延遲時間或過濾噪聲,則應選擇500pF或更小的電容。當需要較大的電容時,應在IC輸出端和電容器之間連接限流電阻(R)。具有輸出容限功能的CMOS IC不需要限流電阻(R)來斷電。但可能需要一個限流電阻(R)來限制進入電容的充電電流。

不僅如此,大負載電容也不應直接連接到CMOS IC的輸入腳位。

當電容因掉電而放電時,電流流向內部保護二極管,並透過輸入引腳返回VCC。因此,大負載電容不能直接連接到輸入引腳。如果需要直接連接電容,建議最高選擇500 pF的裝置。如果需要更大的電容器,則應在IC輸入端和電容器之間連接限流電阻(Rs)。

計算工作電流和功耗

計算工作電流和功耗如何計算通用邏輯IC的功耗?可透過取得靜態電流和動態電流,然後將該電流乘以施加在IC的電壓來計算通用邏輯IC的功耗。

靜態功耗:PS

當CMOS邏輯處於靜態(即其輸入電壓幾乎保持不變)時,除了流經內部反向偏壓pn結的微小漏電流(即靜態供電電流,ICC)以外,幾乎沒有電流流動。

靜態耗電量是將ICC乘以供電電壓:PS=VCC×ICCVCC:施加在邏輯IC上的電壓。 ICC:如資料表所示的靜態供電電流。

靜態耗電量:PL+PPD

動態供電電流是指當輸入在高電位和低電位之間轉換時流過CMOS邏輯IC的電流。此電流在電容充放電過程中流動。必須同時考慮寄生電容(內部等效電容)和負載電容。

動態功耗是將動態供電電流乘以施加在p通道或n通道MOSFET上的電壓。為方便起見,以下計算將假設此電壓等於VCC,此時動態供電電流最大。

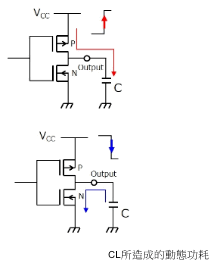

負載電容(CL)所造成的動態功耗:PL

PL指外部負載充電和放電時的功耗,如右圖所示。

儲存在負載電容上的電荷量(QL)計算為QL=CL×VCC,CL為負載電容。

設輸出訊號頻率為fOUT(=1/TOUT),則平均電流(IL)表示為:IL=QL/T=CL×VCC×fOUT;因此,動態耗電量(PL)為:PL=VCC×IL= CL×VCC²×fOUT;

若一個IC有多重輸出,其動態功耗可計算如下:PL=VCC²×Σ(CLn×fOUTn)

內部等效電容(CPD)所造成的動態耗電量:PPD

CMOS邏輯IC具有各種寄生電容,如右圖所示。這些電容可等效地表示為CPD(實際上,CPD的基於零負載條件下相對較高頻率(1 MHz)時的功耗計算得出的)。

PPD是IC的等效電容消耗的功率,可以與PL相同的方式考慮。但請注意,PPD的計算是基於輸入頻率(fIN):PPD=VCC×IL=CPD×VCC²×fIN。

總功耗(PTTL)可以表示為靜態功耗(PS)和動態功耗(PL+PPD)之和:PTTL=PS+PL+PPD。

總功耗(PTTL)可以表示為靜態功耗(PS)和動態功耗(PL+PPD)之和:PTTL=PS+PL+PPD。輸入容限功能可用於電平轉換

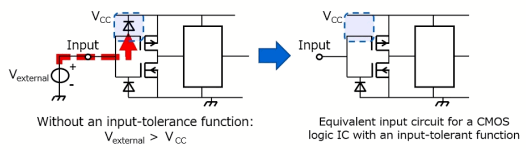

輸入容限功能允許在電源啟動時或電壓為0 V時,向輸入端施加高達最大工作電壓的電壓,允許電平從較高電壓轉換為較低電壓。例如,東芝的74VHC和74LCX系列可用於將5 V轉換至3 V,74VCX系列可用於將3V轉換至1.2 V。

推薦以下是TOSHIBA-Major characteristics of general-purpose logic ICs.

推薦以下是TOSHIBA-Major characteristics of general-purpose logic ICs.|

Type |

Series Name |

CMOS Logic ICs Series No. |

One-Gate Logic ( L-MOS ) Equivalent |

Operating Voltage Range VCC (V) |

Propagation |

Output Current *2 IOUT (mA) |

Input-Tolerant |

Output Power-down Protection |

|---|---|---|---|---|---|---|---|---|

|

For 5 V Systems |

Standard |

3 to 18 |

200 |

±0.51 |

△*3 |

- |

||

|

High Speed |

2 to 6 |

23 (at 4.5 V) |

±4.0 or ±6.0 |

△*3 |

- |

|||

|

4.5 to 5.5 |

31 |

- | ||||||

|

Advanced |

2 to 5.5 |

8.5 |

±24 |

- |

- |

|||

|

4.5 to 5.5 |

9.0 |

|||||||

|

Very High Speed |

2 to 5.5 |

8.5 |

±8.0 |

● |

- |

|||

|

10 |

||||||||

|

4.5 to 5.5 |

9.5 |

● |

●*4 |

|||||

|

1.8 to 5.5 |

8.5 |

±16 |

● |

● |

||||

|

For low |

Low Voltage |

1.65 to 3.6 |

6.5 |

±24 |

● |

●*5 |

||

|

Very Low Voltage |

1.2 to 3.6 |

4.2 |

±24 |

● |

● |

*1: Maximum propagation delay time of typical ICs (TC4001, TC74HC244, TC74HCT244, TC74AC244, TC74ACT244, 74VHC244, 74VHC9541 (An-Yn), VHCT244, VHCV244, 74LCX244, and TC74VCX244) at -40 to 85 °C, except for the TC4001 for which the maximum propagation delay time at 25 °C is shown.

*2: Those output current values are from DC Characteristics table of the datasheet. In addition, they are specified in absolute maximum ratings.

*3: TC4049BF/BP, TC4050BF/BP, TC74HC4049BP/BF/BFT, 74HC4049D, TC74HC4050BP/BF/BFT and 74HC4050D have the input-tolerant function that allows level shifting from a higher voltage to a lower voltage.

*4: The TC7SET series and TC7SZU04/TC7WZU04 does not have an output power-down protection function.

*5: The TC7SZ series in the fSV package do not have an output power-down protection function except those with an open-drain output.

Q&A

Q: 如何防止邏輯IC裝置損壞?

A: 在輸入側插入二極體以進行ESD防護。如果施加的電壓高於VCC或在IC關閉時施加電壓,則輸入端和電源之間的二極體可能會導通。IC可能會被產生的大電流破壞。因此,透過使用具有輸入容限功能的IC,即輸入端和電源之間無二極體的IC,可以防止裝置損壞。

Q: 輸出端的保護?

A:

(1) 在CMOS電路中除了三端輸出元件外,不允許兩個元件輸出端並接,因為不同的元件參數不一致,可能導致NMOS和PMOS元件同時導通,形成大電流。

但為了增加電路的驅動能力,允許把同一晶片上的同類電路並聯使用。

(2) 當CMOS電路輸出端有較大的容性負載時,流經輸出管的衝擊電流較大,易造成電路失效。

因此,必須在輸出端與負載電容間串聯一限流電阻,將瞬態衝擊電流限制在10mA以下。

Q: CMOS常遇到的介面電路問題?

A:

(1) 與OPA連接時,若運轉採用雙電源,CMOS採用的是獨立的另一組電源。若OPA使用單電源,與CMOS使用的電源一樣,可直接連接。

(2) TTL到CMOS的連接。用TTL電路去 Drive CMOS電路時,由於CMOS電路是電壓驅動元件,所需電流小,因此電流driver不會有問題,主要是電壓驅動能力問題,TTL電路輸出高電平的最小值為2.4V ,而CMOS電路的輸入高電位一般高於3.5V,這就使二者的邏輯電平無法相容。可在TTL的輸出端與電源之間接一個電阻R(Pull up)可將TTL的電平提高到3.5V以上。

點擊連結以取得更詳細的資訊

評論