隨著Al工作負載日趨複雜和高耗能,能提供高能效並能夠處理高壓的可靠SiC JFET將越來越重要。我們將詳細介紹安森美(onsemi)SiC cascode JFET,內容包括Cascode(共源共柵)關鍵參數和並聯振盪的分析,以及設計指南。本文為第一篇,聚焦Cascode產品介紹、Cascode背景知識和並聯設計。

簡介

大電流操作通常需要直接並聯功率半導體器件。出於成本或布局的考慮,並聯分立器件通常是優選方案。另一種替代方案是使用功率模塊,但這些模塊實際上也是通過並聯晶片實現的。本文總結了適用於所有並聯電壓柵控型功率半導體(如SiC JFET cascode、SiC MOSFET、Si MOSFET、IGBT等)的通用最佳實踐方案。並聯Cascode等高增益器件尤其具有挑戰性。遵循這些實踐方案有助於成功實現 SiC JFET cascode的並聯工作。

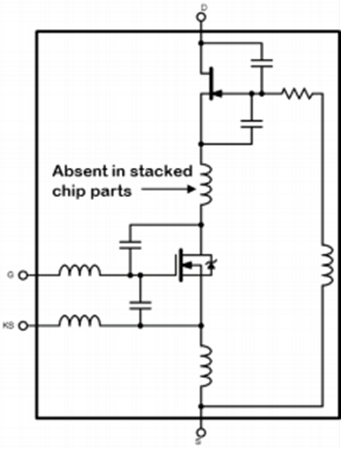

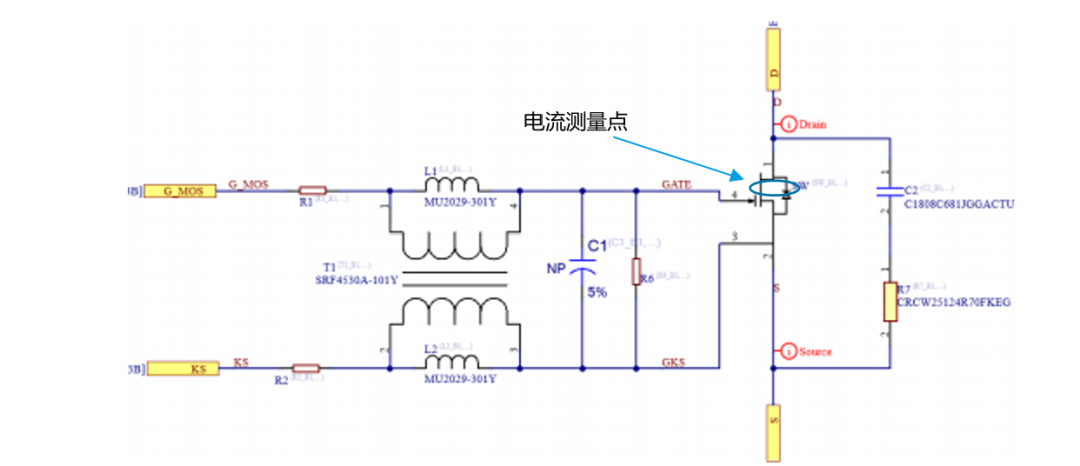

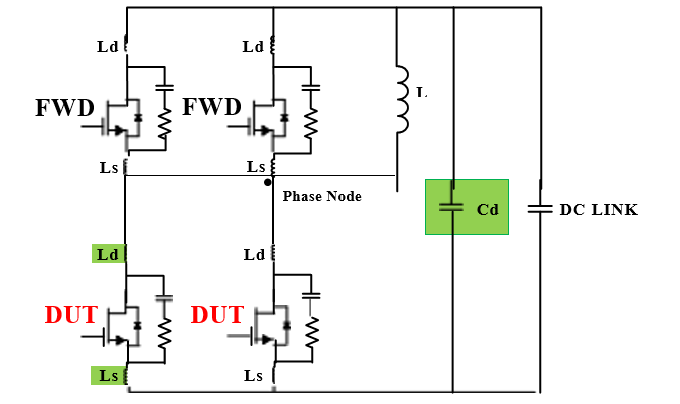

如圖 1 所示,cascode 結構是由一個常開 SiC JFET(碳化矽結型場效應電晶體) 與一個低壓 Si MOSFET (矽金屬-氧化物半導體場效應電晶體)串聯而成。JFET的 柵極直接連接到 MOSFET 的源極,JFET 的柵極電阻是 JFET 晶片的一部分。

MOSFET 漏極-源極電壓是 JFET 柵極-源極電壓的反相,從而使cascode 結構呈現常關特性。正如《Cascode入門》中所述,Cascode與其他功率電晶體的主要區別在於,一旦 VDS超過 JFET 的閾值電壓,就沒有柵極-漏極電容。 這是因為 JFET 沒有漏極-源極電容,因此Cascode結構的開關速度極快。 這一特性與寄生電感問題相結合,是Cascode並聯工作中需要解決的核心問題。

並聯的挑戰

靜態電流失配

靜態電流失配是指並聯器件在開關瞬態穩定後,並聯器件之間的電流不匹配現象。對於具有熱不穩定性(如負溫度係數導通電阻的舊式矽二極體或穿通型IGBT)的器件尤其值得關注。如果各個器件導通電阻的變化(分布)足夠小(即經過分選的器件),並且為了彌補不可避免的電流失配而留有裕量,則具有負溫度係數的器件可以成功並聯。

有一個廣為流傳的誤解,認為正溫度係數導通電阻能強制均流,從而有利於並聯。實際上,正溫度係數僅確保熱穩定性。現代功率半導體(包括 SiC JFET、SiC MOSFET、場截止 IGBT 等)的參數分布較窄,這進一步強化了人們對於正溫度係數在均流方面具有強大作用的看法,但決定靜態均流的是參數分布和共同的散熱裝置。

動態電流失配

動態電流失配是由MOS柵控器件和JFET器件固有的器件間閾值電壓變化、電流環路的不對稱性以及柵極驅動器之間傳播時延差異(如果適用的話)所引起的。閾值電壓較低的部件會較早導通、較晚關斷,因此會產生更多的硬開關損耗。在開關頻率非常高的情況下,這種情況更加令人擔憂。

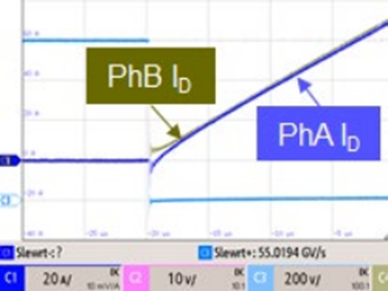

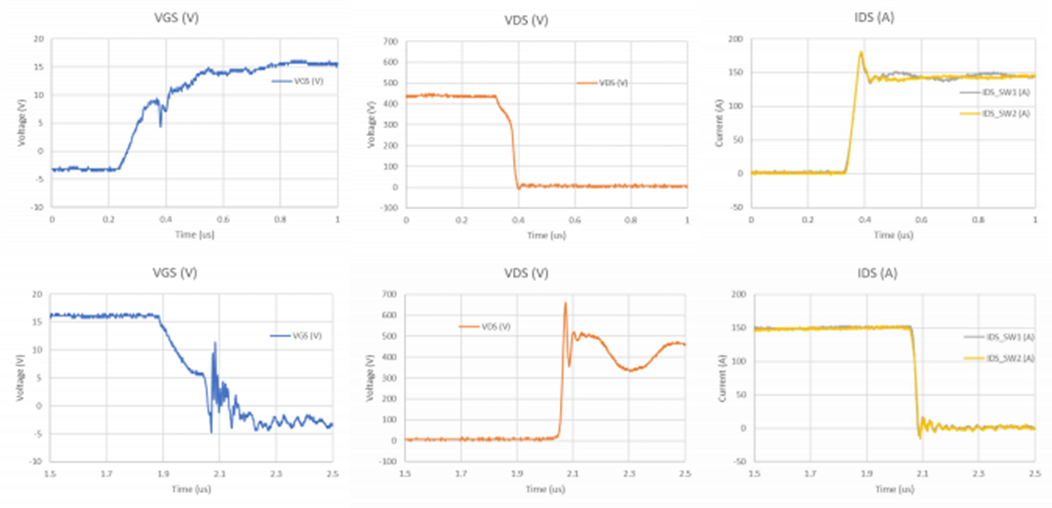

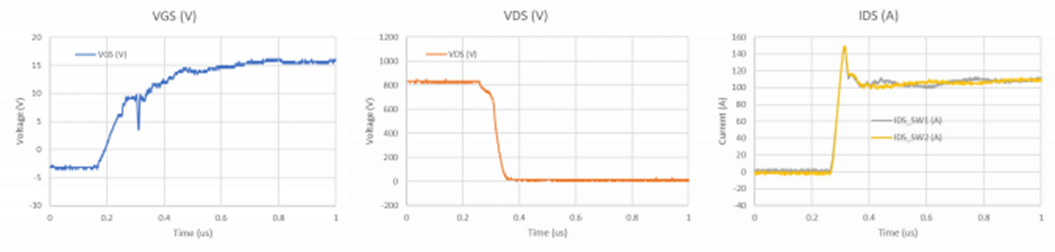

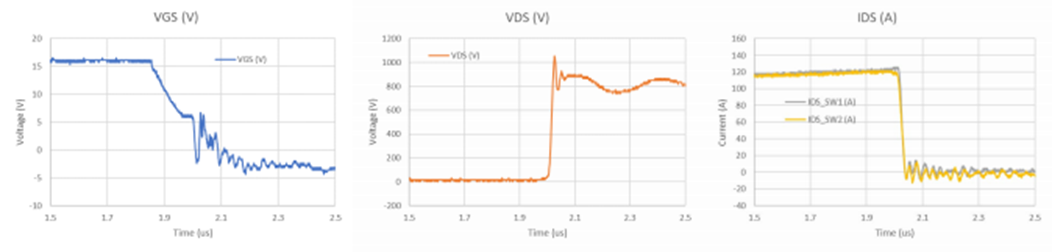

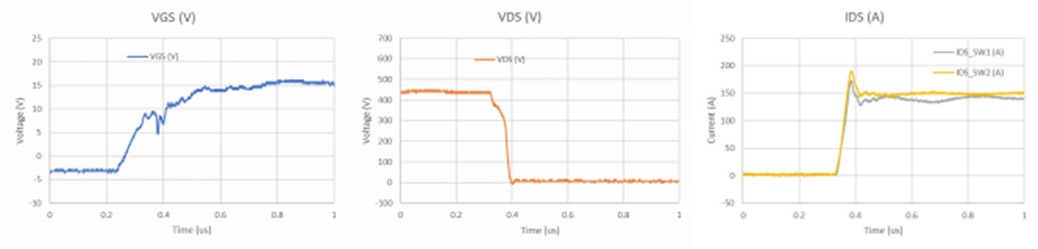

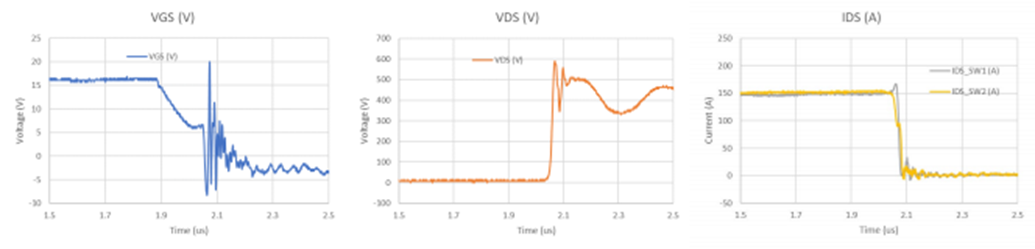

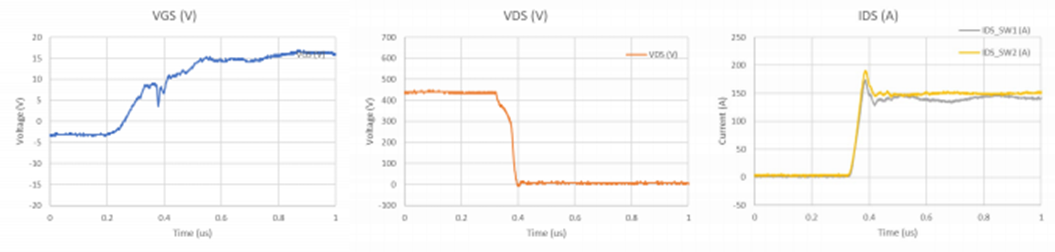

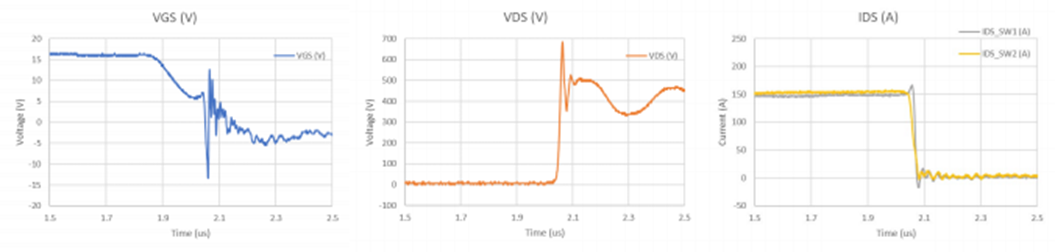

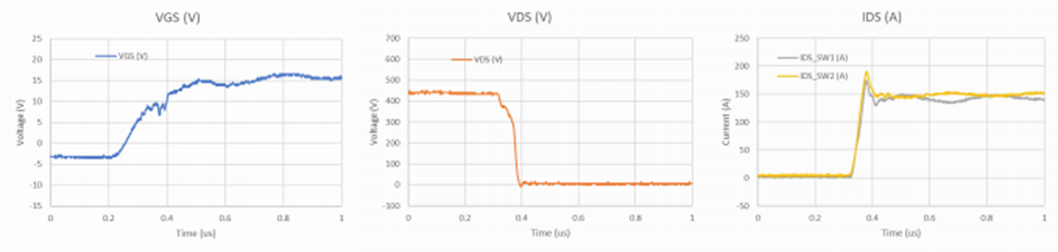

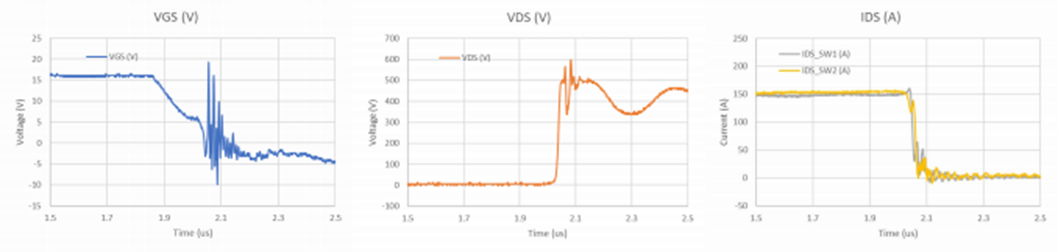

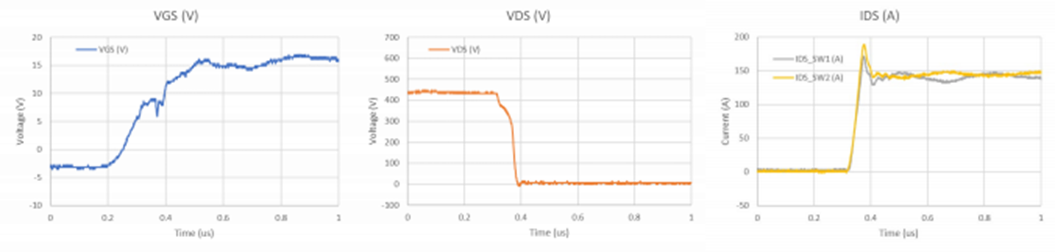

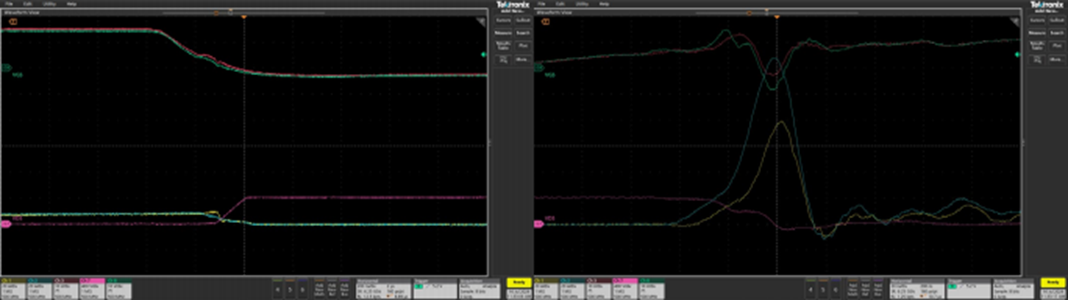

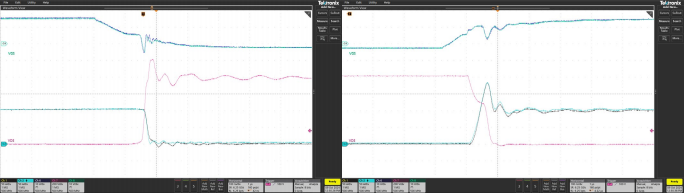

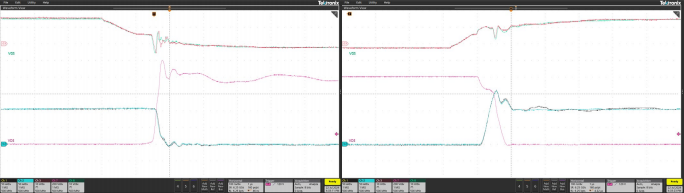

圖2顯示了兩個並聯cascode電路在導通時的動態失配。電流失配迅速減小是典型的現象,因為穩態均流主要由RDS(on)決定。在計算中,使用數據表中RDS(on)和RθJC的最大值,可以為並聯時的靜態和動態電流失配提供安全裕量。

演示和測試結果

根據上述指南設計了一個演示板,並顯示了四個器件的測試結果:

-

UJ4SC075006K4S

-

UJ4C075023K4S

-

UF3SC120009K4S

-

UF3SC120016K4S

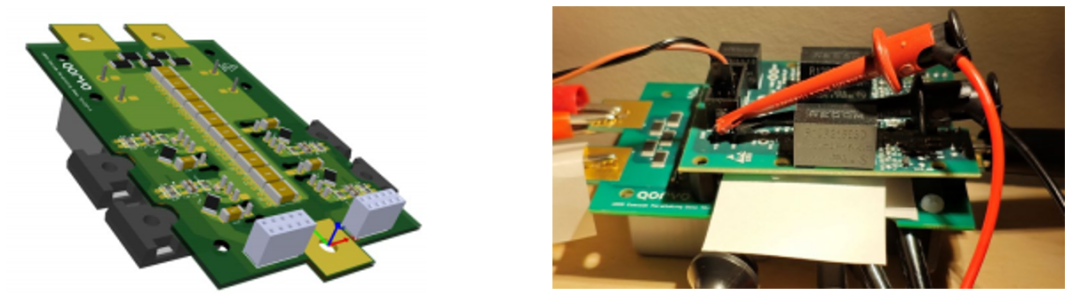

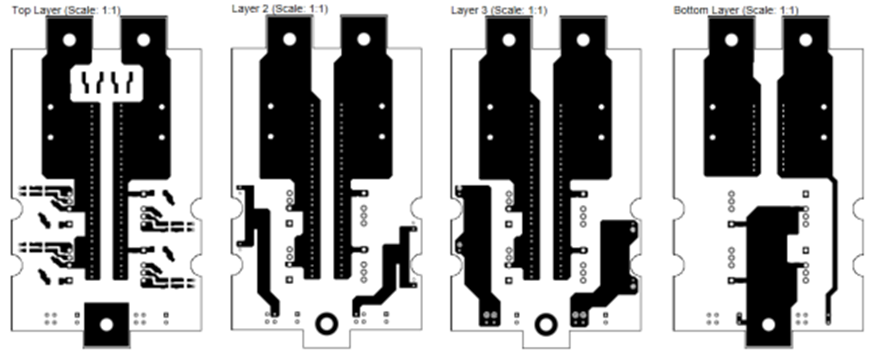

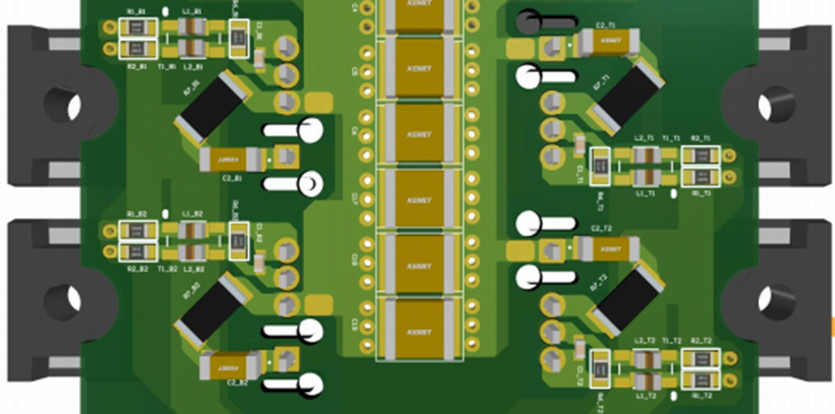

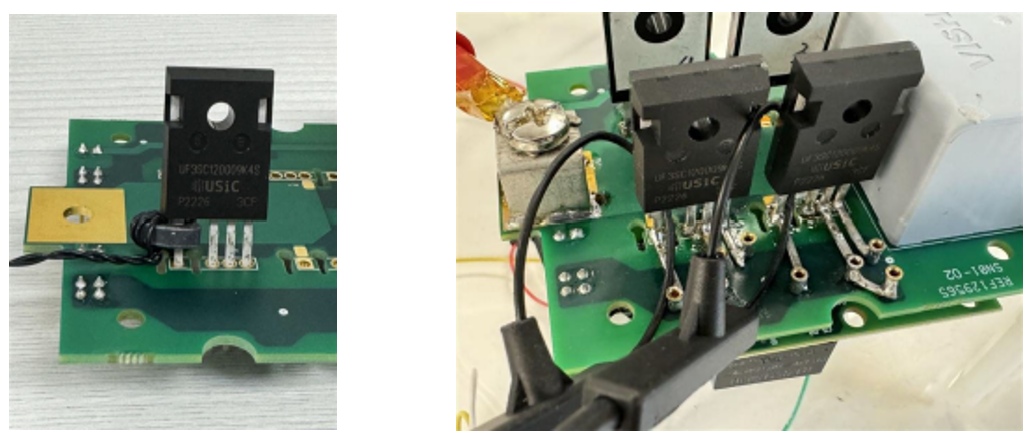

演示板設計

圖 1 顯示了演示和測試板,其中包括一塊並聯了兩個器件的半橋拓撲電源板和一塊柵極驅動器板。

本設計示例遵循功率環路和柵極驅動電路的對稱布局建議。同時,直流母線電容和去耦電容採用對稱布局以最小化換流環路。

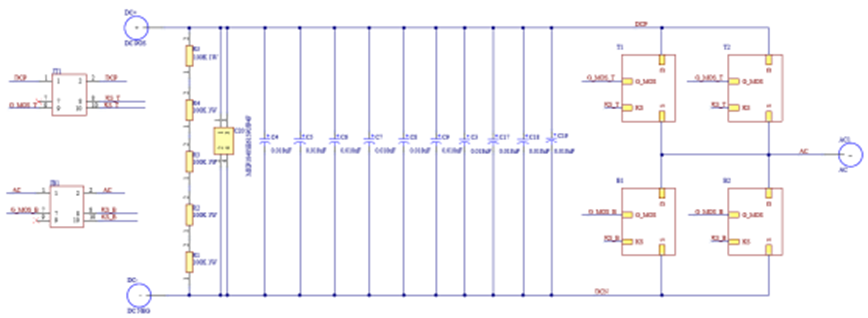

圖2和圖3展示了該演示設計的原理圖,其中使用了鐵氧體磁珠和共模電感(可選)用於研究不同條件下的效果。

測試結果

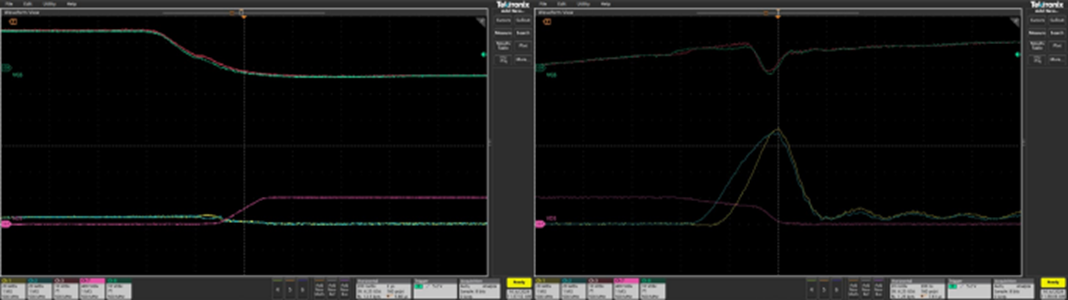

該示例設計的 SiC FET 並聯測試結果,柵極和Kelvin源極上都有鐵氧體磁珠。

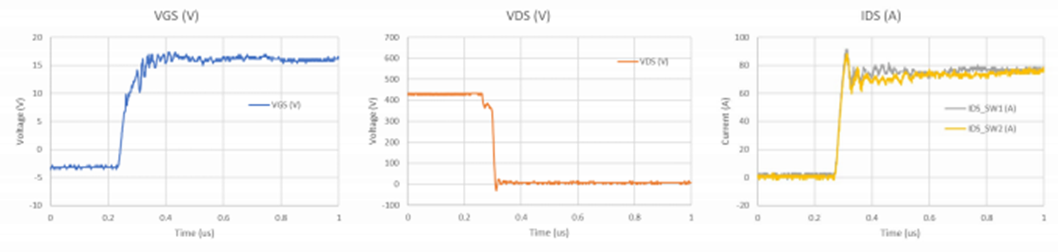

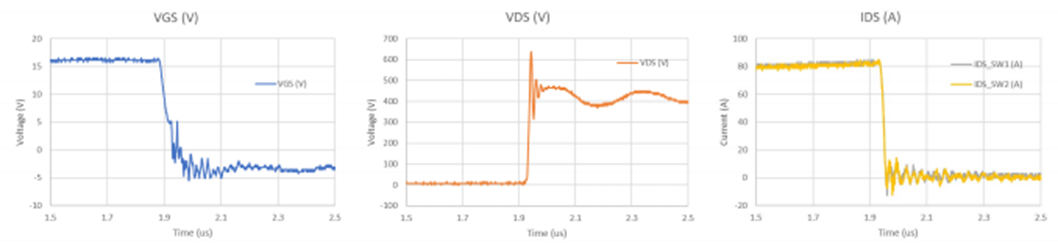

開關波形-UJ4SC075006K4S:

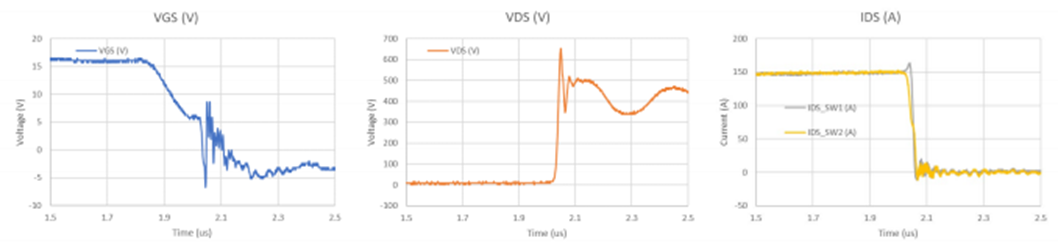

開關波形-UJ4C075023K4S

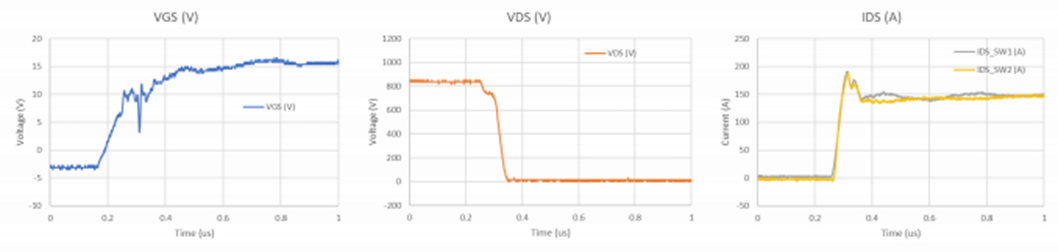

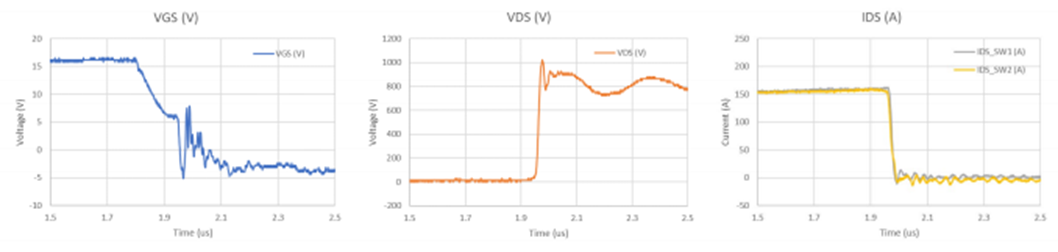

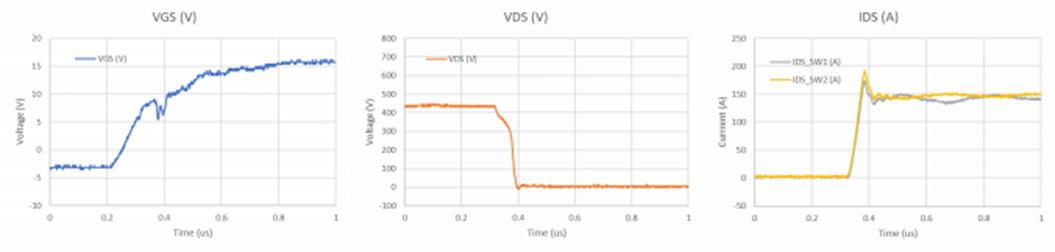

開關波形-UF3SC120009K4S

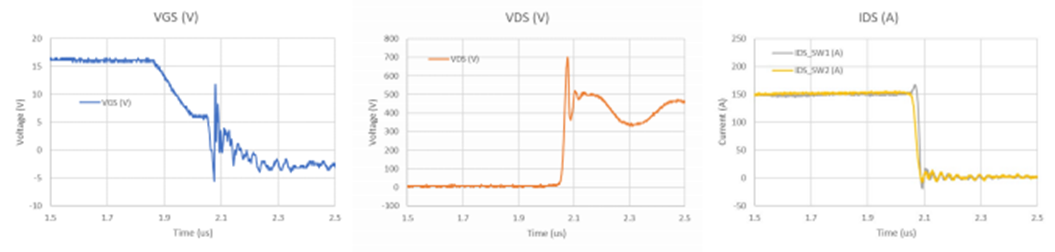

開關波形-UF3SC120016K4S

仿真柵極閾值失配

通常,由於各器件的實際參數與數據手冊標稱值之間存在差異(即便差異微小),此類失配現象不可避免。因此,為了測試鐵氧體磁珠和共模電感在柵極電路上的有效性,在基於UJ4SC075006K4S器件搭建的測試平台中,通過改變單個柵極電阻值(一個為 6.8 歐姆,另一個為 6.2 歐姆)來仿真柵極閾值電平失配狀態。圖 10 至圖 14 顯示了採用不同措施緩解仿真柵極閾值失配的波形圖。

通過改變柵極電阻來仿真柵極閾值失配(未使用鐵氧體磁珠)

柵極上有鐵氧體磁珠的波形

Kelvin源上有鐵氧體磁珠的波形

柵極和Kelvin源極上均有鐵氧體磁珠的波形

柵極電路上有共模電感的波形

仿真布局導致的失配

對稱布局同樣是並聯器件設計的關鍵要點,因為非對稱布局會導致不同支路的漏極走線電感(Ld)與源極走線電感(Ls)產生差異,進而引發動態電流失配或瞬態振盪。此外,去耦電容(Cd)在布局中的位置是否對稱也是影響因素之一。

因此,為驗證鐵氧體磁珠與共模電感在柵極電路上的作用,我們以 UF3SC120009K4S 為基礎,通過改變漏極/源極引線的長度來仿真失配的 Ld/Ls 布局,並對比了不同Cd布局位置的影響。圖14展示了Ld、Ls及Cd的布局位置分布,圖15至圖19則展示了通過不同優化措施減輕非對稱布局負面影響的波形對比。

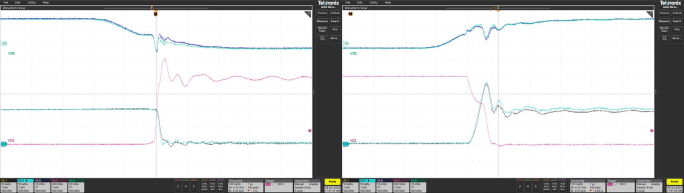

柵極和Kelvin源上均有鐵氧體磁珠的 Ld 不平衡波形(直流母線 400V,Id = 8A)

柵極和Kelvin源上均有鐵氧體磁珠的 Ls 不平衡波形(直流母線 400V,Id = 6A)

Cd 在不對稱位置,柵極和Kelvin源上都有鐵氧體磁珠的波形(直流母線800V,Id= 100A)

Cd 在不對稱位置,柵極和Kelvin源極上均有共模電感的波形(直流母線800V,Id = 100A)

Cd 在對稱位置,柵極和Kelvin源上均有共模電感的波形(直流母線800V,Id= 100A)

由嚴重不平衡的Ld所導致的大動態電流失配。Ld不平衡問題只能通過對稱的布局設計本身來解決。圖16顯示了由Ls不平衡引起的動態電流失配。

為避免器件損壞,本測試中我們未設置過大的Ls不平衡,因為Ls不僅會影響功率環路,還會影響柵極環路。Ls不平衡可通過以下方式解決:採用對稱布局設計並添加鐵氧體磁珠或CMC。添加鐵氧體磁珠可以解決Ls 不平衡問題,但效果不如CMC顯著。此外,與CMC相比,鐵氧體磁珠會降低器件速度,增加開關損耗。因此,我們建議在實際並聯應用中採用CMC結合對稱布局設計方案。

在實現Ld和Ls的平衡後,圖17展示了由Cd不平衡引起的動態電流失配現象(本案例中仍使用鐵氧體磁珠)。通過對比圖17和圖18可以看出,在柵極環路中使用CMC相較於使用鐵氧體磁珠,可以更有效地平衡電流失配和Vgs電壓。同樣,與CMC 相比,鐵氧體磁珠會減慢器件的速度,增加開關損耗。

但有一點我們需要注意:CMC 只能消除Vgs 電壓失配,但不能消除電流失配。對於電流失配,CMC僅能起到緩解作用。因此,如圖19所示,若要徹底消除電流失配,唯一有效的方法是將Cd儘可能靠近並聯半橋並實現對稱布局。基於上述分析,我們再次建議在實際並聯應用場景中使用CMC,並採用對稱布局設計。

設計和測試中的最佳實踐

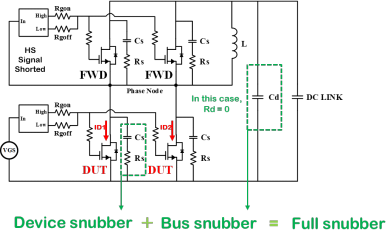

成功並聯SiC FET 需要器件漏極至源極緩衝電路和母線緩衝電路

•成功並聯SiC FET 需要器件緩衝電路,如圖20 所示。用戶指南中推薦了起始值。

•對稱布局至關重要,測試證實,不對稱的漏極和源極雜散電感以及去耦電容的位置會導致開關電流差異過大。

•如果柵極閾值的微小失配和微小的不對稱布局不可避免,那麼柵極和源極環路上的CMC是消除瞬態電流失配或瞬態振盪的最有效辦法。

•不推薦使用鐵氧體磁芯(環形)電流互感器(CT),因為它會由於引線與磁芯之間的互感而導致不平衡的漏極雜散電感。應使用羅氏線圈電流探頭進行電流測量。

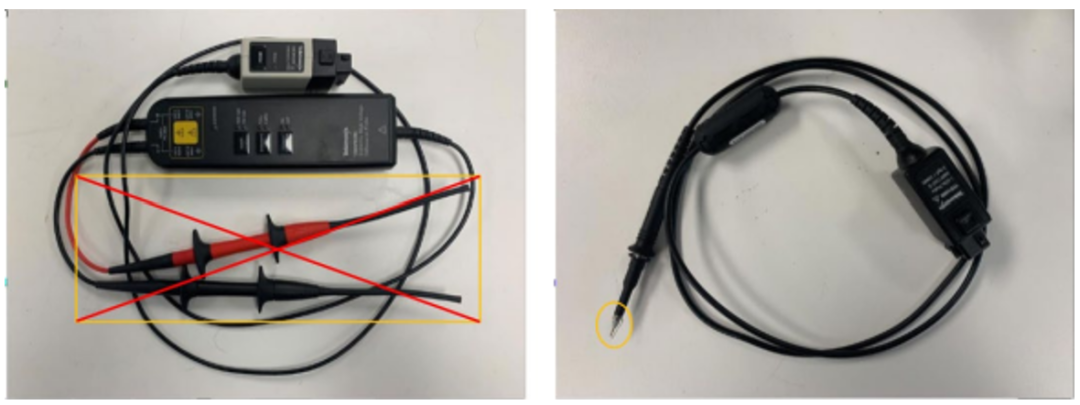

電流測量方法,左:鐵氧體磁芯CT(不推薦);右:羅氏線圈探頭

• 對於電壓測量,不推薦使用差分探頭,因為其引線和導線的環路較大(會增加環路電感),建議使用環路電感較小的無源探頭。

電壓探頭,左:差分探頭(不推薦使用);右:環路電感較小的無源探頭

• 由於dv/dt很高,共模噪聲很容易耦合到柵極到源極的信號測量中,濾除這種噪聲的一種方法是在電壓探頭線纜上添加鐵氧體磁芯,並扭轉這些線纜。

將線纜扭轉,並使用鐵氧體磁芯過濾共模柵源噪聲

結語

儘管SiC JFET cascode結構具有很高的增益和開關壓擺率,只要遵循本應用筆記中概述的指導原則,就能成功實現並聯。本文雖然只討論了兩個器件並聯的情況,但這些並聯準則適用於任何數量的器件並聯。最後,這些指導原則不僅適用於cascode,也適用於任何其他類型的電壓柵控功率電晶體。

對於需要並聯兩個以上分立器件、要求低dv/dt 且不需要器件 RC緩衝電路的大功率逆變器等應用,安森美(onsemi)建議使用Combo-FET 器件。

參考來源