一、概述

NXP 推出的 S32K3 系列 MCU 是針對汽車應用的高性能車規級 MCU,該系列晶片最高支持 ASIL-D 等級的功能安全,廣泛應用於汽車BMS、底盤控制器、車身控制器等汽車應用中,本文將給大家介紹下 S32K3 晶片中的 ERM 模塊,該模塊是實現功能安全的主要模塊之一,該模塊主要負責收集晶片出現的內存相關錯誤並且上報,下文將重點介紹這個模塊的功能。

二、主要特性

ERM 模塊包含有以下特性:

-

當捕獲到錯誤事件時可以選擇是否產生中斷

-

捕獲單比特 ECC 錯誤事件並記錄錯誤地址和特徵信息,以及捕獲多比特 ECC 錯誤事件

-

支持內存的錯誤事件捕獲,每個內存通道有獨立的報告欄位和中斷配置

-

記錄單比特 ECC 錯誤的次數

S32K3 系列晶片最多支持兩個 ERM 模塊:ERM0 和 ERM1

其中不同晶片平台支持情況如下表:

|

Instances

|

S32K358/S32K348/S32K338/S32K328/S32K388/S32K389

|

S32K322/S32K324/S32K344/S32K342/S32K341/S32K312/S32K311/S32K310/S32K314

|

|---|---|---|

|

ERM0

|

支持

|

支持

|

|

ERM1

|

支持

|

不支持

|

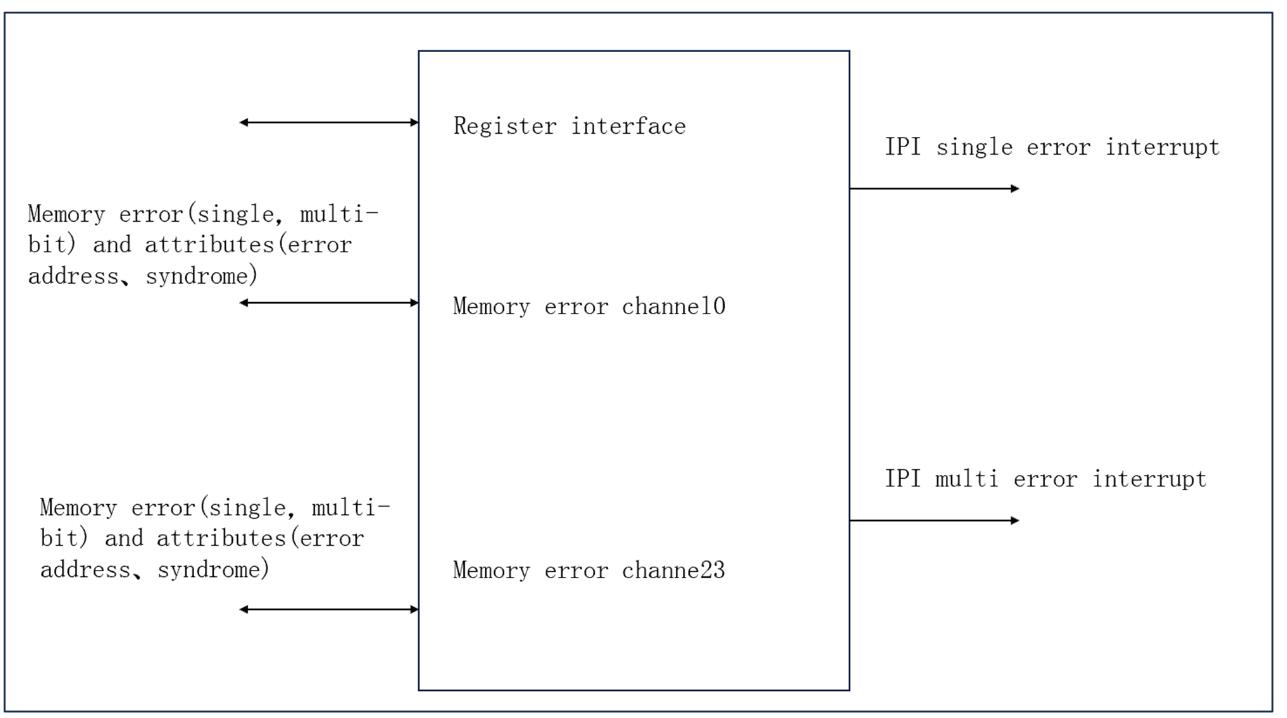

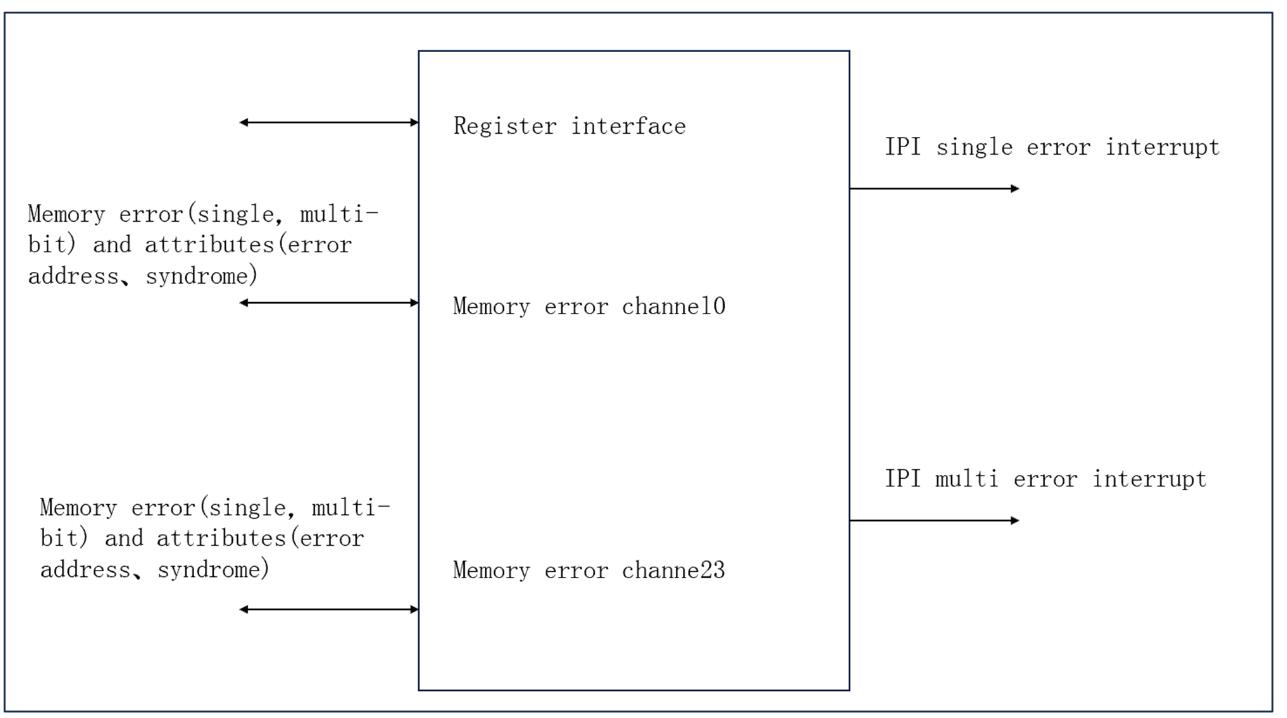

ERM 模塊的框圖如下所示:

圖 2.1 ERM 模塊框圖

三、ERM 模塊通道映射

下面為 ERM0 不同通道跟內存區域間的映射,完整的映射關係可以查閱 S32K3 的用戶手冊。

|

通道

|

模塊

|

捕獲狀態

|

|---|---|---|

|

00

|

SRAM0

|

單比特錯誤、多比特錯誤,絕對錯誤地址和錯誤特徵

|

|

01

|

SRAM1

|

單比特錯誤、多比特錯誤,絕對錯誤地址和錯誤特徵

|

|

02

|

Cortex-M7_0 I-cache tag RAM

|

單比特錯誤、多比特錯誤

|

|

03

|

Cortex-M7_0 I-cache data RAM

|

單比特錯誤、多比特錯誤

|

|

04

|

Cortex-M7_0 D-cache tag RAM

|

單比特錯誤、多比特錯誤

|

|

05

|

Cortex-M7_0 D-cache data RAM

|

單比特錯誤、多比特錯誤

|

|

06

|

Cortex-M7_1 I-cache tag RAM

|

單比特錯誤、多比特錯誤

|

|

07

|

Cortex-M7_1 I-cache data RAM

|

單比特錯誤、多比特錯誤

|

|

08

|

Cortex-M7_1 D-cache tag RAM

|

單比特錯誤、多比特錯誤

|

|

09

|

Cortex-M7_1 D-cache data RAM

|

單比特錯誤、多比特錯誤

|

|

10

|

Cortex-M7_0 ITCM

|

單比特錯誤、多比特錯誤、特徵信息及偏移的錯誤地址

|

|

11

|

Cortex-M7_0 D0TCM

|

單比特錯誤、多比特錯誤、特徵信息及偏移的錯誤地址

|

|

12

|

Cortex-M7_0 D1TCM

|

單比特錯誤、多比特錯誤、特徵信息及偏移的錯誤地址

|

|

13

|

Cortex-M7_1 ITCM

|

單比特錯誤、多比特錯誤、特徵信息及偏移的錯誤地址

|

|

14

|

Cortex-M7_1 D0TCM

|

單比特錯誤、多比特錯誤、特徵信息及偏移的錯誤地址

|

|

15

|

Cortex-M7_1 D1TCM

|

單比特錯誤、多比特錯誤、特徵信息及偏移的錯誤地址

|

|

16

|

DMA TCD

|

單比特錯誤、多比特錯誤、特徵信息及偏移的錯誤地址

|

|

17

|

Flash memory port p0

|

單比特錯誤、多比特錯誤、絕對錯誤地址

|

|

18

|

Flash memory port p1

|

單比特錯誤、多比特錯誤、絕對錯誤地址

|

|

19

|

Flash memory port p2

|

單比特錯誤、多比特錯誤、絕對錯誤地址

|

其中需要注意以下幾點:

-

對於 S32K342、S32K341、S32K322、S32K312、S32K311 這些型號而已是沒有 SRAM1 的

-

Cache 控制器不會報告錯誤地址以及錯誤特徵信息

-

對於 S32K312 和 S32K211,由於只有單核,因此 Cortex-M7_1 對應的 Cache 和 RAM 也是沒有的,Flash Memory p2 也沒有

四、功能概述

ERM 模塊主要包含有以下寄存器:

|

寄存器

|

描述

|

|---|---|

|

CRn(n = 0~2)

|

ERM 配置寄存器

|

|

SRn(n = 0~2)

|

ERM 狀態寄存器

|

|

EARn(n = 0~1、10~21)

|

ERM 內存錯誤地址寄存器

|

|

SYNn(n = 0~1、10~21)

|

ERM 錯誤特徵寄存器

|

|

CORR_ERR_CNTn(n = 0~21)

|

ERM 內存可矯正錯誤計數寄存器

|

-

CRn 寄存器主要配置每個通道的中斷通知,每個通道都包括單比特錯誤和多比特錯誤兩種錯誤事件的通知

-

SRn 寄存器主要記錄每個通道的錯誤事件、每個通道的錯誤事件都包括單比特錯誤和多比特錯誤

-

EARn 寄存器主要記錄發生錯誤時的地址信息

-

SYNn 寄存器主要記錄錯誤的特徵信息,標識可校準的單比特數據翻轉或者不可校準的單比特地址翻轉的相對位置信息

-

CORR_ERR_CNTn 寄存器主要記錄單比特錯誤出現的次數

當出現了單比特錯誤事件時,ERM 模塊會進行以下處理:

-

SRx 寄存器中對應的 SBCn 位會置位,對該事件進行記錄

-

增加錯誤計數,CORR_ERR_CNTn 寄存器值加一

-

記錄對應的訪問地址,保存在 EARn 寄存器中

-

存儲 ECC 錯誤的特徵,第幾個位錯誤,保存在 SYNn 寄存器

當不可校準的錯誤事件(多比特錯誤)發生時,ERM 模塊會進行以下處理:

-

SRn 寄存器中對應的 SBCn 位會置位,對該事件進行記錄

-

記錄對應的訪問地址,保存在 EARn 寄存器中

-

存儲 ECC 錯誤的特徵,第幾個位錯誤,保存在 SYNn 寄存器

ERM 模塊的操作流程如下:

-

初始化內存為已知的值以保證正確的 ECC 校驗碼被存儲

-

在內存初始化時如果 ERM 捕獲到了 ECC 錯誤事件,則清除對應的 SRx 寄存器中對應的值

-

操作 CRx[ESCIEn] 和 CRx[ENCIEn] 寄存器的值來使能 ERM 模塊的中斷

五、參考資料

《S32K3XXRM.pdf》,Rev 9,2024.07

評論