1. 簡介

本文介紹如何使用 NXP 提供的 AUTOSAR MCAL 軟體包創建 EB 配置工程調整 MCU 內核時鐘頻率。

1.1 需求組件

軟體組件:

- 配置軟體:EB tresos Studio 27.1;

- RTD 版本:4_2.0.0;

2. EB tresos Studio 配置

AUTOSAR 環境的各模塊配置需要使用 EB 軟體進行配置,創建 S32K344 EB 配置工程添加 MCU 模塊配置軟體默認使用 S32K344 內部晶振 Fast IRC(FIRC)作為時鐘源為 CORE_CLK、AIPS_PLAT_CLK、AIPS_SLOW_CLK、HSE_CLK、DCM_CLK、LBIST_CLK、QSPI_MEM_CLK 等時鐘提供時鐘頻率。FIRC 時鐘只有 48MHz,然而 S32K344 內核時鐘最大支持到 160MHz,FIRC 作為時鐘源無法滿足需求需要調整配置使 S32K344 內核時鐘頻率達到 160MHz 以滿足應用需求。

2.1 McuFXOSC 配置

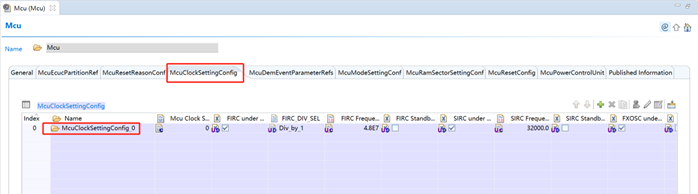

EB 中添加 MCU 模塊後,修改 MCU 內核時鐘僅需修改 McuClockSettingConfig 頁面內配置即可,雙擊 McuClockSettingConfig_0 進入詳細配置頁面。

圖 2.1-1 McuClockSettingConfig 配置頁面

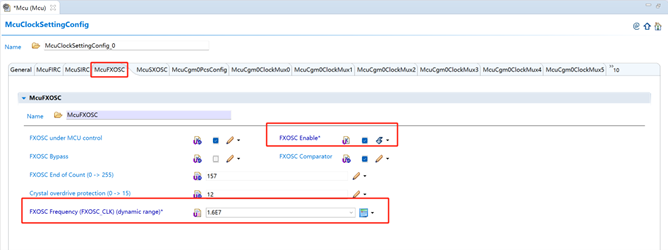

進入詳細配置頁面首先修改 McuFXOSC 配置,McuFXOSC 配置與 MCU 外部晶振保持一致。首先勾選 FXOSC Enable 選項框,隨後在 FXOSC Frequency (FXOSC_CLK) 內填入外部晶振頻率,晶振頻率範圍為 8MHz 到 40MHz,該示例使用外部晶振為 16MHz。

圖 2.1-2 McuFXOSC 配置頁面

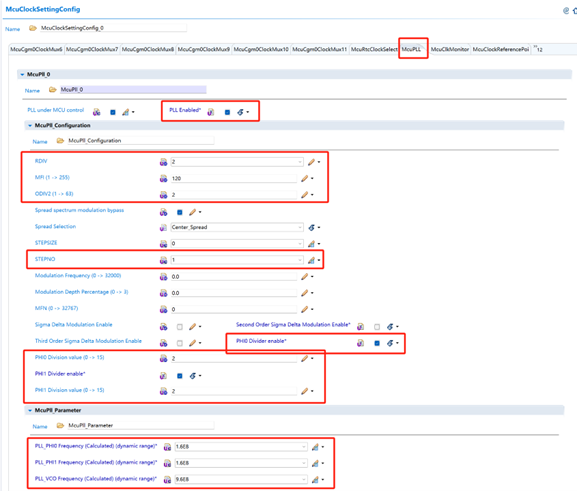

2.2 McuPLL 配置

配置外部時鐘後需要使用 PLL 將外部晶振頻率倍頻到所需要頻率。在 McuPLL 頁面先要勾選 PLL Enable 使能 PLL 功能,然後填入配置數據。RDIV 是分頻係數常規值為 2;MFI 為倍頻係數常規值為 120;ODIV2 為分頻係數常規值為 2;STEPNO 為設置 PLL 值常規值為 1,其餘值保持默認即可。除以上值修改還需勾選 PHI0 Divider enable/ PHI1 Divider enable 使能 PHI0 與 PHI1 時鐘並在 PHI0 Division value/PHI1 Division value 內填入分頻係數常規值為 2。

設置以上配置後還需在 PLL_PHI0 Frequency(Calculated)、PLL_PHI1 Frequency(Calculated)、PLL_VCO Frequency(Calculated)內填入時鐘頻率值。

1、PLL_VCO Frequency(Calculated)值計算方式相同為 Fre=(FXOSC_Fre/RDIV)*MFI;以本文配置為例:

- FXOSC_Fre=16MHz;

- RDOV=2;

- MFI=120;

所以 PLL_VCO Fre=(16/2)*120=960MHz;

2、PLL_PHI0 Frequency(Calculated)與 PLL_PHI1 Frequency(Calculated)值計算方式相同為 Fre=(PLL_VCO Fre/ODIV2)/(STEPNO+PHI Division value)。以本文配置為例:

- PLL_VCO Fre=960MHz;

- ODVIV2=2;

- STEPNO=1;

- PHI0 Division value=2;

- PHI1 Division value=2;

所以 PLL_PHI0 Fre=(960/2)/(1+2)=160MHz;PLL_PHI1 Fre=(960/2)/(1+2)=160MHz(PLL_PHI0 Frequency 與 PLL_PHI1 Frequency 僅計算公式相同,本文由於使用需求配置為相同頻率,可按照使用需求配置成所需頻率,兩無頻率無需相同)。

圖 2.2-1 McuPLL 配置頁面

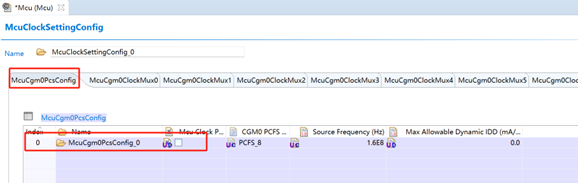

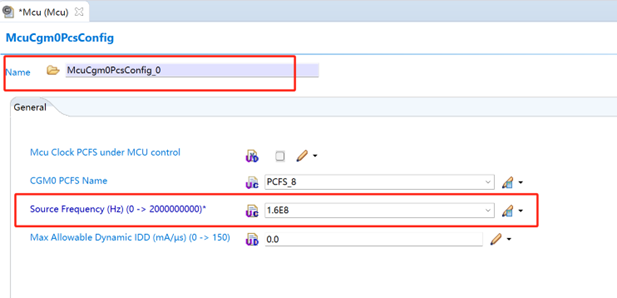

2.3 McuCgm0PcsConfig 配置

配置好 PLL 後需要對配置其他時鐘,頁面切換到 cuCgm0PcsConfig 內雙擊 McuCgm0PcsConfig_0 進入詳細配置頁面。在詳細配置頁面將 Source Frequency 填入與 PLL_PIH1 Frequency 相同數值,以本示例為例填入值為 160MHz。

圖 2.3-1 McuCgm0PcsConfig 配置圖

圖 2.3-2 McuCgm0PcsConfig_0 詳細配置圖

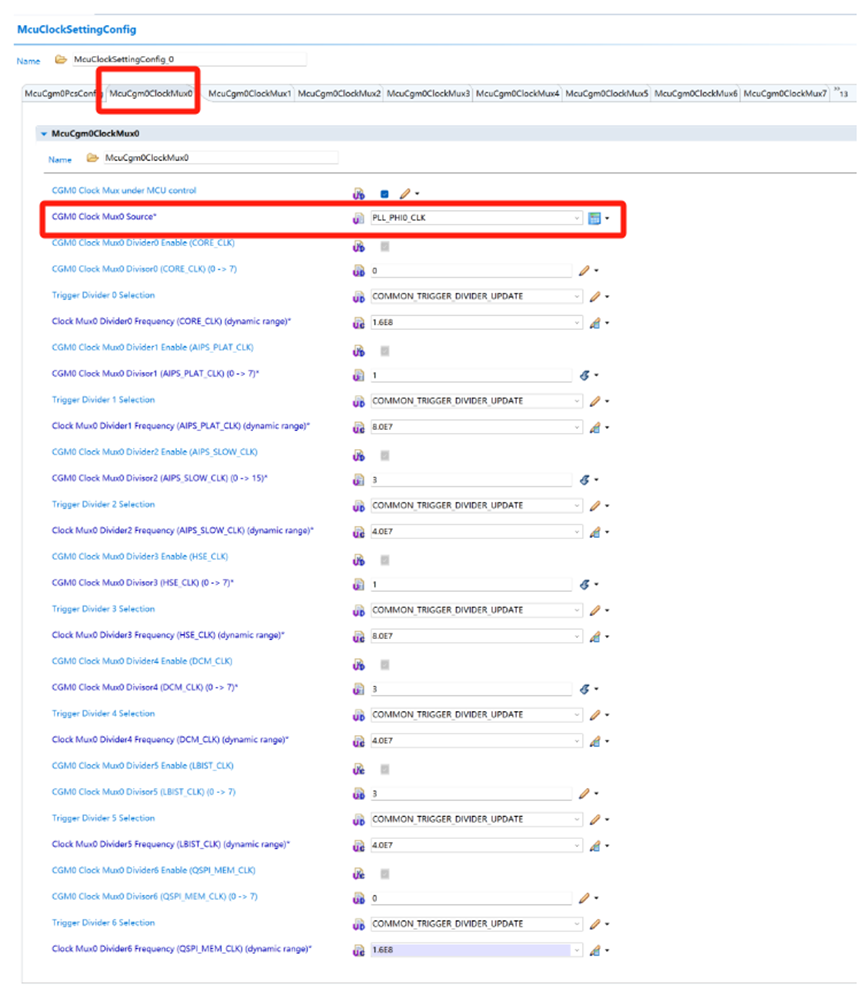

2.4 McuCgm0ClockMux0 配置

完成以上配置後需要切換到 McuCgm0ClockMux0 頁面內對 CORE_CLK、AIPS_PLAT_CLK、AIPS_SLOW_CLK、HSE_CLK 等時鐘進行配置。配置 MCU 時鐘時需要注意 CGM0 Clock Mux0 Source 與各時鐘分頻值與時鐘頻率:CGM0 Clock Mux0 Source 選項可在 FIRC_CLK 和 PLL_PHI0_CLK 間選擇,該示例中 FIRC_CLK 時鐘頻率為 48MHz,PLL_PHI0_CLK 時鐘頻率為 160MHz,CGM0 Clock Mux0 Source 須選擇 PLL_PHI0_CLK 選項才可以是 CORE_CLK 頻率為 160MHz;各模塊時鐘分頻係數與時鐘頻率須相匹配,同時分頻係數比實際分頻係數減 1,以本文為例:

AIPS_PLAT_CLK 時鐘頻率為 80MHz 從 PLL_PHI0_CLK 時鐘 2 分頻得到,因此 AIPS_PLAT_CLK 時鐘的分頻係數為 2-1=1,時鐘頻率為 160/2=80MHz。

其它時鐘配置規則相同,S32K344 部分時鐘存在頻率上限具體上限規則可查閱 S32KXX 系列 MCU 用戶參考手冊,常用分頻係數與頻率如下。

- CORE_CLK:

- Divisor:0;

- Frequency:160MHz

- AIPS_PLAT_CLK:

- Divisor:1;

- Frequency:80MHz

- AIPS_SLOW_CLK:

- Divisor:3;

- Frequency:40MHz

- HSE_CLK:

- Divisor:1;

- Frequency:80MHz

- DCM_CLK:

- Divisor:3;

- Frequency:40MHz

- LBIST_CLK:

- Divisor:3;

- Frequency:40MHz

- QSPI_MEM_CLK:

- Divisor:3;

- Frequency:160MHz

圖 2.4-1 Platform 配置頁面圖

按以上配置即可將 S32K344 MCU 內核時鐘從 48MHz 切換到 160MHz,由於篇幅所限本文僅介紹 S32K344 MCAL Mcu 模塊部分內容,如想了解更多資料與設計,請聯繫我們 atu.sh@wpi-group.com。

3. 參考文獻

[1] S32K3XX Reference Manual.pdf,NXP

[2] S32K3XX Data Sheet.pdf,NXP

歡迎在博文下方留言評論,我們會及時回復您的問題。

如有更多需求,歡迎聯繫大聯大世平集團 ATU 部門:atu.sh@wpi-group.com 作者:Hobo

更多資訊,請掃碼關注我們!

評論