嘿,小夥伴們,你們有沒有遇到過那種項目里邏輯電路多到讓你眼花繚亂的情況?別擔心,今天給你們推薦一篇超級實用的技術文章——《利用單片機實現複雜的分立邏輯》,作者是Microchip的“應用工程師”Robert Perkel!

Robert在文章里告訴我們,傳統分立邏輯器件雖然好用,但BOM一多,PCB面積就大,頭疼啊!不過,Microchip的PIC16F13145系列單片機里有個叫CLB的神秘外設,簡直就是硬體邏輯的“變形金剛”!

這CLB不僅能實現複雜的邏輯功能,還能精簡BOM,讓你的設計變得超級簡潔。而且,它還有個超酷的“合成器”工具,就像魔法棒一樣,點點畫畫就能生成配置邏輯。哪怕你是Verilog高手,也能輕鬆導入自己的代碼!

文章里還舉了兩個超讚的例子:一個是7段顯示轉換器,另一個是SPI至WS2812轉換器。看完這些,你會發現,原來單片機還能這麼玩!

趕緊去看看吧,說不定你的下一個項目就能用上這個“魔術師”了!讓你的設計從此告別繁瑣,走向簡潔高效!

利用單片機實現複雜的分立邏輯

開發人員可利用 PIC16F13145 系列單片機中的可配置邏輯模塊(CLB)外設實現硬體中復 雜的分立邏輯功能,從而精簡物料清單(BOM)並開發定製專用邏輯。

Microchip Technology Inc. 8 位單片機業務部

應用工程師

Robert Perkel

在許多嵌入式系統應用中,通常都會使用分立式邏輯器件,例如 74'HC 系列。這些 邏輯器件的優勢在於可以獨立於單片機(MCU)工作,並且響應速度比軟體快得多。但 是,這些器件會增加物料清單(BOM)並且需要占用額外的 PCB 面積。

為了解決這一問題,Microchip 的許多單片機都集成了一種名為可配置邏輯單元(CLC)的外設(在 PIC® MCU 上)或名為可配置定製邏輯(CCL)的類似外設(在 AVR® MCU 上)。這兩種外設都實現了軟體定義的定製邏輯,可以獨立於 CPU 執行。換句話說, 一旦設置了定製邏輯功能,其行為就獨立於單片機。

但是,這兩種外設存在限制,即每個實例的邏輯數量非常小。每個 CLC 大約相當於 一個查找表(LUT),而 CCL 相當於一個內部具有幾個獨立 LUT 的實例。這兩種外設的功 能非常強大,可用於開發簡單邏輯電路、將各種信號混合在一起以及與其他硬體外設相集 成。例如,硬體按鈕去抖、WS2812 輸出生成和正交解碼這些示例都需要使用這兩種外設, 但單片機中這兩種外設的數量並不多,因此限制了應用的複雜度。

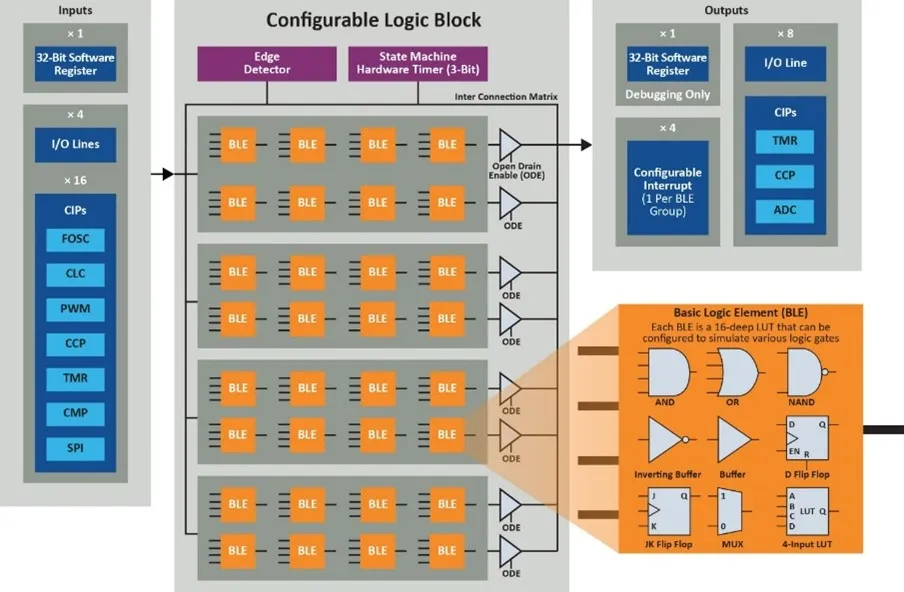

為了支持更複雜的應用,PIC16F13145 系列單片機引入了一種名為可配置邏輯模塊(CLB)的新型邏輯外設(如圖 1 所示)。請注意,CLB 並不會取代 CLC 或 CCL 外設,器件 可以同時配備 CLC/CCL 和 CLB。

圖 1—— CLB 框圖

PIC16F13145 系列單片機上的 CLB 包含四個邏輯組,每組包含八個 BLE。不同邏輯 組的 BLE 之間彼此連接——每個邏輯組代表兩個 GPIO 輸出和一個可選的 CPU 中斷。當工 作電壓為 5.5V 時,BLE 的傳播時間典型值小於 6 ns。整個結構中的所有 BLE 共用一個公共 時鐘,其時鐘源與可選的時鐘分頻器一起在軟體中進行配置。CLB 可以使用單片機的內部 時鐘源之一或外部提供的時鐘源。

該外設從單片機的存儲器中進行初始化,之後可通過外設引腳選擇(PPS)直接從 自身結構中控制引腳。用戶可通過 PPS 重新分配用於硬體外設的 I/O 引腳,從而獲得更大 的設計靈活性。舉例來說,如果 SPI 時鐘先前使用 RA1,但使用 RA6 會更有利,那麼便可 以通過 PPS 重新映射引腳。

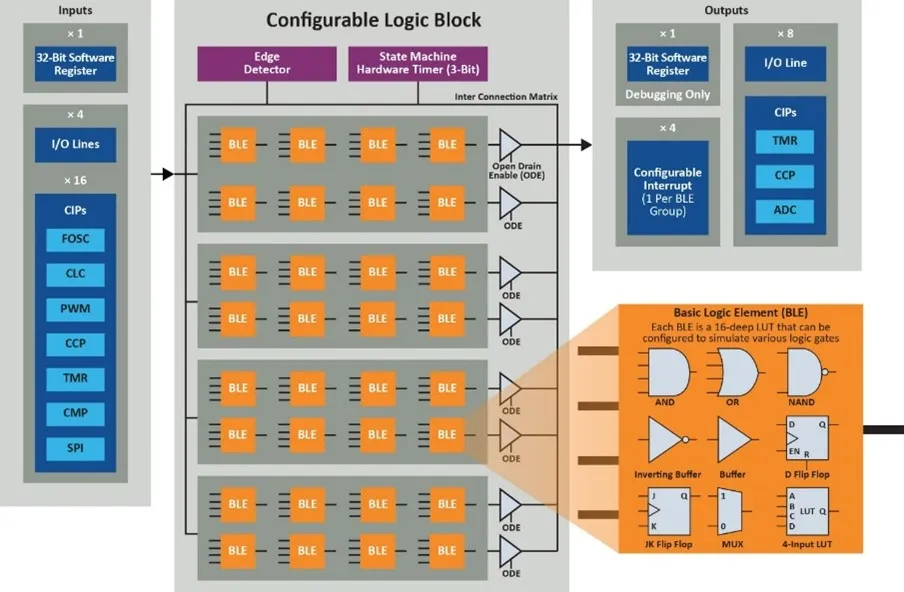

CLB 中的其他元件包括專用的 3 位硬體定時器(帶解碼輸出)、用於輸入信號的邊 沿檢測器以及 32 位輸出寄存器(用於調試)。單片機上的其他獨立於內核的外設(CIP) 輸出可用作 CLB 的輸入,以便實現更複雜的設計。由於 CLB 比 CLC 或 CCL 複雜得多,因此 Microchip 開發了一款名為 CLB 合成器的新 工具。CLB 合成器提供了一個用於配置邏輯的圖形界面,如下面的圖 2 所示。除了邏輯原 語之外,該工具還支持更高級的邏輯模塊庫(可由用戶預先提供或定製)。

與該圖形工具交互時,後台會自動生成一個 Verilog 模塊用於合成。如果開發人員 更喜歡編寫自己的 Verilog 或者已準備好該文件,則可以將其作為模塊直接導入工具。

圖 2——已打開相移鍵控(PSK)示例的 CLB 合成器

CLB 合成器的輸出是一個匯編文件,其中包含用於設置 CLB 的比特流和一些用於將 CLB 配置為外設的源代碼。該工具可通過 MPLAB®代碼配置器(MCC)或獨立在線工具運 行。MCC 是一款代碼生成實用程序,允許用戶使用可視化界面來設置和配置單片機中的 外設。當硬體外設完成配置後,MCC 將生成初始化代碼和器件 API。

在運行時,使用板上硬體直接從程序存儲器加載 CLB 比特流。這種實現的好處在 於如果在程序運行時需要更改 CLB 配置,則可以使用存儲在器件存儲器中的不同比特流 重複執行加載過程。

為了演示 CLB 的應用,我們創建了一系列用例示例。這裡我們將討論兩個示例:7 段顯示轉換器和 SPI 至 WS2812 轉換器。用例示例可作為構件複製以用作完整解決方案的 一部分。這裡旨在展示該外設的實用性以及它能夠為設計帶來哪些價值。

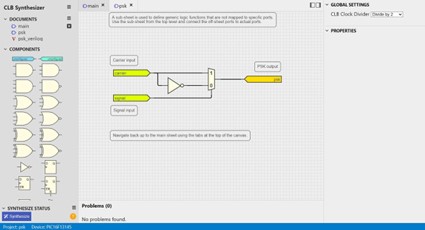

第一個用例是 7 段顯示轉換器。7 段顯示器可通過一組普通的 I/O 引腳驅動,但標 准實現通常需要使用軟體定義的查找表將輸入數字轉換為適合顯示器的正確輸出模式。在 該實現中,CLB 充當硬體查找表。所需的輸出字符(0 到 F)從軟體加載到 CLB 輸入寄存 器中。顯示器的每個輸出段均由 LUT 控制,以將輸入映射到輸出。

該用例示例在內部用於構建計時系統的新控制板。最初的用戶界面是在 20 世紀 80 年代使用 74'HC 系列邏輯開發。使用 CLB 後,一個 20 引腳的單片機即可實現電路板上的 顯示和鍵盤邏輯,極大地精簡了物料清單(BOM)。圖 3 並排給出了兩種方案以供比較。

圖 3——原 PCB 與新 PCB 的並排比較。該示例由 Josh Booth 開發。

下一個示例是 SPI 至 WS2812 轉換器。WS2812 是一種單線串行協議,用於通過脈 寬調製控制 LED 陣列。在本例中,SPI 硬體用作要發送到 LED 的數據的移位寄存器,而 CLB 用於將 SCLK 和 SDO 轉換為預期的輸出。

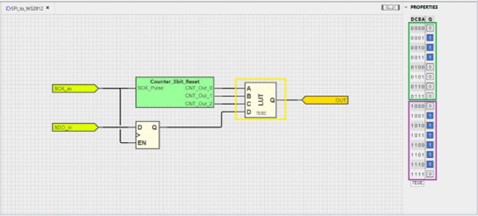

在本例中,這是通過單觸發 3 位計數器、帶使能功能的 D 鎖存器和 4 輸入 LUT 來 實現,如下面的圖 4 所示。該實現的技巧體現在 SPI 和 CLB 的時鐘源。SPI 時鐘設置為空 閒高電平、在上升沿改變狀態並以 WS2812 輸出的頻率(800 kHz)運行,而 CLB 的時鐘 源以前者 10 倍的頻率(8 MHz)運行。當 SCLK 為低電平時,將觸發 3 位計數器並開始計 數。當計數到 7(0b111)時,3 位計數器將停止並保持為 0,直到時鐘脈衝的下一個低電 平周期為止。

計數器的輸出與輸出數據的鎖存版本一起饋入 4 輸入 LUT。這將設置數據的輸出模 式,如圖 4 的右側所示。計數器復位後,計數器輸出將保持為 0 以完成循環。之後,可 根據需要發送 SPI 硬體中的下一個字節,重複該循環。

圖 4——SPI 至 WS2812 轉換器框圖(由 Petre Teodor-Emilian 開發)

這兩個示例都證明了單片機內部分立邏輯的優勢。硬體外設可將 CPU 從各種任務 中解放出來,從而縮短響應時間並降低功耗,同時減少元器件數量。有了 CLB,之前無法 在單片機內部實現的複雜應用現在都可以順利開發。目前,可前往 Microchip 直銷網站或 其他代理商處購買 PIC16F13145 系列單片機來獲取 CLB。

評論