在電源晶片的數字控制方法中,經常引入延遲環節。在引入延遲環節後,分析電路響應的方法特別是定量計算會變得比較複雜。本文通過對一種有延遲環節的burst控制方法的分析,提出一種可用於工程實踐的方法,那就是通過電路分析,用在靜態工作點作瞬態響應仿真的方法得到參數調試方向。

本文作者:汪月亮

英飛凌消費、計算與通訊業務大中華區 高級主任工程師

關鍵詞:延遲環節,burst控制方法,靜態工作點,等效仿真模型,瞬態響應

1、引言

在現代電源晶片設計中,模數結合的方法已經很常見。數字控制的方法的好處是:抗干擾能力強、控制精確、靈活性好、系統的兼容性好、方便實現電源管理。在數字控制模式中,可以輕鬆引入延遲環節,讓控制更加靈活,高效。這種方法帶來的問題是,在引入延遲環節後,在電源工程設計中,最常見的用零極分布來分析電路響應的方法不再適用。引入延遲環節後,通常傳遞函數用(G(s)=eτs)來表示,但在真實過程中,τ的不確定性讓分析難度加大。在工程實踐中,仿真的辦法,是快速理解與找到解決問題的有效手段。那麼如何設定仿真模型可以得到理想的結果就很重要。本文將基於對一種burst控制方法的理解,給出一種在靜態工作點作瞬態響應仿真的方法來獲得對這類問題的理解與工程解決方法。

2、一種有延遲環節的burst控制方法

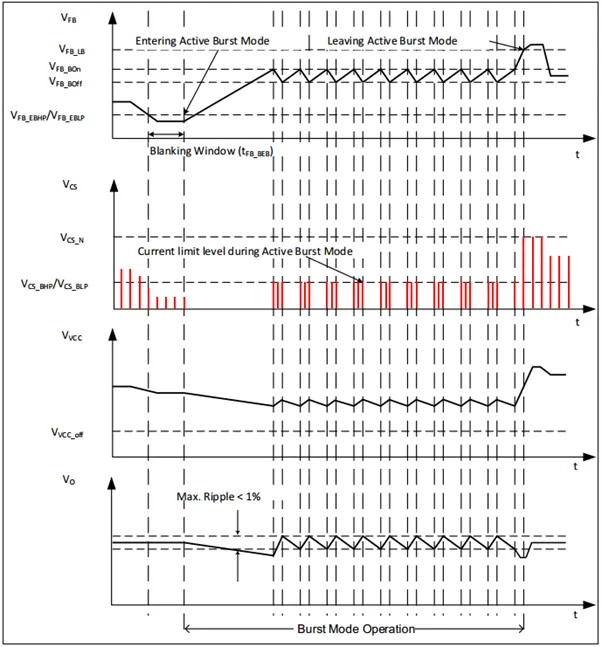

在這種控制方法裡,如圖一所示,當晶片進入主動burst模式後,晶片停止發出驅動脈衝,也就是圖中VCS信號沒有出現的區間,因為輸出電壓的下跌,反饋作用的拉電流(一般是光藕的作用)消失,晶片的FB引腳上的電壓在內部電流的作用下開始快速上升,直到VFB_BON信號,並重新喚醒晶片發出驅動脈衝,讓下跌中的輸出電壓回歸正常值。

上面的分析過程是一種設計想得到的理想狀態。在實際應用中,我們會發現,在輸出電容較小,不合理的反饋設計下,FB引腳上的電壓快速上升的時間會遠大於晶片理想的設計時間,輸出電壓的跌落幅度變得不可接受。理論上應該消失的從光藕反饋過來的拉電流並不會因為輸出電壓的跌落馬上消失,這將導致,輸出電壓跌落過多,而且傳統經典的適用於線性時不變系統的控制理論,無法很好的解釋與解決這個問題。

burst控制方法如下圖

圖一 burst控制方法

3、常見的控制電路及靜態工作點的分析

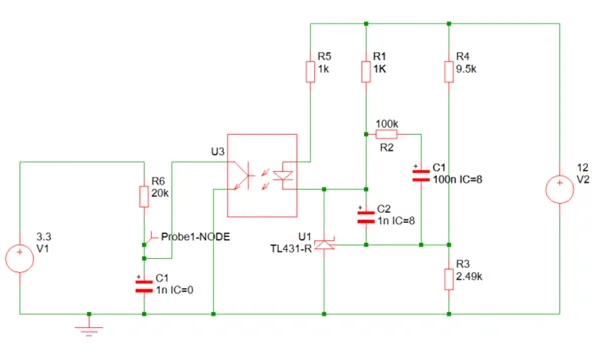

圖二 常見反饋電路

如圖二所示,這是一種常見的由TL431與光藕組成反饋電路,反饋補償是Ⅱ類補償電路。輸出電壓為12V。靜態工作點主要是確定兩個反饋電容在穩態時的電壓值。

首先定義光藕的工作狀態:CTR: 50%; VF: 1.45V

定義光藕的工作電流:IF: 0.33mA (備註:此電流由晶片工作狀態決定)

定義TL431參考腳電壓:Vref: 2.5V

定義輸出電壓:Vout=12V

反饋補償的電容(C1,C2)上的電壓為:Vout-VF-(IF*R5)-Vref

得到反饋補償的電容(C1,C2)上的電壓為:12V-1.45V-(0.33mAx1k)-2.5V≈8V

由此得到在12V穩態下,C1,C2上的電壓為8V

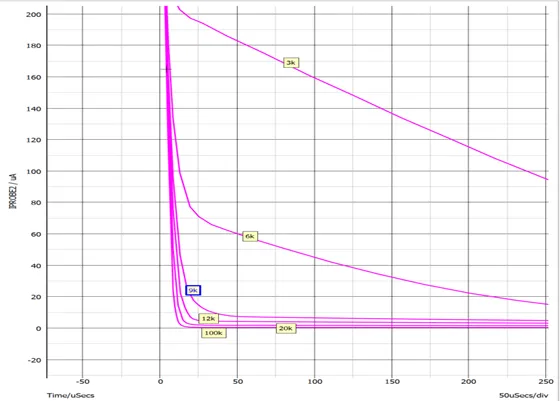

4、仿真建立方法與等效仿真模型

實際工程樣機為一台60W, 12V/5A的電源,控制晶片的burst控制方法如前圖一所示。

1、假定設計目標為進入burst態,重新發出驅動時,12V輸出電壓的跌落小於0.5V,以此設定仿真的電壓源,如圖所示,12V的輸出,電壓源取11.5V

2、反饋網絡取值等同於實際電路取值

3、用二極體取代光藕,去光藕的CTR動態

4、用流經二極體的電流等效晶片反饋 (FB) 電壓的變化速率

5、設定反饋電容的初始電壓為系統輸出電壓為12V穩態時的初始電壓(如圖為8V)

6、選定SIMETRIX為仿真工具,分析模型選擇瞬態分析。

建立的仿真電路如下圖三所示。

圖三 仿真電路

這種仿真分析方法的目的是用來幫助理解電路的工作與工程實踐中的元件參數的調試方向。很明顯,流經此二極體的電流會影響電源控制晶片反饋 (FB) 腳上電壓的上升,控制的目標就是,讓這一路電流儘快掉到最小,以得到反饋 (FB) 電壓的上升。

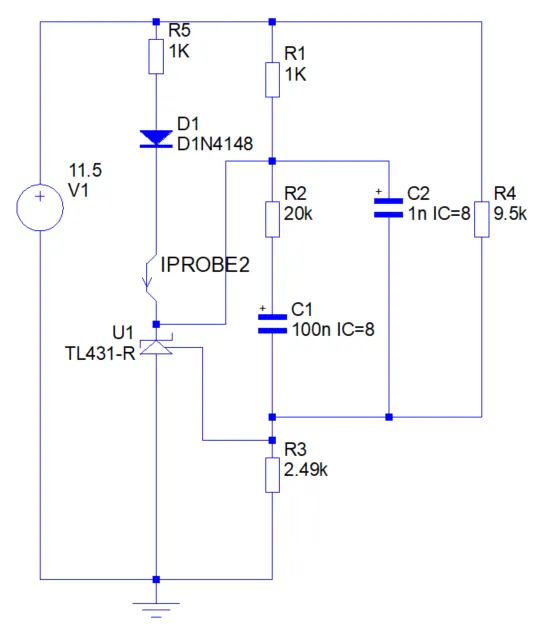

仿真結果如下:

電路的初始參數如圖三所示

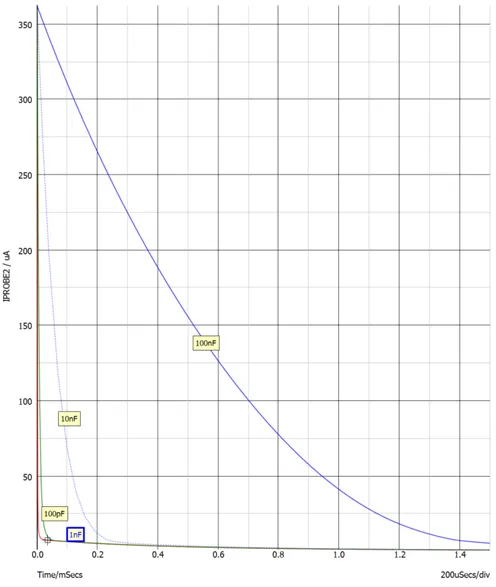

選取不同的反饋電阻值,如圖三中的R2 (3k-100k),對流經光藕的電流IPROB2分析,得到圖四,圖五,不同反饋補償電阻值下的光藕電流隨時間變化規律。

圖四 不同反饋補償電阻值下的光藕電流隨時間變化規律

圖五 不同反饋補償電阻值下的光藕電流隨時間變化規律(放大版)

選取不同的反饋電容值,圖三中的C1 (10nF-1uF) ,對流經光藕的電流IPROB2分析,得到圖六。

圖六 不同反饋補償電容(C1)值下的光藕電流隨時間變化規律

選取不同的反饋電容值,圖三中的C2 (1nF-100nF),對流經光藕的電流IPROB2分析,得到圖七。

圖七 不同反饋補償電容(C2)值下的光藕電流隨時間變化規律

5、仿真結果分析

從仿真的結果看,環路補償的三個參數對流過光藕的電流,即同比於FB上升(延時)到重新開啟輸出驅動的時間,影響很不相同。電阻R2的選擇影響很大,超過一定值後,開始收斂,影響開始變化不大。選好較大值的R2後,與之串聯的C1,對結果影響很小。而極點電容C2,值選的越大,結果越差。

從理論分析來看,如圖三所示,當電源主控晶片停止發驅動,輸出下跌後,TL431的參考電壓低於TL431的基準電壓2.5V。TL431的陰極電壓就會上升,這個上升的電壓會通過反饋補償網絡R1,C1,C2補償TL431的基準電壓,如果基準電壓被重新抬升到2.5V,TL431會重新導通,產生拉電流,這個電流會有部分流過光藕,影響了流過光藕的電流收斂速度,並與陰極上升的電壓建立一定程度的動態平衡。這與仿真的結果是一致的。

6、實驗驗證

在實際應用中,C2的值一般都比較小,主要考慮R2,C1的影響,為此實驗選擇了一台60W,輸出12V/5A的電源, 按照圖三的反饋網絡,選取不同參數,測試FB引腳上的電壓快速上升的時間 (TR),來驗證仿真結果。實際測試中,為了得到系統進出Burst的條件,負載設為動態,從1A到0.3A動態變化。波形八到十三的圖中,曲線C1為實測的FB引腳上的電壓波形,曲線C2為晶片的驅動波形。

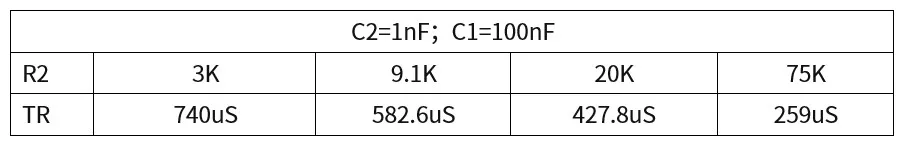

1)選取參數如下:首先定義電容C2的值為1nF, 定義電容C1 的值為100nF,

選取不同的電阻R2的值: 3K, 9.1K, 20K, 75K。(結果見圖八,圖九,圖十,圖十一)

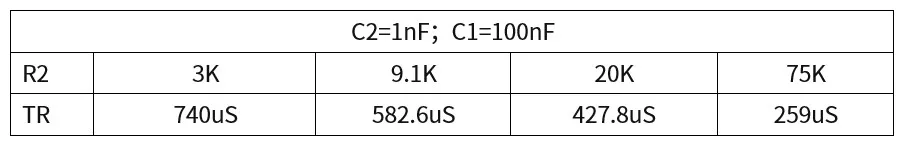

2)選取參數如下:首先定義電容C2的值為1nF,定義R2的值為75K,

選取不同的C1的值: 1uF, 10nF。(結果見圖十二,十三)

實際測試結果如下表一和表二

表一 上升時間隨R2變化表

表二 上升時間隨C1的變化表

圖八 3K/100nF 740uS

圖九 9.1K/100nF 582.6uS

圖十 20K/100nF 427.8uS

圖十一 75k/100nF 259uS

圖十二 75K /1uF 276.6uS

圖十三 75K/10nF 250.6uS

7、結論

從實測的結果來看,反饋電壓(FB)的上升時間與仿真的結果,變化的方向完全一致。因而,這種仿真方法能在這種有延遲環節的burst控制方法中得到響應時間的變化規律,在反饋補償網絡中,選擇較大的反饋電值,與較小的極點電容,有利於讓流過光藕的電流快速收斂至最小值。利用在靜態工作點作瞬態響應仿真的方法可以快速得到近似工程解。

參考文獻

-

ICE5ARXXXBZS數據表,英飛凌科技股份有限公司

-

DEMO 5GSAG 60W1演示板,英飛凌科技股份有限公司

-

Model 310, 0.01Hz - 30MHz Frequency Response Analyzer

-

開關電源環路中的TL431, Christophe Basso

-

Designing control loops for linear and switching power supplies, Christophe Basso

評論