一、概述

NXP MCXN236 是一款高效能的 32 位元 ARM Cortex-M33 微控制器,它具有高達 150 MHz 的 CPU 運算速度,並擁有 1 MB 的 Flash 和 352 KB 的ECC RAM,內建 Smart DMA 技術,可提升數據傳輸效率,它還具備 8 組 Flexcomms 每組皆可宣告為 SPI、I2C、UART 功能,且支援 High Speed USB、2 組 Flex CAN FD、2 組 I3C、5 組 32 bit Timer、此外,它也擴展了 2 個 16 位元 4 通道高速 ADC,最高取樣率可達 2 Msps,並提供了 HLQFP 與 VFBGA 封装,適合應用電競市場、工業自動化、USB週邊、物聯網和消費性電子等高運算和高速 USB 應用需求的設計。

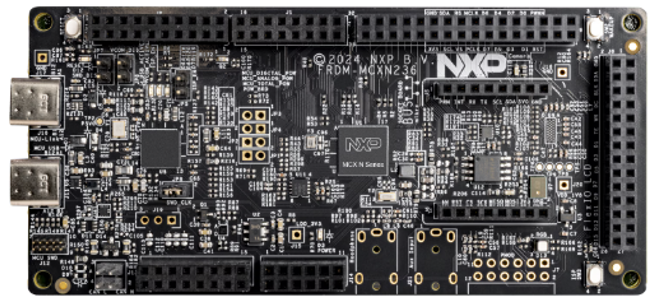

圖 1 ( 註 1 )

圖 1 ( 註 1 )本章節將簡介到的 UART(Universal Asynchronous Receiver/Transmitter)是一種通用的非同步串行通訊協議,用於在電子設備之間進行數據傳輸。

UART通訊使用兩條線(一條用於數據傳輸,一條用於時序控制)進行通訊,並且是非同步的,即數據傳輸時不需要時鐘信號。數據傳輸的速率由波特率(baud rate)來決定,通常可以設置為標準的波特率(如9600、19200、38400等)。

UART通訊通常用於將數據從一個設備傳輸到另一個設備,例如從微控制器到外部設備(如感測器、顯示器、通信模塊等)。

針對 UART 協議網路上有許多文章已經有詳細介紹到,本章節將集中在 MCXN236 UART register 設定上進行使用解析。

二、 需求物件

2.1 硬體

2.1.1 NXP FRDM-MCXN236 EVK 詳細規格如下列網址所示

使用MCUXpresso的FRDM-MCXN236开发板 | NXP 半导体

2.1.2 Type C USB Cable : 1 pcs

2.1.3 USB to RS232 Tool : 1 pcs

2.2 軟體

2.2.1 Keil ( IDE ) 軟體開發環境如下列網址所示

https://www.keil.com/product/

2.2.2 NXP FRDM-MCXN236 SDK 如下列網址所示

欢迎 | MCUXpresso SDK构建工具 (nxp.com)

2.2.3 PC 上的終端機軟體

三、 操作方式

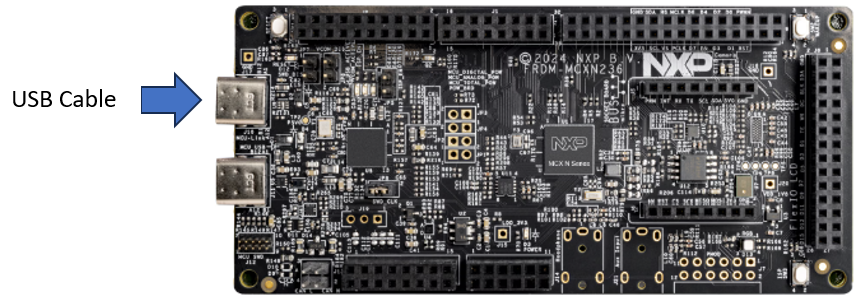

3.1 先將 USB cable 與 FRDM-MCXN236 EVK 的 J10 對接上 ( 如圖 2 ),J10 為 EVK on board 燒錄 IC 的 connector,同時也會對 EVK 進行供電

圖 2 ( 註 1 )

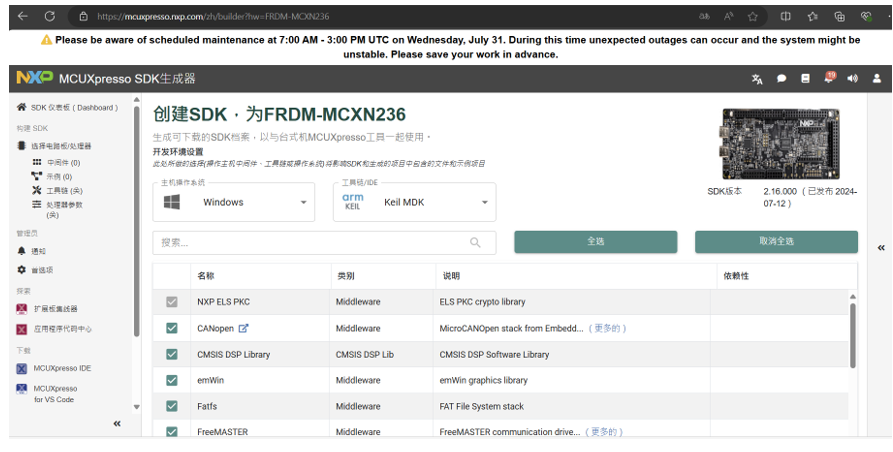

圖 2 ( 註 1 )3.2 本章節將編譯 UART 的設定 function,會參考到 NXP SDK 中的 MCU 的 startup、CMSIS 的相關文件,因此可以到 NXP 官網下載 FRDM-MCXN236 SDK 檔 ( 如圖 3 )

欢迎 | MCUXpresso SDK构建工具 (nxp.com)

圖 3

圖 33.3 有關於初次使用 MCXN236 MCU 所需的配置步驟可參考 “ MCXN236 系列 System clock 參數定解析與實作 ” 的步驟 3.3 ~ 3.9,這邊就不重覆介紹。

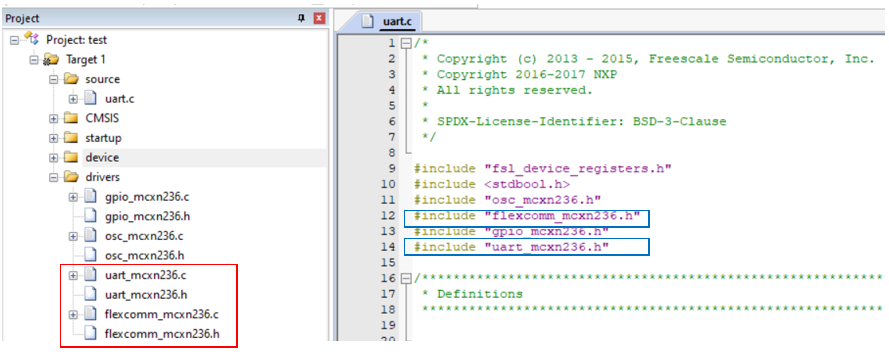

3.4.4,uart_mcxn236.c、uart_mcxn236.h、flexcomm_mcxn236.c、flexcomm_mcxn236.h 複製到圖 4 紅色方框的資料夾,該 4 份文件後緒會說明如何編譯。

圖 4

圖 4將有參考到的文件 include 到 uart.c 中 ( 如圖 4 藍方框 )。

3.5 參考“ MCXN236 系列 System clock 參數定解析與實作 ” 的步驟 3.8 ~ 3.9 將編譯完成的 Code 燒錄到 MCXN236 上

3.6 範例中 UART TX、RX 腳位宣告為 PIO1_9 ( TX )、PIO1_8 ( RX ),將 EVK 上的 PIO1_9 ( TX )、PIO1_8 ( RX ) 與 USB to RS232 Tool 進行對接

四、SDK 參數解析

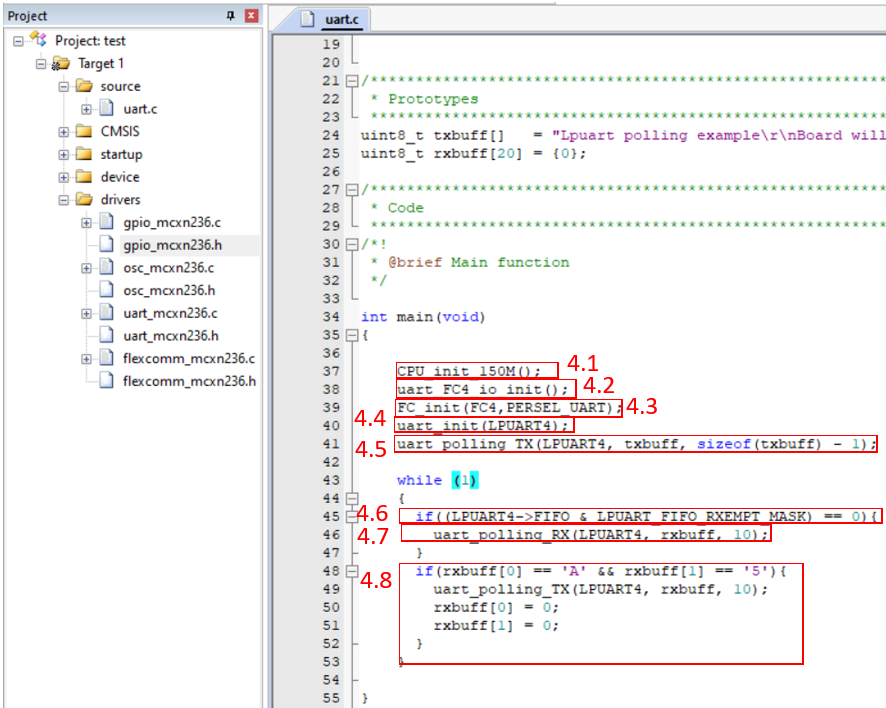

4.1 點選 uart.c,查看 Main 中的內容 ( 如圖 5 ),其中 CPU_init_150M 部分細節可於 “ MCXN236 系列 System clock 參數定解析與實作 ”中查閱到設定細節

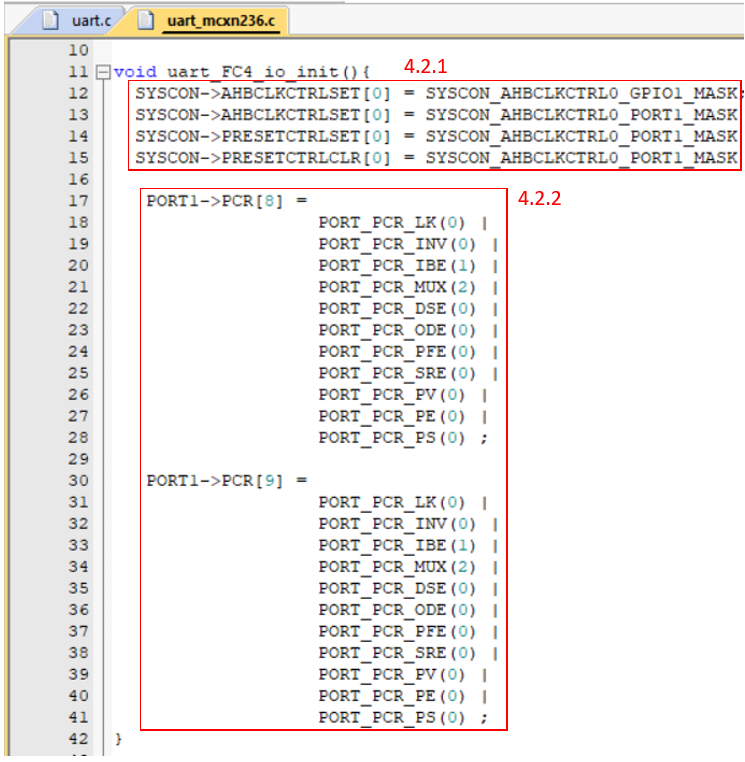

4.2 uart_FC4_io_init 可看到該 Function 編譯在 uart_mcxn236.c 中 ( 如圖 6 )

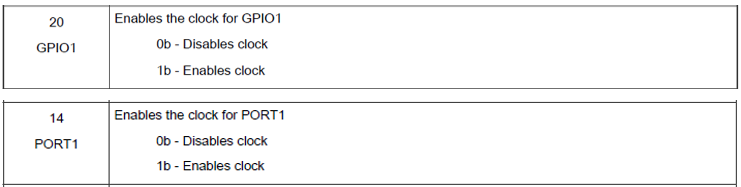

4.2.1 SYSCON->AHBCLKCTRLSET[0] : Enable GPIO1 與 PORT1 Clock ( 如圖 7 ),可參考 MCXN23xRM Page 262 與 263

4.2.2 PORT1->PCR[8] 與 PORT1->PCR[9] 會針對 PORT Pin 的 register 下參數,解析如下, register 功能參數設定可於 MCXN23xRM Page 2414 中參考:

PORT_PCR_LK(0) : Lock Register 參數設定為 0,代表不對該 Port 做 Lock,使用者可在該狀態下自由更改 GPIO P1_8 與 P1_9 中的 PCR 參數

PORT_PCR_INV(0):Invert Input 參數設定為 0,不對 input 訊號做反向功能

PORT_PCR_IBE(1) :Enable Input Buffer,表示 P1_8 與 P1_9 為 digital input

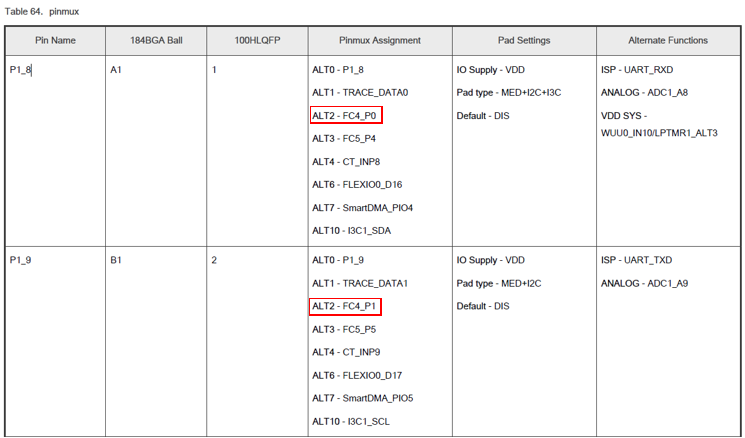

PORT_PCR_MUX(2) :Pin Multiplex Control 設定為 2,表示 P1_8 與 P1_9 為 UART TX、RX 功能,配置在 Pinmux 功能的 ALT2 上 ( 如圖 8 ),MCXN23xRM Page 104

PORT_PCR_DSE(0) :Drive Strength 參數設定為 low

PORT_PCR_ODE(0) :Disable Open Drain 功能

PORT_PCR_PFE(0) :Disable Passive Filter 功能

PORT_PCR_SRE(0) :Slew Rate 設定為 Fast

PORT_PCR_PV(0) :選擇高或低內部上拉電阻值,設定為 Low

PORT_PCR_PE(0) :disable 內部電阻功能開關

PORT_PCR_PS(0) :Input_IO_Status 參數為 0,disable 內部上拉電阻功能

圖 5

圖 5 圖 6

圖 6 圖 7 ( 註 2 )

圖 7 ( 註 2 ) 圖 8 ( 註 2 )

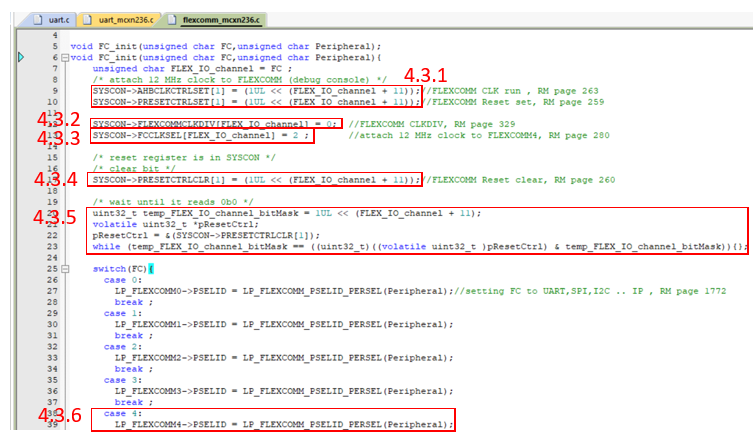

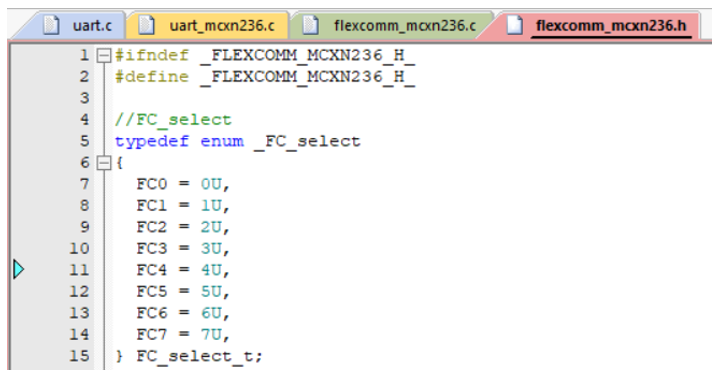

圖 8 ( 註 2 )4.3 FC_init 可看到該 Function 編譯在 flexcomm_mcxn236.c 中 ( 如圖 9 )

* 參數 FLEX_IO_channel 為 FC4 ( 如圖 5 ),實質數值為 4 ( 如圖 10 )

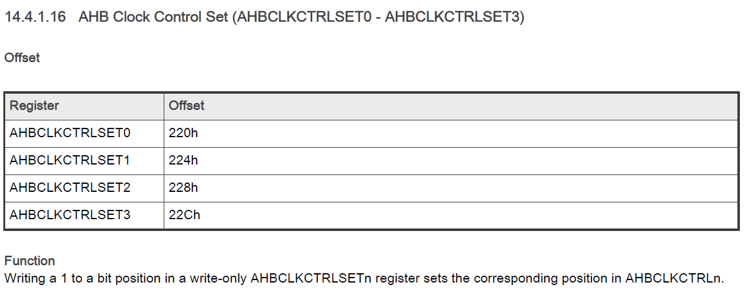

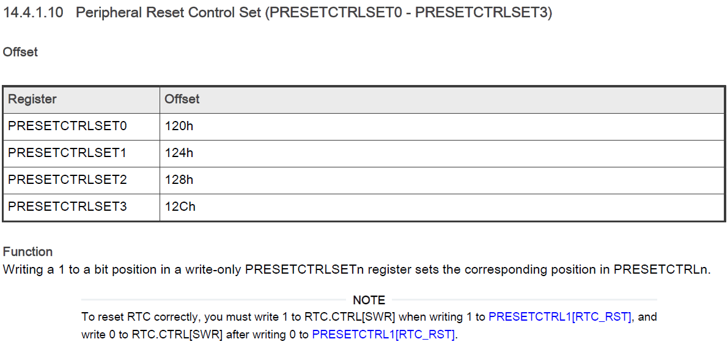

4.3.1 SYSCON->AHBCLKCTRLSET[1] 與 SYSCON->PRESETCTRLSET[1] 將針對指定 AHBCLKCTRLSET 與 PRESETCTRLSET bit 執行 set 與 reset 功能,可參考 MCXN23xRM Page 273 與 259 ( 如圖 11、12 ),指定的 bit 定義可參考 MCXN23xRM Page 266 ( 如圖 13 )

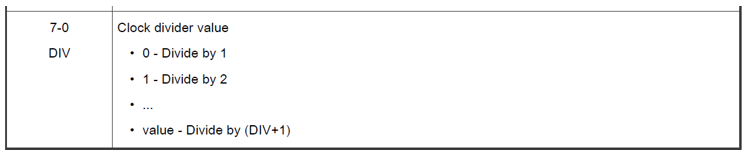

4.3.2 SYSCON->FLEXCOMMCLKDIV[FLEX_IO_channel] 這邊設定 FC4 Clock Source 的除頻參數為 0,代表除頻倍率為 1,可參考 MCXN23xRM Page 329 ( 如圖 14 )

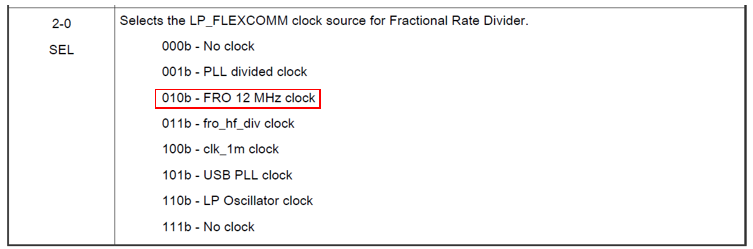

4.3.3 SYSCON->FCCLKSEL[FLEX_IO_channel] 這邊設定 FC4 的Clock Source 為 FRO 12 MHz clock,可參考 MCXN23xRM Page 280 ( 如圖 15 )

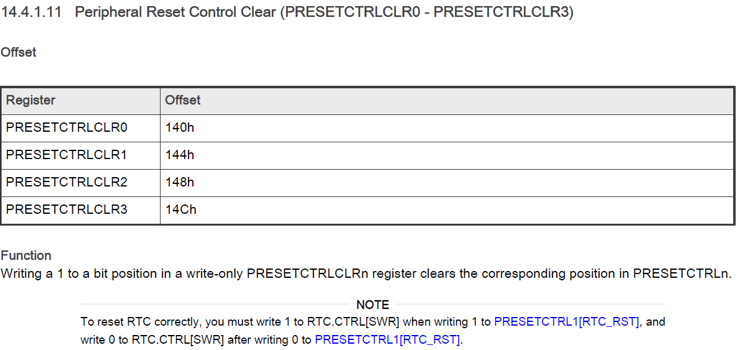

4.3.4 SYSCON->PRESETCTRLCLR[1] 將針對指定 PRESETCTRLCLR bit 執行Clear 功能,可參考 MCXN23xRM Page 260 ( 如圖 16 )

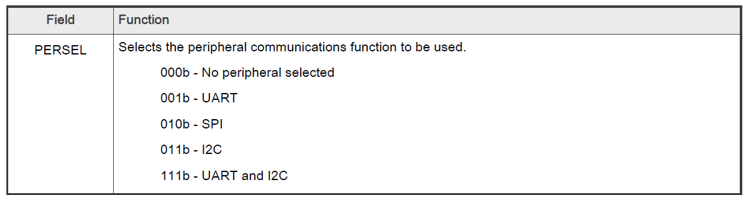

4.3.6 LP_FLEXCOMM4->PSELID 設定 FC4 的功能為 UART,可參考 MCXN23xRM Page 1722 ( 如圖 17 )

圖 9

圖 9 圖 10

圖 10 圖 11 ( 註 2 )

圖 11 ( 註 2 ) 圖 12 ( 註 2 )

圖 12 ( 註 2 ) 圖 13 ( 註 2 )

圖 13 ( 註 2 ) 圖 14 ( 註 2 )

圖 14 ( 註 2 ) 圖 15 ( 註 2 )

圖 15 ( 註 2 ) 圖 16 ( 註 2 )

圖 16 ( 註 2 ) 圖 17 ( 註 2 )

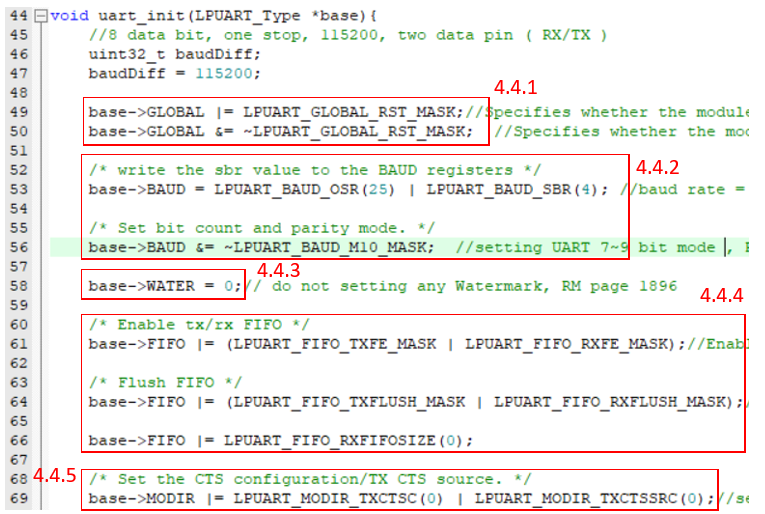

圖 17 ( 註 2 )4.4 uart_init 可看到該 Function 編譯在 uart_mcxn236.c 中 ( 如圖 18 ),解析如下:

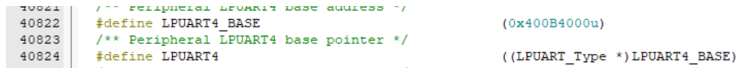

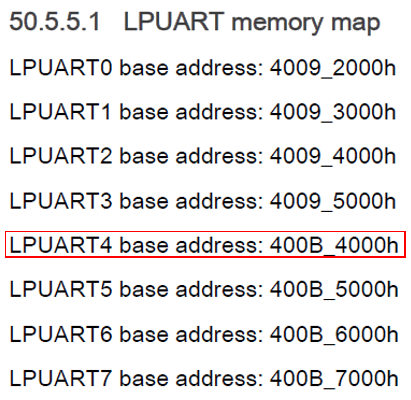

這邊 base 帶入的 address 值為 LPUART4 ( 如圖 19 ),對應 MCXN23xRM Page 1861 ( 如圖 20 )

4.4.1 base->GLOBAL 這邊會對 LPUART4 進行 reset,可參考 MCXN23xRM Page 1865 ( 如圖 21 )

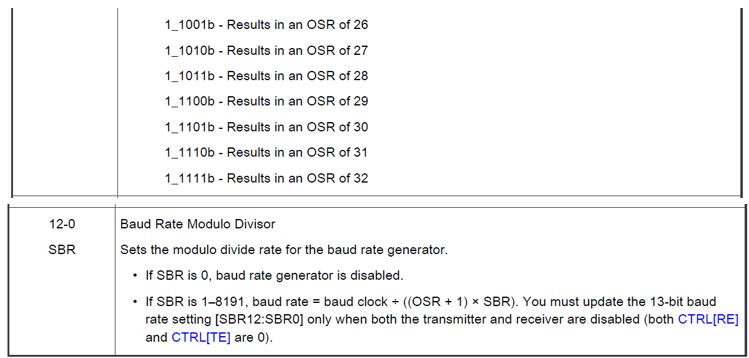

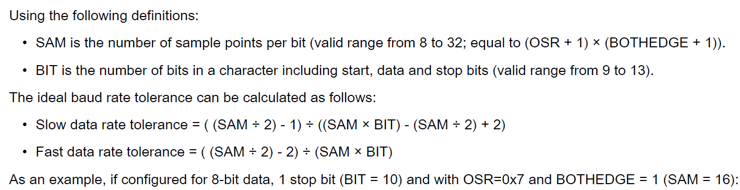

4.4.2 base->BAUD 透過該 register 設定 UART 的 baud rate,計算方式可參考 MCXN23xRM Figure 226 ( 如圖 22 ),設定 OSR 值為 25、SBR 為 4,對照 MCXN23xRM Page 1867,得到圖 22 中的參數值 ( 如圖 23 )

LPUART asynchronous module clock = 12 MHz ( 如步驟 4.3.3 所設定 )

baud rate = 12 MHz / ( 4 x ( 25+1 ) )

得到 baud rate 為 115384 趨近 baud rate 115200,baud rate tolerance 的計算方式可參考 MCXN23xRM Page 1845 ( 如圖 24 ),本次範例中所設定的參數是 Data 8 bit、基偶較驗無開啟,因此圖 24 BIT 參數為 8、BOTHEDGE 參數為 0

SAM = ( OSR +1 ) x ( BOTHEDGE + 1 ) = 26

透過公式可計算出 Slow data rate tolerance 約為 6 %、Fast data rate tolerance 約為 5.28 %

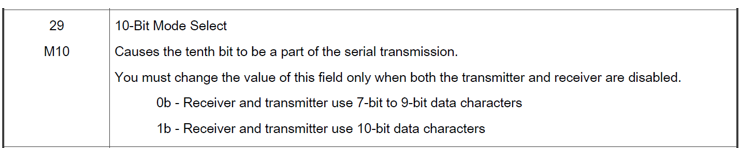

透過 BAUD M10 register 設定 UART 寫入/讀取的 data 為 7~9 bit,可參考 MCXN23xRM Page 1867 ( 如圖 25 )

4.4.3 base->WATER 將 TX、RX 的 Counter 與 Watermark 歸 0,可參考 MCXN23xRM Page 1896

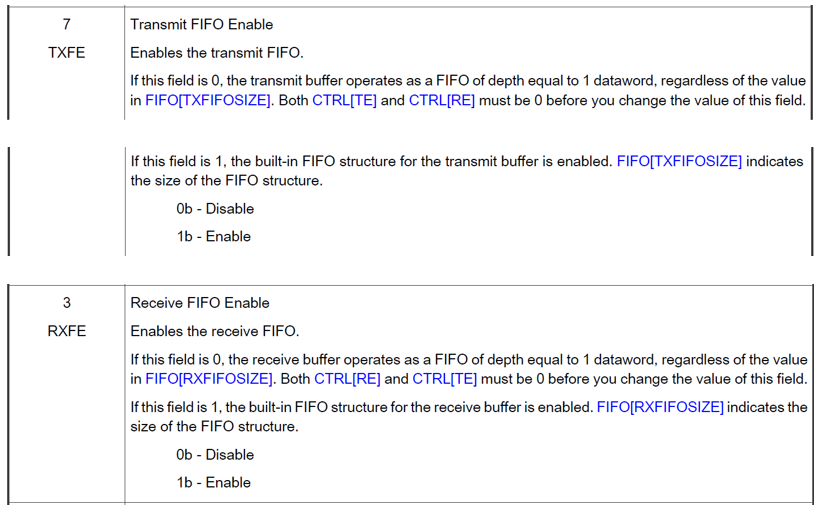

4.4.4 base->FIFO Enable TX、RX FIFO 功能,可參考 MCXN23xRM Page 1894 ( 如圖 26 )

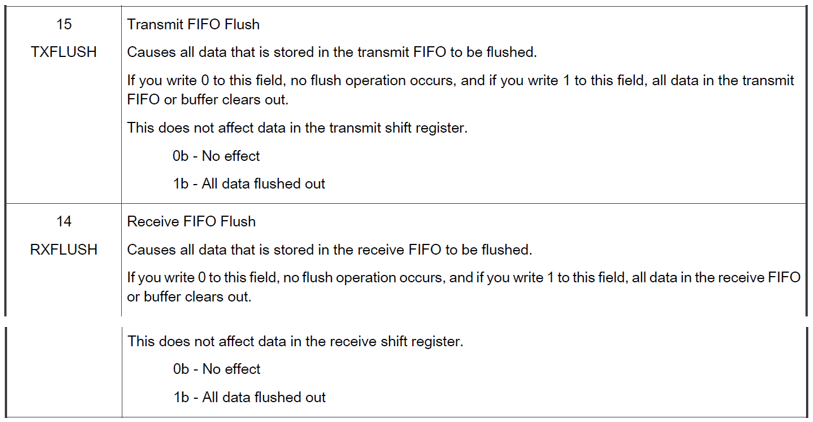

透過 FIFO TXFLUSH、RXFLUSH 清除 TX、RX FIFO 中的 data,可參考 MCXN23xRM Page 1893 ( 如圖 27 )

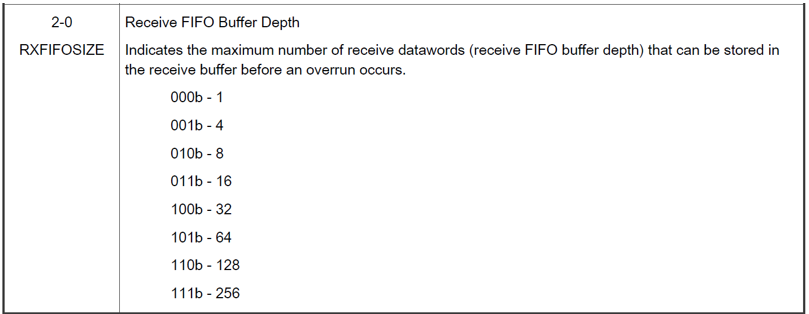

透過 FIFO RXFIFOSIZE 將 RX FIFO Size 設定為 0,表示 FIFO 接收 Depth 為 1,可參考 MCXN23xRM Page 1893 ( 如圖 28 )

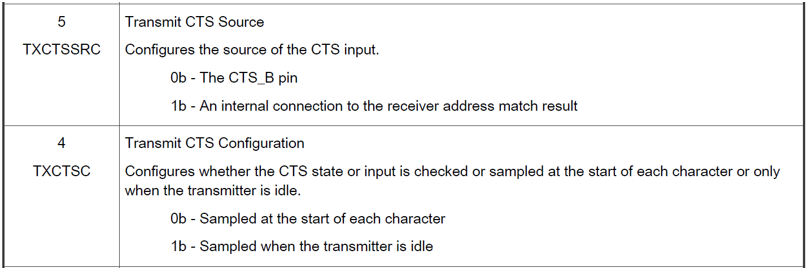

4.4.5 base->MODIR 透過 TXCTSSRC 設定 CTS Source,透過 TXCTSC 設定何時做 sampled,但範例不使用 CTS 功能,可參考 MCXN23xRM Page 1890 ( 如圖 29 )

圖 18

圖 18 圖 19

圖 19 圖 20 ( 註 2 )

圖 20 ( 註 2 ) 圖 21 ( 註 2 )

圖 21 ( 註 2 ) 圖 22 ( 註 2 )

圖 22 ( 註 2 ) 圖 23 ( 註 2 )

圖 23 ( 註 2 ) 圖 24 ( 註 2 )

圖 24 ( 註 2 ) 圖 25 ( 註 2 )

圖 25 ( 註 2 ) 圖 26 ( 註 2 )

圖 26 ( 註 2 ) 圖 27 ( 註 2 )

圖 27 ( 註 2 ) 圖 28 ( 註 2 )

圖 28 ( 註 2 ) 圖 29 ( 註 2 )

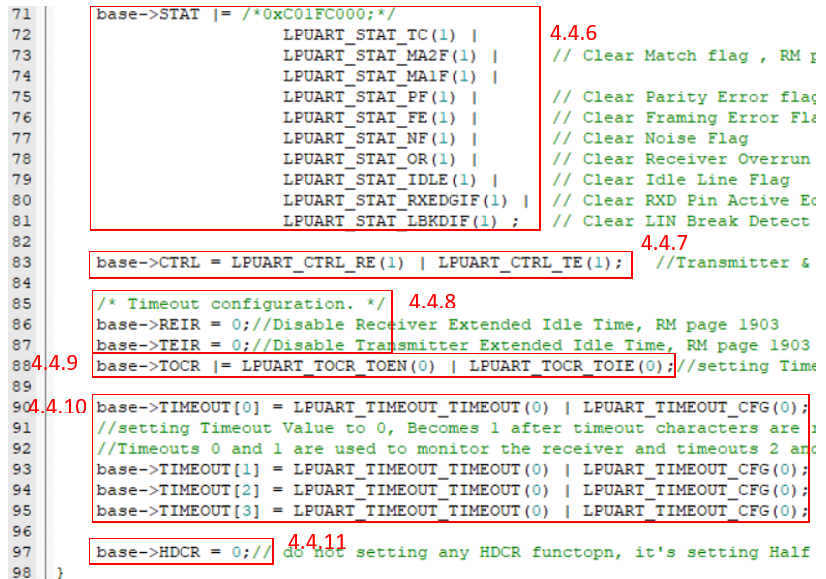

圖 29 ( 註 2 )4.4.6 base->STAT 解析如下 ( 如圖 30 ),可參考 MCXN23xRM Page 1871:

LPUART_STAT_TC:透過 TC register 將 Transmission Complete Flag 歸 0

LPUART_STAT_MA2F:透過 MA2F register 將 Match 2 Flag 歸 0

LPUART_STAT_MA1F:透過 MA1F register 將 Match 1 Flag 歸 0

LPUART_STAT_PF:透過 PF register 將 Parity Error Flag 歸 0

LPUART_STAT_FE:透過 FE register 將 Framing Error Flag 歸 0

LPUART_STAT_NF:透過 NF register 將 Noise Flag 歸 0

LPUART_STAT_OR:透過 OR register 將 Receiver Overrun Flag 歸 0

LPUART_STAT_IDLE:透過 IDLE register 將 Idle Line Flag 歸 0

LPUART_STAT_RXEDGIF:透過 RXEDGIF register 將 RXD Pin Active Edge Interrupt Flag歸 0

LPUART_STAT_LBKDIF:透過 LBKDIF register 將 LIN Break Detect Interrupt Flag 歸 0

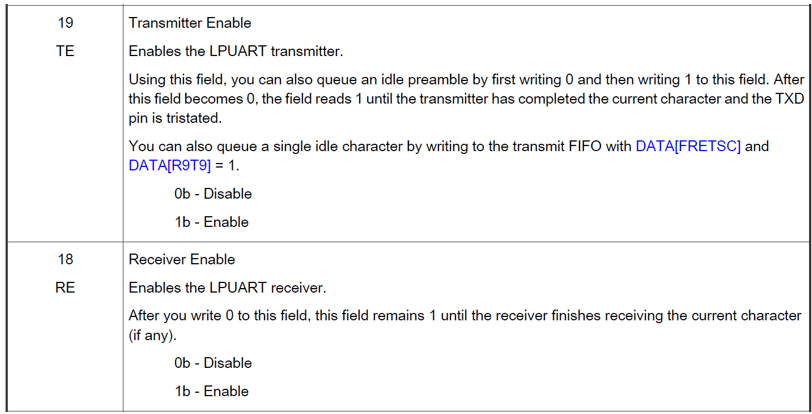

4.4.7 base->CTRL 透過 RE 與 TE register Enable TX、RX 功能,可參考 MCXN23xRM Page 1881 ( 如圖 31 )

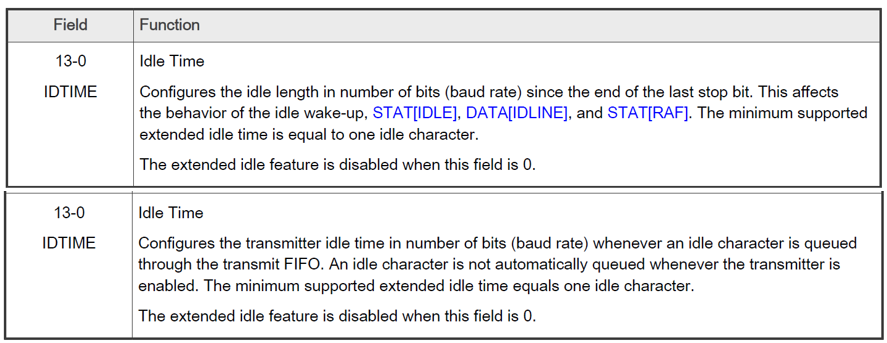

4.4.8 透過 base->REIR 與 base->TEIR 設定是否延長 RX、TX 的 idle 時間,這邊兩者皆設置為 0,可參考 MCXN23xRM Page 1903 ( 如圖 32 )

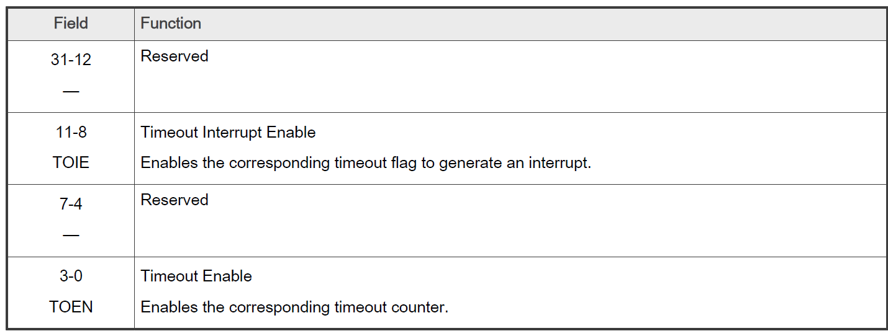

4.4.9 base->TOCR 透過 TOEN register 設定 Timeouts 0~3 功能是否啟用,透過 TOIE register 設定 Timeouts 0~3 是否啟用中斷配置,可參考 MCXN23xRM Page 1906 ( 如圖 33 )

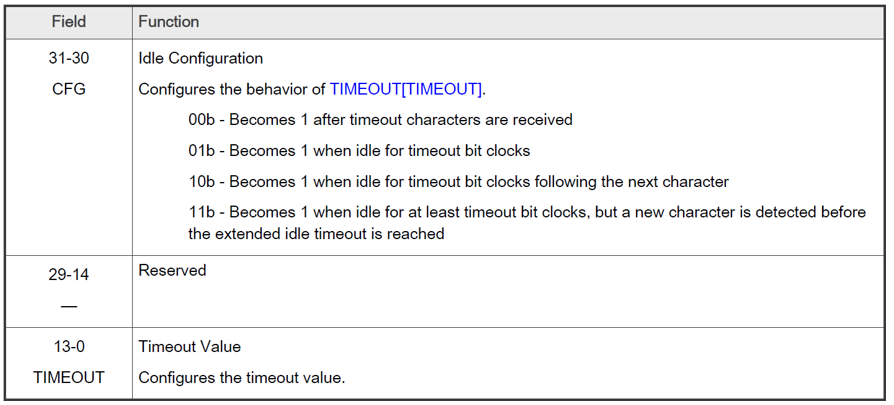

4.4.10 base->TIMEOUT 透過 CFG register 選擇偵測 Timeout 事件的配置,透過 TIMEOUT register 設定 Timeout 的時間配置,可參考 MCXN23xRM Page 1908 ( 如圖 34 )

4.4.11 base->HDCR 用來設定 UART 半雙工的配置,範例沒有使用到因此設定為 0,可參考 MCXN23xRM Page 1904

圖 30

圖 30 圖 31 ( 註 2 )

圖 31 ( 註 2 ) 圖 32 ( 註 2 )

圖 32 ( 註 2 ) 圖 33 ( 註 2 )

圖 33 ( 註 2 ) 圖 34 ( 註 2 )

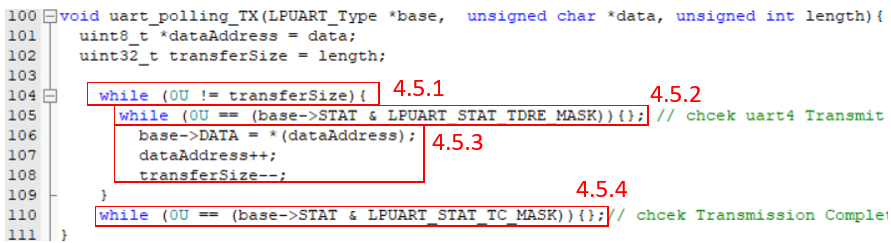

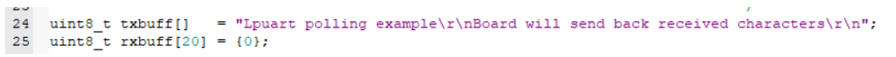

圖 34 ( 註 2 )4.5 uart_polling_TX Function ( 如圖 35 ) 輸入 3 個參數 LPUART4、txbuff、sizeof(txbuff) - 1 ,解析如下:

LPUART4 為 Function 中的 base address

txbuff 為 UART TX 傳送的暫存空間,範例初始值如圖 36,Function 中會另外宣告 dataAddress 指標變數等於 txbuff

sizeof(txbuff) – 1 則為 使用到的 size - 1 的值,用來做 TX counter 使用,Function 中會另外宣告 transferSize 變數等於 sizeof(txbuff) - 1

4.5.1 判斷 transferSize 的值是否為 0,決定後續 function 是否要執行

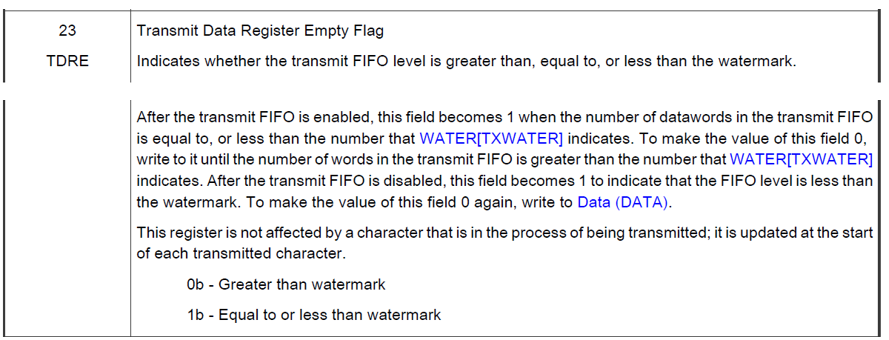

4.5.2 透過 TDRE register 的 Transmit Data Register Empty Flag 功能來判斷 TX FIFO data 數量是否大於 watermark 的值,如果大於則會往下執行

4.5.3 base->DATA 將 txbuff 的指標指向 base->DATA,指向完畢後資料翠自動送出,而後執行 dataAddress++ 增加指標值與 transferSize—表示已傳輸 1 byte 資料出去,並執行到 transferSize 為 0 後跳出迴圈

4.5.4 base->STAT 透過 base->STAT 中的 TC register 確認 TX 資料以傳輸完畢,可參考 MCXN23xRM Page 1874 ( 如圖 38 )

圖 35

圖 35 圖 36

圖 36 圖 37 ( 註 2 )

圖 37 ( 註 2 ) 圖 38 ( 註 2 )

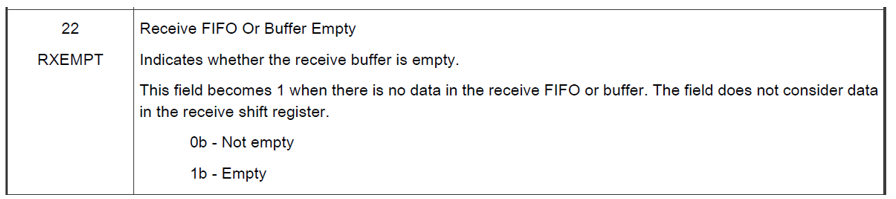

圖 38 ( 註 2 )4.6 LPUART4->FIFO 透過 FIFO register RXEMPT 確認 RX FIFO 中是否為空值,可參考 MCXN23xRM Page 1892 ( 如圖 39 ),如果有值則會執行 uart_polling_RX

圖 39 ( 註 2 )

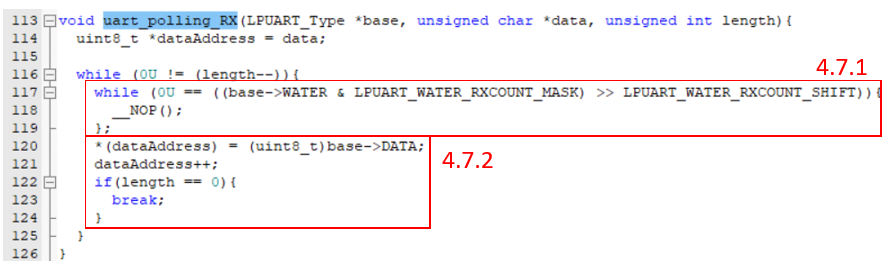

圖 39 ( 註 2 )4.7 uart_polling_RX ( 如圖 40 ) 輸入 3 個參數 LPUART4、rxbuff、10,解析如下:

rxbuff 為 UART RX 接收資料的暫存空間,Function 中會另外宣告 dataAddress 指標變數等於rxbuff

4.7.1 base->WATER 透過 WATER register RXWATER 確認 FIFO 的 data word 是否大於 RXWATER,如大於則往下執行,可參考 MCXN23xRM Page 1896 ( 如圖 41 )

4.7.2 base->DATA 將 register DATA 中的值放到 rxbuff 中,而後 dataAddress++,代表新的 RX 值擺到下個 rxbuff 中,當 length 等於 0,跳出該 function

圖 40

圖 40 圖 41 ( 註 2 )

圖 41 ( 註 2 )4.8 判斷 rxbuff 中的第 1 與第 2 筆值是否等於 0x0A 與 0x05,如果等於則會將 rxbuff 中的值透過 uart_polling_TX Function 傳送出去,實際測試狀況如圖 42

4.8.1 首筆傳輸資料為 txbuff 中的值,txbuff 內容值在圖 36 中可看到

4.8.2 該筆資料為使用者在終端軟體上輸入的值

4.8.3 當收到 rxbuff 中的第 1 與第 2 筆值是否等於 0x0A 與 0x05,rxbuff 中的值透過 uart_polling_TX Function 傳送出去

圖 42

圖 42註 1:作者:NXP Semiconductors;出處:NXP Web site 使用MCUXpresso的FRDM-MCXN236开发板 | NXP 半导体

註 2:作者:NXP Semiconductors;出處:MCXN23Xrm