一、概述

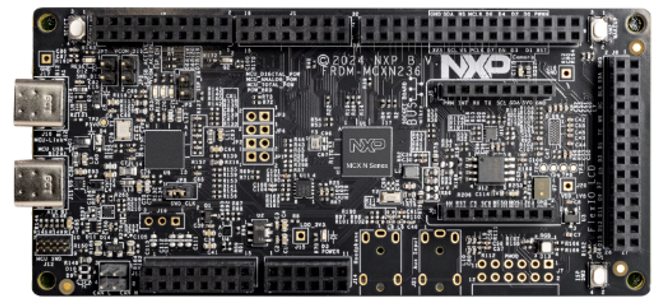

NXP MCXN236 是一款高效能的 32 位元 ARM Cortex-M33 微控制器,它具有高達 150 MHz 的 CPU 運算速度,並擁有 1 MB 的 Flash 和 352 KB 的ECC RAM,內建 Smart DMA 技術,可提升數據傳輸效率,它還具備 8 組 Flexcomms 每組皆可宣告為 SPI、I2C、UART 功能,且支援 High Speed USB、2 組 Flex CAN FD、2 組 I3C、5 組 32 bit Timer、此外,它也擴展了 2 個 16 位元 4 通道高速 ADC,最高取樣率可達 2 Msps,並提供了 HLQFP 與 VFBGA 封装,適合應用電競市場、工業自動化、USB週邊、物聯網和消費性電子等高運算和高速 USB 應用需求的設計。

圖 1 ( 註 1 )

本章節將簡介 MCXN236 的 GPIO 如何進行基本設定,並會搭配 Reference Manual 相關章節解析,GPIO 如何設定 register 使用 Input、Output、interrupt …等功能,而後使用 FRDM-MCXN236 EVK 上的 button 與 LED 來實現 GPIO 的 DEMO

2.1 硬體

2.1.1 NXP FRDM-MCXN236 EVK 詳細規格如下列網址所示

使用MCUXpresso的FRDM-MCXN236开发板 | NXP 半导体

2.1.2 Type C USB Cable : 1 pcs

2.2 軟體

2.2.1 Keil ( IDE ) 軟體開發環境如下列網址所示

https://www.keil.com/product/

2.2.2 NXP FRDM-MCXN236 SDK 如下列網址所示

欢迎 | MCUXpresso SDK构建工具 (nxp.com)

三、 操作方式

3.1 先將 USB cable 與 FRDM-MCXN236 EVK 的 J10 對接上 ( 如圖 2 ),J10 為 EVK on board 燒錄 IC 的 connector,同時也會對 EVK 進行供電

圖 2 ( 註 1 )

圖 2 ( 註 1 )3.2 本章節將編譯 GPIO 的設定 function,會參考到 NXP SDK 中的 MCU 的 startup、CMSIS 的相關文件,因此可以到 NXP 官網下載 FRDM-MCXN236 SDK 檔 ( 如圖 3 )

欢迎 | MCUXpresso SDK构建工具 (nxp.com)

圖 3

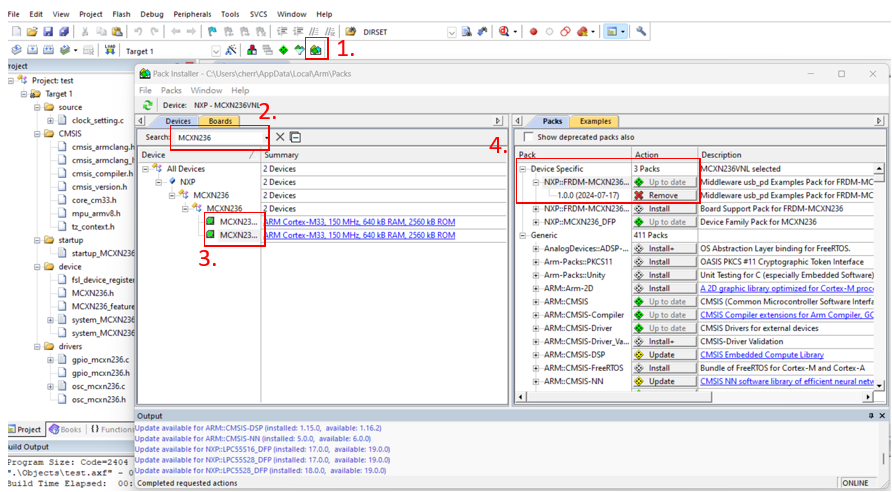

圖 33.3 開啟 Keil,首次使用 MCXN236 MCU 需先到 Keil Pack installer 功能中搜尋 MCXN236,如圖 4 紅框 1. 與 2.,選擇紅框 3. 中的任一款 MCXN236,而後紅框 4. 中會出現相對應的 Pack,進行安裝即可

圖 4

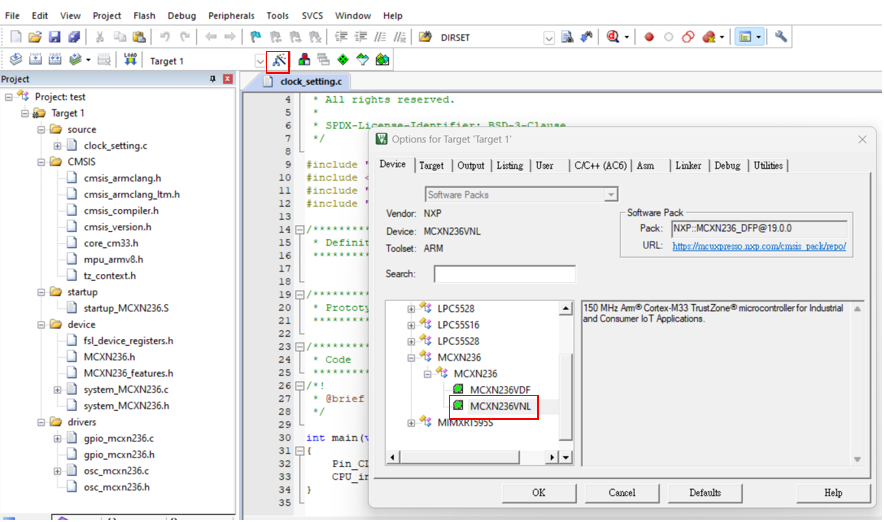

使用 Keil 建立 Project, MCU 選型為 MCXN236 ( 如圖 5 )

圖 5

3.4 下載完畢後針對 SDK 進行解壓縮,後分別查看 SDK 文件路徑如下的檔案

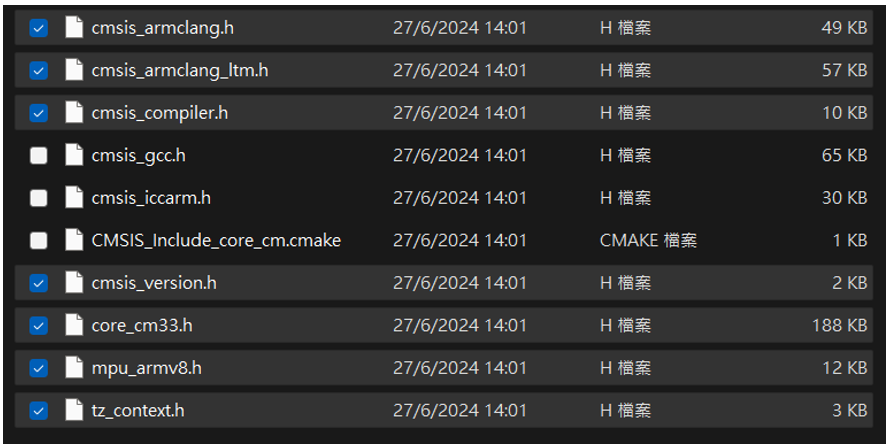

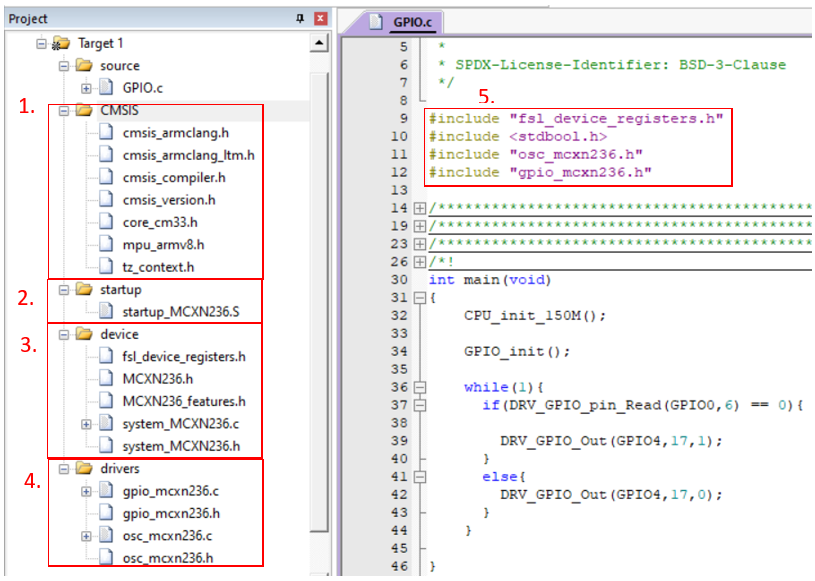

3.4.1 …\SDK_2_14_0_FRDM-MCXN236\CMSIS\Core\Include 將路徑中勾選的文件複製 ( 如圖 6 ),複製到圖 9 紅色方框1 的資料夾

圖 6

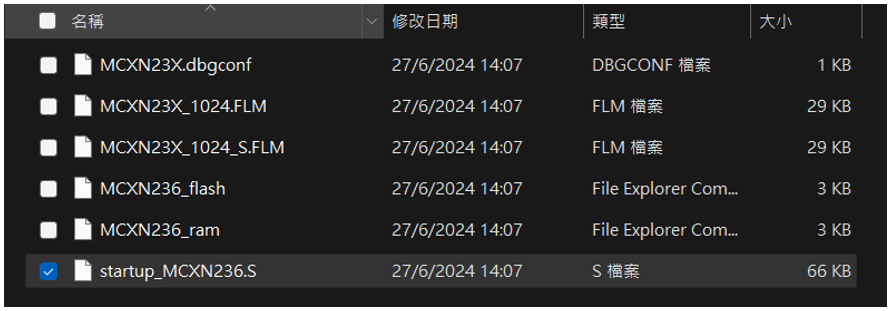

3.4.2 …\SDK_2_14_0_FRDM-MCXN236\devices\MCXN236\arm 將路徑中勾選的文件複製 ( 如圖 7 ),複製到圖 9 紅色方框2 的資料夾

圖 7

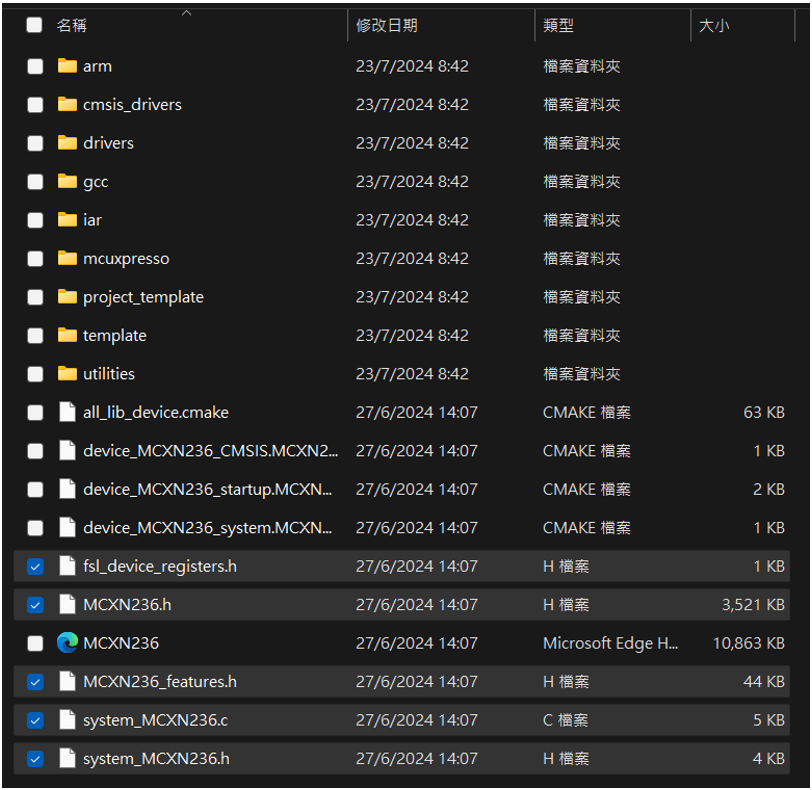

3.4.3 …\SDK_2_14_0_FRDM-MCXN236\devices\MCXN236 將路徑中勾選的文件複製 ( 如圖 8 ),複製到圖 9 紅色方框3 的資料夾

圖 8

3.4.4 將 gpio_mcxn236.c、gpio_mcxn236.h、osc_mcxn236 .c、osc_mcxn236 .h 複製到圖 9 紅色方框4 的資料夾,該 4 份文件後續會說明如何編譯

3.4.5 將有使用到的參考檔 include 到 GPIO.c 中,圖 9 紅色方框 5

圖 9

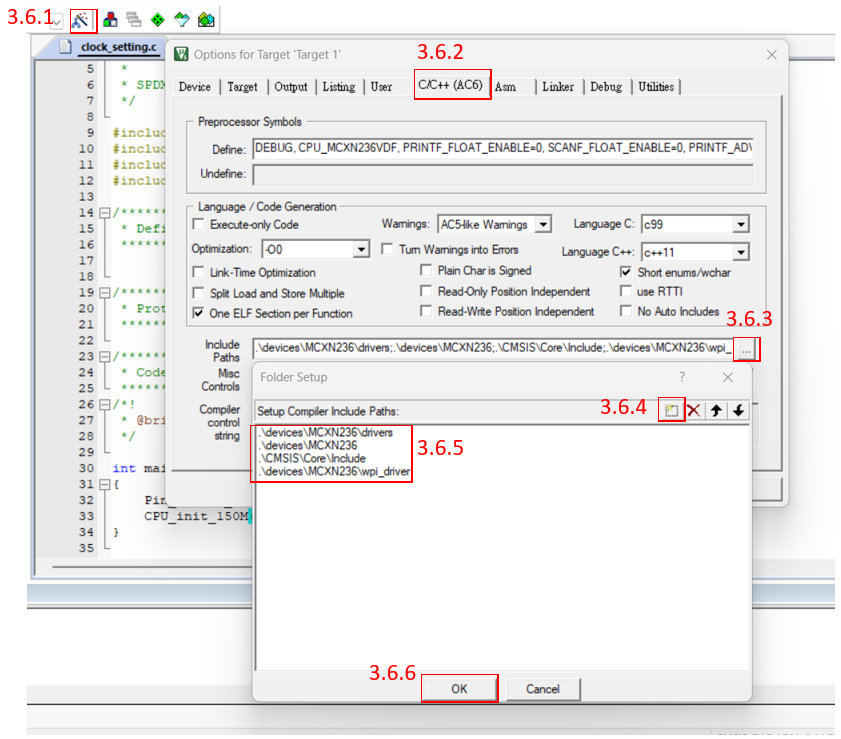

3.6 建置參考文件的路徑 ( 如圖 10 )

圖 10

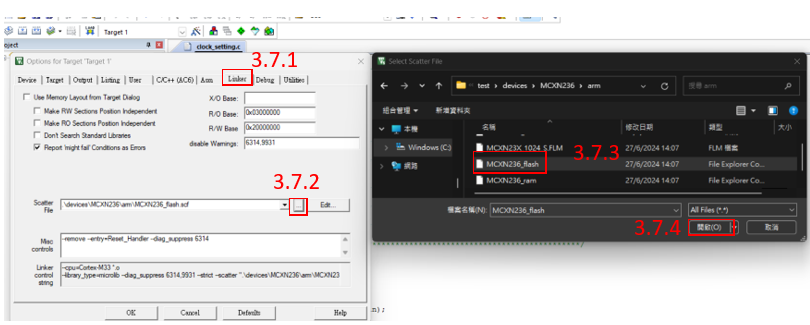

3.7 一樣在 option 的視窗中 ( 如圖11 )

圖 11

圖 12

圖 123.9 點選 Download ( 如圖 13 ) 將編譯完成的 Code 燒錄到 MCXN236 上

圖 13

四、SDK 參數解析

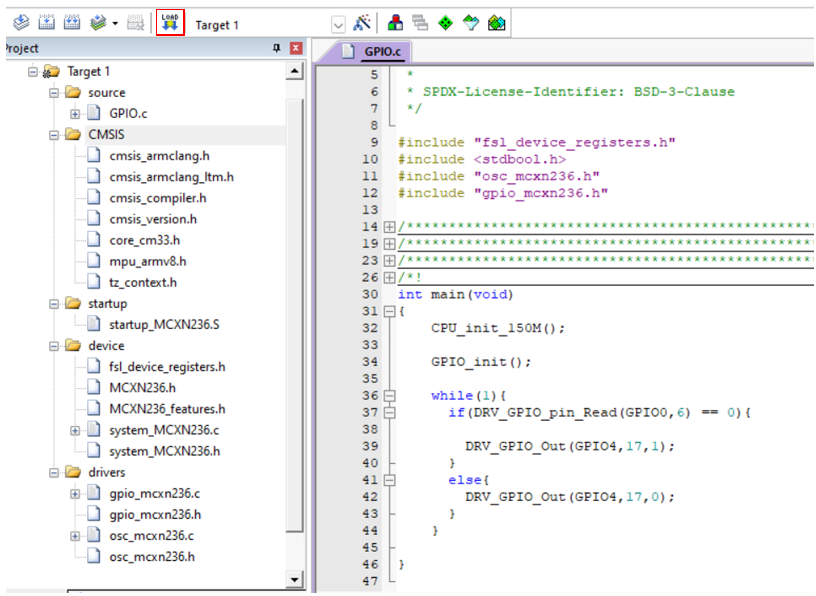

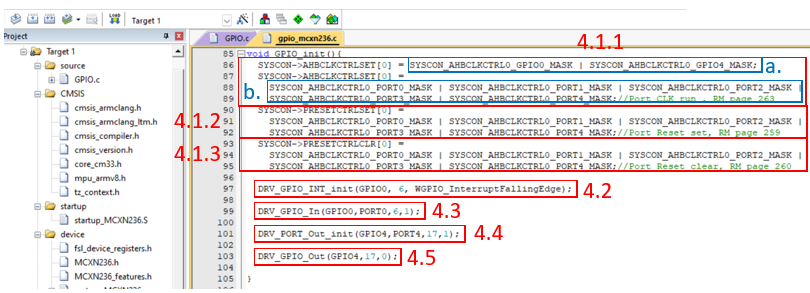

點選 GPIO.c,查看 Main 中的內容 ( 如圖 14 ),其中 CPU_init_150M 部分細節可於 “ MCXN236 系列 System clock 參數定解析與實作 ”中查閱到設定細節

圖 14

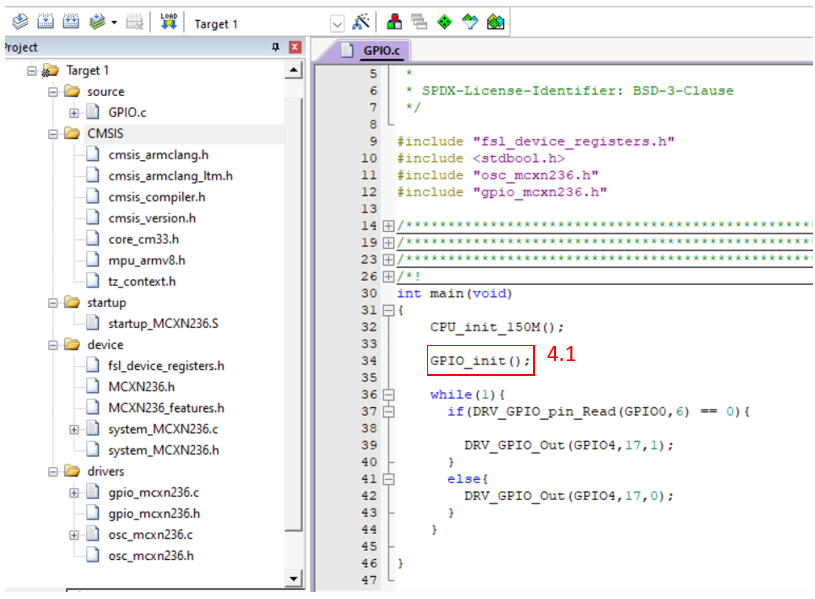

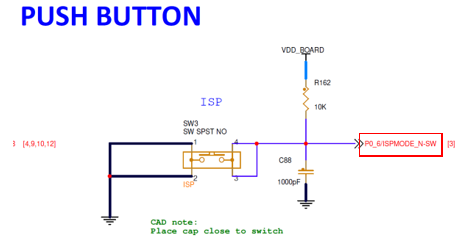

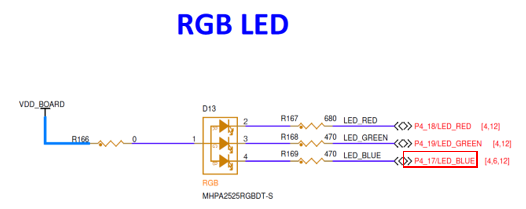

4.1 先查閱 NXP 提供的 FRDM-MCXN236 EVK 線路圖 ( 如圖 15、16 ),EVK 上有配置 button 到 P0_6、有配置 P4_17 到 LED_BLUE,後續將使用該 2 個 GPIO 來作為 Input 與 Output

圖 15 ( 註 2 )

圖 16 ( 註 2 )

查看 GPIO_init 可看到該 Function 編譯在 gpio_mcxn236.c 中 ( 如圖 17 )

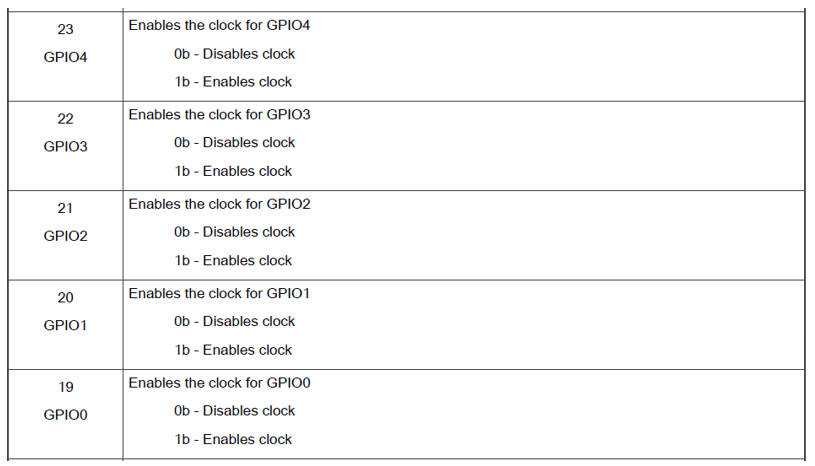

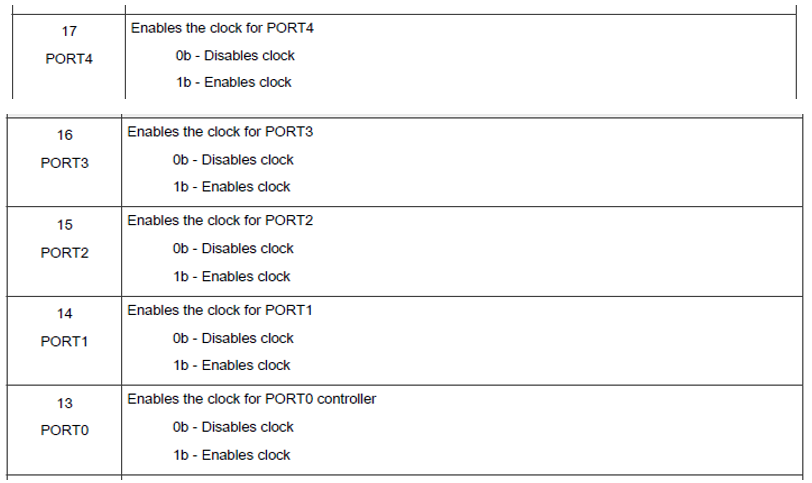

4.1.1 SYSCON->AHBCLKCTRLSET[0] 解析如下:

4.1.2 SYSCON->PRESETCTRLSET[0] 功能為針對要 reset 的周邊設備 bit 位址,填寫 1 的值即可進行 reset,這邊填寫 PORT0 ~ 4,可參考 MCXN23xRM Page 259

4.1.3 SYSCON->PRESETCTRLCLR[0] 針對 4.1.2 已 reset 的周邊設備 bit,填寫 1 的值進行 clear 功能,這邊填寫 PORT0 ~ 4,可參考 MCXN23xRM Page 260

圖 17

圖 18 ( 註 3 )

圖19 ( 註 3 )

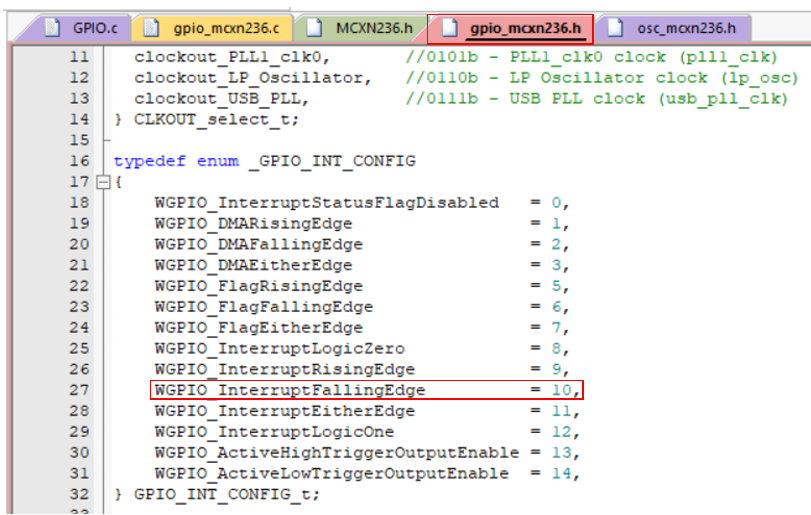

4.2 查看 DRV_GPIO_INT_init Function,這邊下了 3 個參數分別為 GPIO0、6、WGPIO_InterruptFallingEdge ( 如圖 17 ),分別將參數帶入 Function 解析如下:

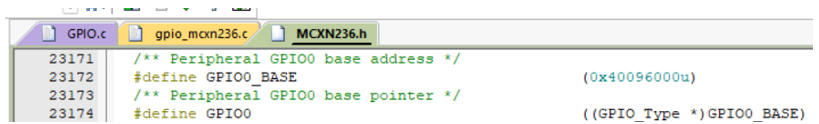

4.2.1 base->ICR[pin],這邊的 base 將會帶入 GPIO0 參數,查詢專案中的 GPIO0 參數可以查閱到參數來自於 MCXN236.h ( 如圖 21 ),配合 MCXN23xRM Page 232 ( 如圖 22 ),可以理解後續的參數會下到 GPIO 中

ICR[2] 代表會對 GPIO Port0 Pin 2 下參數,這邊會對 ICR 的 IRQC 下 config 參數,config 參數為 WGPIO_InterruptFallingEdge

查閱 WGPIO_InterruptFallingEdge 參數可於 gpio_mcxn236.h 找到該參數為 10 ( 如圖 23 )

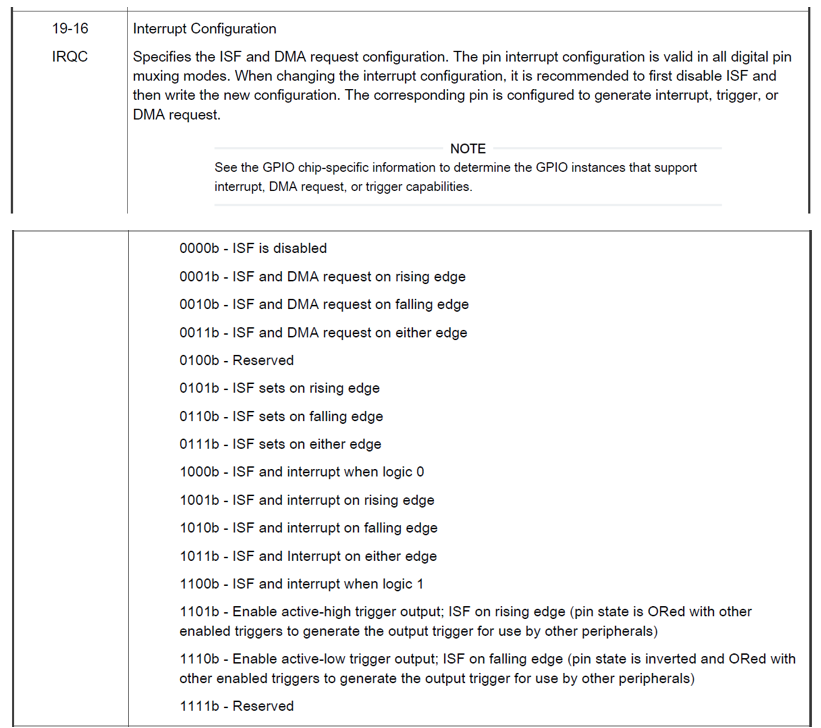

配合 MCXN23xRM Page 2344 了解這邊會對 GPIO Interrupt 的觸發機制設定為 Falling Edge ( 如圖 24 )

4.2.2 NVIC_EnableIRQ,這邊會透過 core_cm33.h 中的 Function 啟用 GPIO_IRQ 功能

圖20

圖20

圖21

圖22 ( 註 3 )

圖22 ( 註 3 )

圖23

圖 24 ( 註 3 )

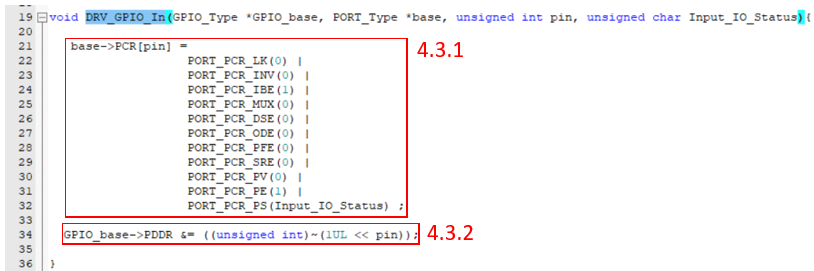

GPIO0、PORT0 章節 4.2 已解析過,後續就不再解析

參數 6 會帶入 PCR[6],代表會對 PORT0 Pin6 進行設定

參數 1 的部分則會帶入 PORT_PCR_PS 中,後續解析

4.3.1 base->PCR[pin] 會針對 PORT Pin 的 register 下參數,解析如下, register 功能參數設定可於 MCXN23xRM Page 2414 中參考:

4.3.2 GPIO_base->PDDR : 設定 GPIO 的 Direction,這邊設定為 0,表示 input ( 如圖 27 ),可參考 MCXN23xRM Page 2340

圖 25

圖 26 ( 註 3 )

圖 26 ( 註 3 ) 圖 27 ( 註 3 )

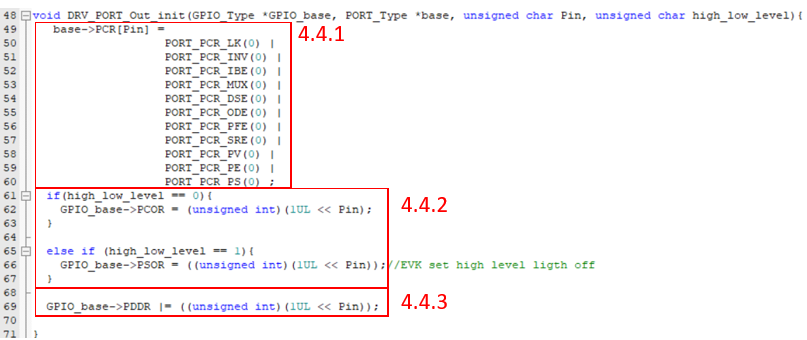

圖 27 ( 註 3 )4.4 DRV_PORT_Out_init 輸入的參數分別為 GPIO4、PORT4、17、1,解析如下 ( 如圖 28 ):

參數 17 會帶入 PCR[17],代表會對 PORT4 Pin17 進行設定

參數 1 的部分則會帶入 high_low_level 中,後續解析

4.4.1 base->PCR[pin] 解析的部分與 4.3.1 相同,這邊就不重複解析

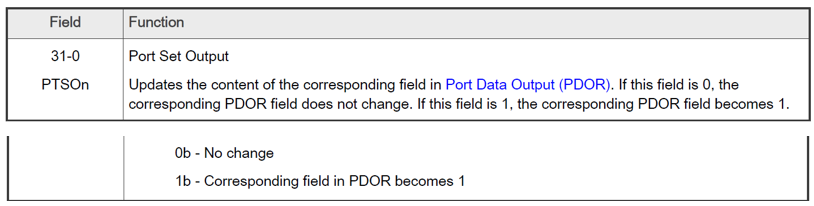

4.4.2 使用 high_low_level 來決定 GPIO register 是透過 PCOR 驅使 Output 為 Low ( 如圖 29 ) 或 PSOR 驅使 Output 為 High ( 如圖 30 ),可參考 MCXN23xRM Page 2336 ~ 2337

4.4.3 GPIO_base->PDDR : 設定 GPIO 的 Direction,這邊設定為 1,表示 output ( 如圖 27 ),可參考 MCXN23xRM Page 2340

圖 28

圖 29 ( 註 3 )

圖 29 ( 註 3 )

圖 30 ( 註 3 )

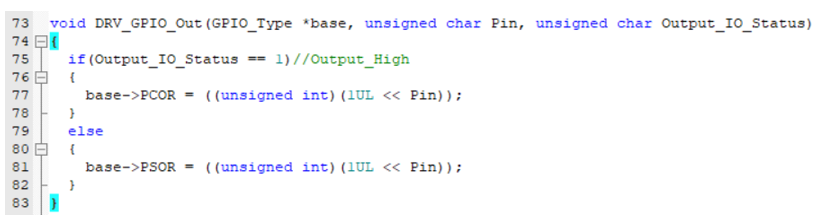

4.5 DRV_GPIO_Out 輸入的參數分別為 GPIO4、17、0 ( 如圖 17 ),解析如下:

參數 17 ( Pin ) 會依據 high_low_level 的配置來決定該參數將帶入 PCOR 或 PSOR,進而決定 output 的輸出電壓準位,配置解析方式如 4.4.2

圖 31

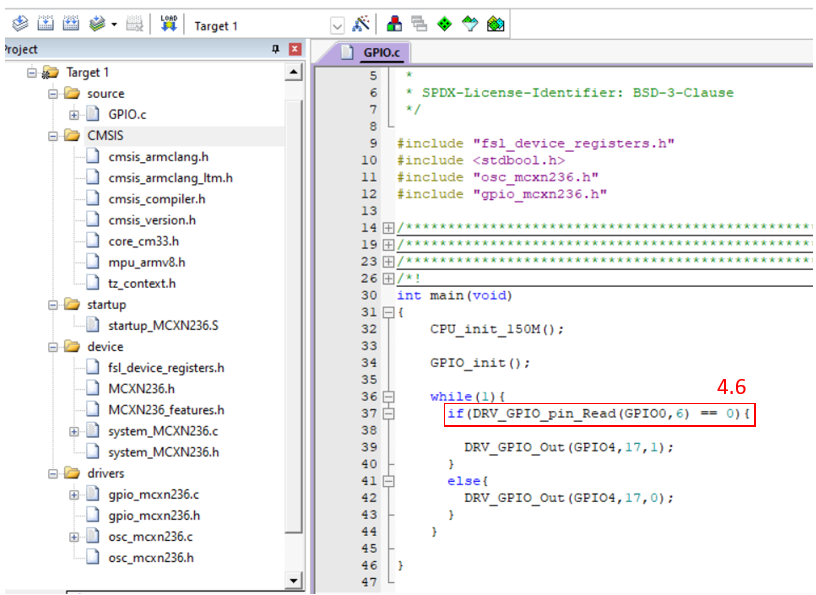

4.6 DRV_GPIO_pin_Read 輸入的參數分別為 GPIO0、6 ( 如圖 32 ),解析如下:

參數 GPIO0 代表該次 DRV_GPIO_pin_Read 將針對 GPIO0 Pin 6

4.6.1 查看 DRV_GPIO_pin_Read Function 如圖 33,Function 將 return (base->PDIR) >> Pin) & 0x01UL) 的值,該值是透過 GPIO PDIR register 功能來查看 GPIO0 Pin 6 的狀態 ( 如圖 34 ),可參考 MCXN23xRM Page 2335

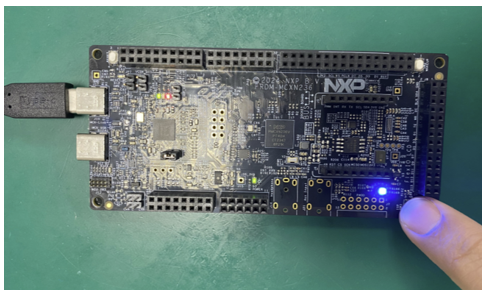

當 EVK 上的 SW3 被按壓後 ( 如圖 15 ),將 return 0,達成條件後 GPIO4 Pin 17 輸出 high 電壓準位,使 LED_BLUE 亮起 ( 如圖 35 )

圖 32

圖 33

圖 33 圖 34 ( 註 3 )

圖 34 ( 註 3 )

圖 35

5.1 gpio_mcxn236.c 與 osc_mcxn236.c 於第 4 章節有提到的部分這邊就不再重複

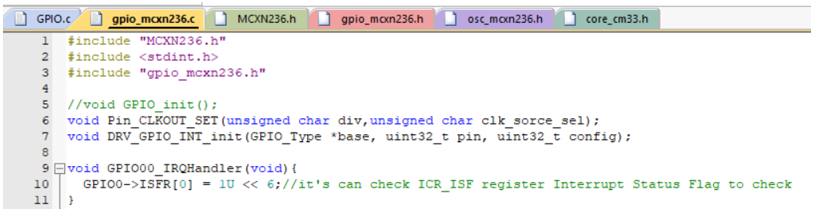

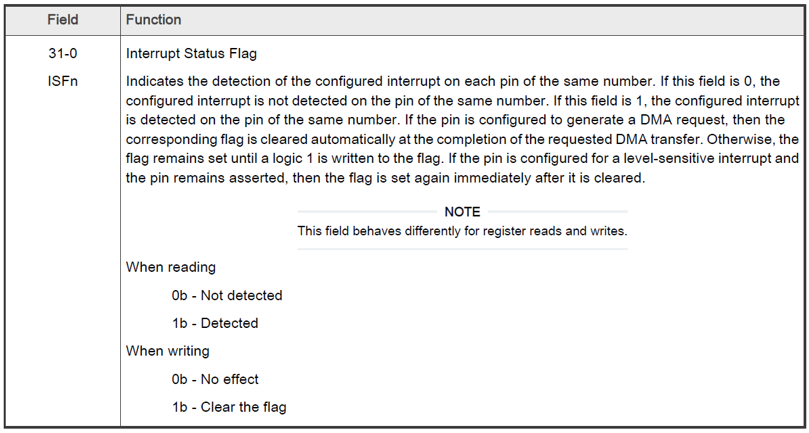

5.2 需注意的是檔案中有參考到的檔案需要 include ( 如圖 36 ),當 GPIO0 Pin 6 有觸發 Falling Edge 時會進入 GPIO00_IRQHandler,透過 GPIO0->ISFR[0] 來清除 Flag ( 如圖 37 ),可參考 MCXN23xRM Page 2347

圖 36

圖 37 ( 註 3 )

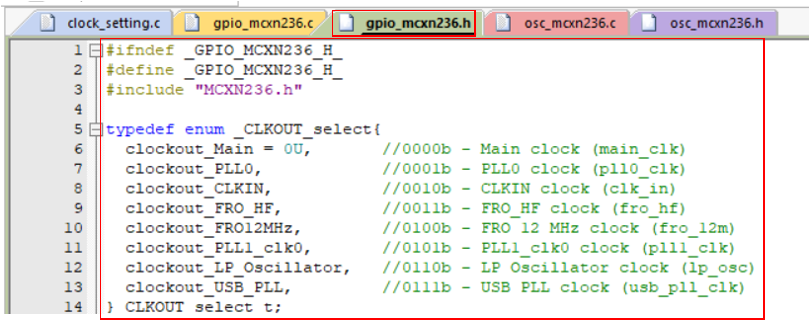

5.3 gpio_mcxn236.h 需建置以下結構與參考文件 ( 如圖38 )

圖 38

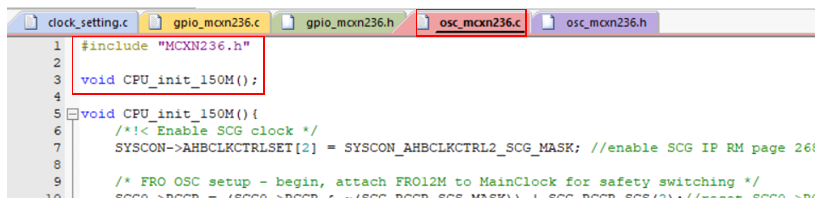

5.4 與步驟 5.2 相同,檔案中有參考到的檔案需要 include ( 如圖 39 )

圖 39

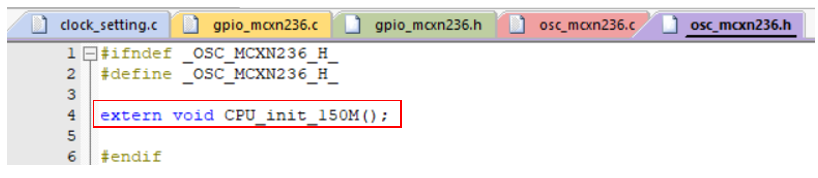

5.5 osc_mcxn236.h 需建置以下配置 ( 如圖 40 )

圖 40

註 1:作者:NXP Semiconductors;出處:NXP Web site 使用MCUXpresso的FRDM-MCXN236开发板 | NXP 半导体

註 2:作者:NXP Semiconductors;出處:SPF-90828

註 3:作者:NXP Semiconductors;出處:MCXN23xRM