功率級內部的MOSFET必須能承受高電流,並對整個系統的效率產生顯著影響。導通損耗和開關損耗共同構成了電晶體上的功率耗散。需要考慮的主要參數包括導通電阻RDS(ON)、柵極電荷以及寄生元件等,它們能在導通損耗和開關損耗之間取得平衡。

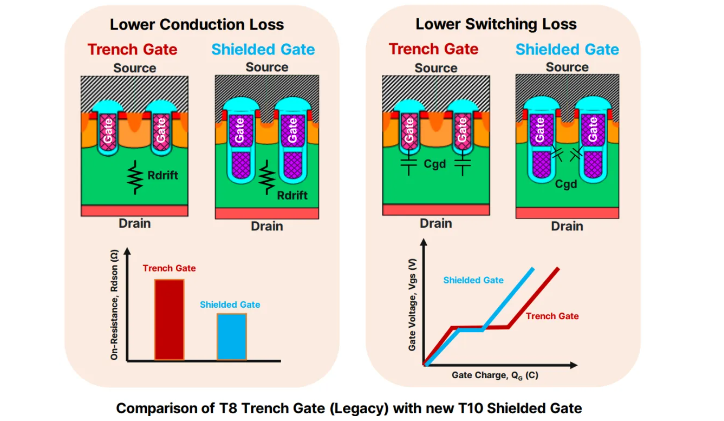

安森美用於低壓和中壓 MOSFET 的新型 T10 技術是理想的選擇,該技術採用屏蔽柵極溝道設計,具有超低 QG 和 RDS(ON) < 1m 的特性。T10技術通過其行業領先的軟恢復體二極體(Qrr, Trr)減少了振鈴、過沖和噪聲,實現了性能與恢復特性之間的完美平衡。

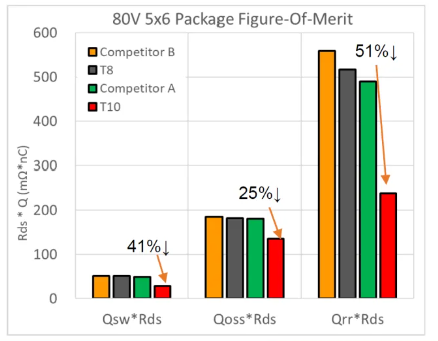

FOM改進

T10屏蔽柵極溝槽技術主要針對DC-DC轉換應用,適用於各種需要 40V 和 80V MOSFET 的新型 48V 應用和傳統 12V 應用。該技術旨在優化效率,降低輸出電容及關鍵性能指標,同時實現更低的導通電阻RDS(ON)和柵極電荷QG。其中,出色的40V溝槽技術產品NVMFWS0D4N04XM,RDS(ON)可低至0.42mΩ,採用小巧的5x6封裝。而對於80V的選項NVBLS0D8N08X,RDS(ON)則可低至0.79mΩ。對於低壓 FET,襯底電阻可能占 RDS(ON) 的很大一部分。

因此,隨著技術的進步,使用較低電阻率的襯底和減薄晶圓變得至關重要。在 T10 技術中,安森美成功減小了晶圓厚度,從而將 40V MOSFET 中襯底對 RDS(ON) 的影響從約 50% 減少到 22%。更薄的襯底也提高了器件的熱性能。

評論