前言:

對於目前電子產品而言,無不追求高效能及輕薄短小。而高效能與輕薄短小,這兩者卻是相違背的。為了因應目前消費產品的潮流趨勢,各零件廠商對於這類的整合式電源產品,都紛紛投入研發資源,以期望能開發更小的封裝尺寸,更大的乘載電流。

先前我們在前一篇博文中,有針對VCC穩壓電容、VIN 濾波電容及LS GATE的相關處理方式有做過討論,而這篇我們將延續對於POL的應用穩定性,來看看還有哪些需要注意的地方。

- POL FB 回授路徑的處理:

以COT架構的POL產品架構來看,其FB回授的電壓會與內部產生的基礎電壓做對比。因沒有早期定頻IC的二階補償器,所以FB回授的穩定度攸關POL穩定性。

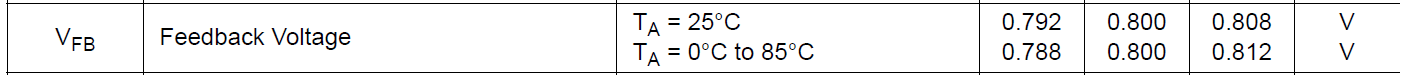

以AOS AOZ2261AQI-10來看,FB回授的電壓會與內部產生的基礎電壓(0.8V)做對比,FB低於基礎電壓(0.8V)時,內部CONTROLLER 會加快DUTY去彌補偏低的輸出電壓。直到FB回授電壓回到與基礎電壓(0.8V)相同時,回到RTON設定頻率。

當FB回授電壓超出(0.808V)或低於(0.792V)時,此時POL就會進入保護模式,所以FB回授的路徑處理就相當的重要。

一般來說,我們會建議避開電感周邊及維持同層路徑。因電感周邊SWITCHING NOISE較高,當FB回授路徑通過此處時,容易讓FB受到干擾,造成FB回授電壓的波動,進而影響FB回授準位,誤觸POL保護機制。另外,我們也會建議FB路徑減少穿層,因為過多的穿層動作,也都會對訊號產生影響。

- FB 回授的位置:

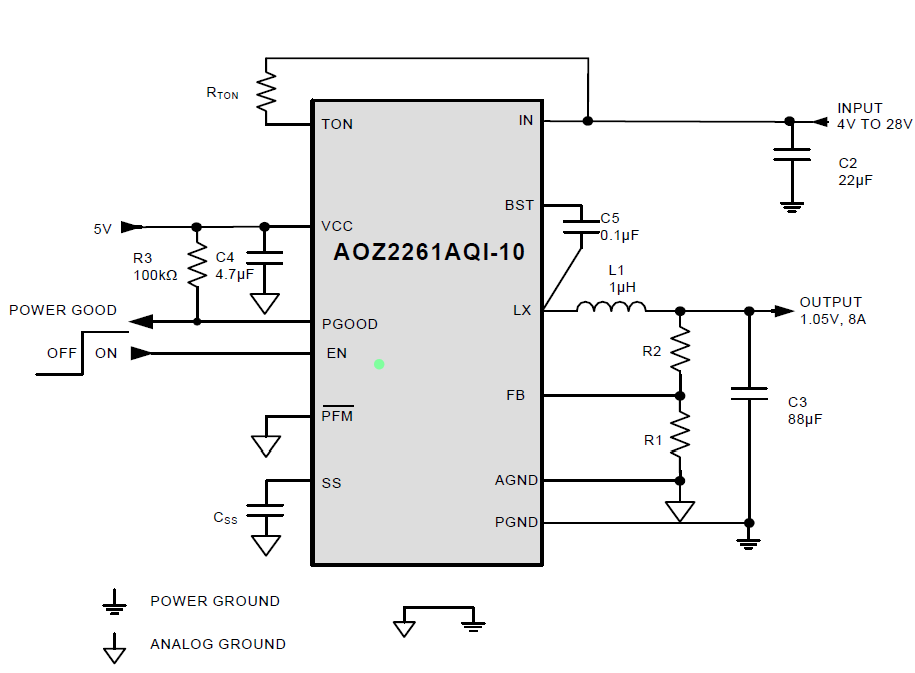

就以下建議線路來看,FB回授從電感與輸出電容間就拉回IC端,一般我們會建議設計者在做LAYOUT規劃時,FB回授點從輸出電容後再拉回IC。此舉有助於FB電壓準位經過輸出電容的穩壓後,相對比較穩定。對於POL的穩定性有一定的幫助。

- 頻率的設定:

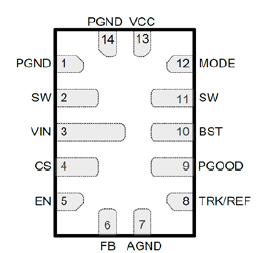

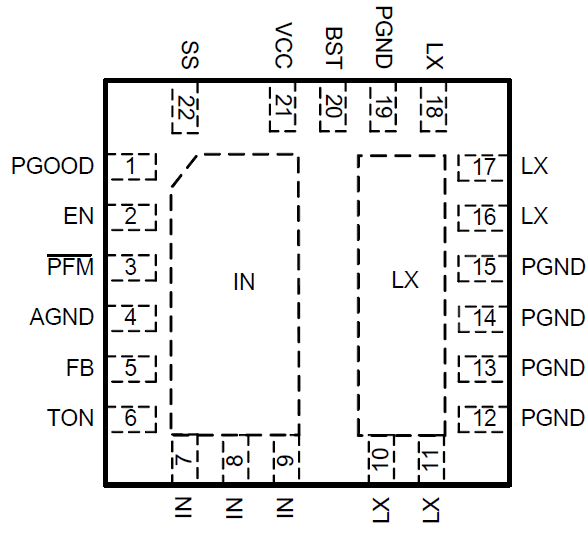

以下圖POL IC接腳來看,目前主流分為單晶片封裝及多晶片封裝方式。

以單晶片封裝來看,其優點為可使用於較高的操作頻率,以滿足應用需求及輸出電容的尺寸。但單晶片封裝的產品,因為IC底部的散熱PAD較多晶片封裝的產品來的小,此時,操作頻率設定的高低,就會影響到IC本體的溫度。

反之,多晶片封裝的產品,雖然本身散熱的PAD較單晶片封裝的產品來的多,但因內部CONTROLLER 與H/L SIDE MOSFET仍須有打線做連接,多少還是會影響到傳輸的頻率。以AOZ2260AQI為例,如非特殊要求,一般我們會將頻率設定在300 – 650KHZ。

問與答:

- Q1:以AOS POL產品來看,頻率是否有建議值?

Ans:如非特殊需求,建議使用300 – 650 KHZ。

- Q2:以AOS POL產品來看,FB 受到干擾時,會有甚麼異常?

Ans: 當FB受到干擾時,最明顯的就是輸出電壓產生波動,及PHASE JITTER的現象。

- Q3以AOS POL產品來看,輸出電壓設定上與頻率有何關聯性?

Ans:以AOS COT 架構的POL來看,首先須注意其Max on time 的限制,如初始設定頻率會與MAX ON TIME 衝突時,可嘗試將頻率加快,避開MAX ON TIME的限制。

- Q4:以AOS POL產品來看,是否有過溫保護?

Ans:以AOZ2260AQI為例,IC 內部是有THERMAL SHUTDOWN 的功能,但並不建議把它當成主要的保護機制。因為一般IC工作溫度約在80℃以下,而THERMAL SHUTDOWN的點在於150℃,並不建議讓IC工作在這樣高的溫度下。

- Q5:以AOS POL產品來看,COT架構的優點為何?

Ans: COT架構的POL因少了內部二階補償機制,FB 直接與內部VREF作比較。能較快速的反應輸出端電流的變化,一般來說COT架構的POL在transient時輸出電壓會較定頻類POL會相對的穩定一些。