STR(Suspend to RAM) 功能是實現系統在休眠狀態下快速喚醒的一個功能,要實現該功能需要軟體和硬體協同工作,軟體方面請參考芯馳官方軟體的 STR 功能介紹文件上實現檔, 硬 STR 功能需要保證兩個模塊的供電不能斷電,即 RTC 的 1.8v/0.8v 和 DRAM 的 1.8v/1.1v, 以保證 RTC 模塊正常工

作及 DRAM 保持 IO Retention 模式。

二、 STR電路設計要求

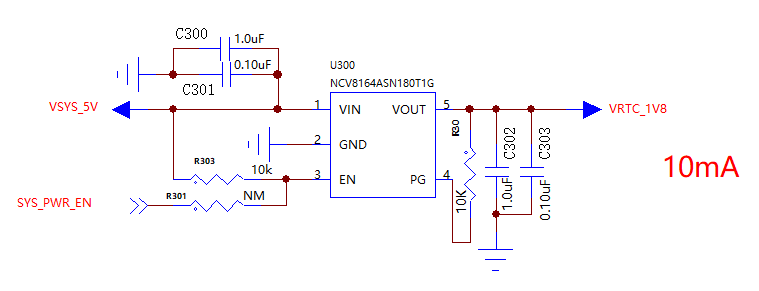

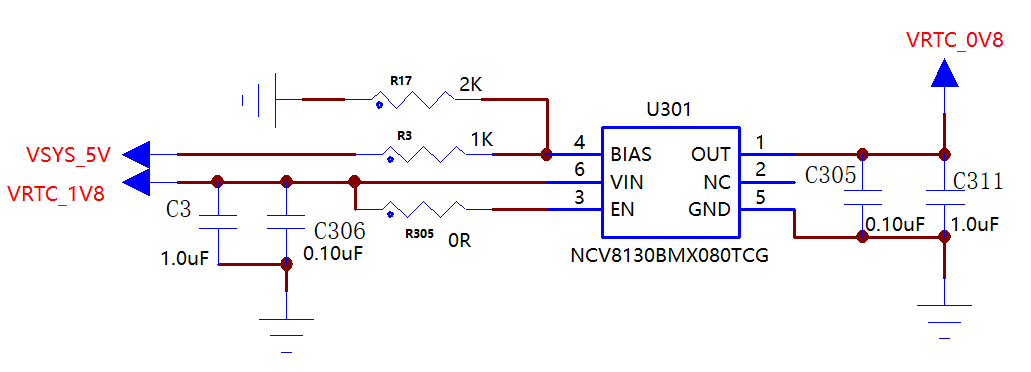

① 進入 STR 模式時,需要 RTC 的 1.8V 和 0.8V 不能斷電, 即 RTC_1V8 和 RTC_0V8 保持供電,並配置好喚醒源;

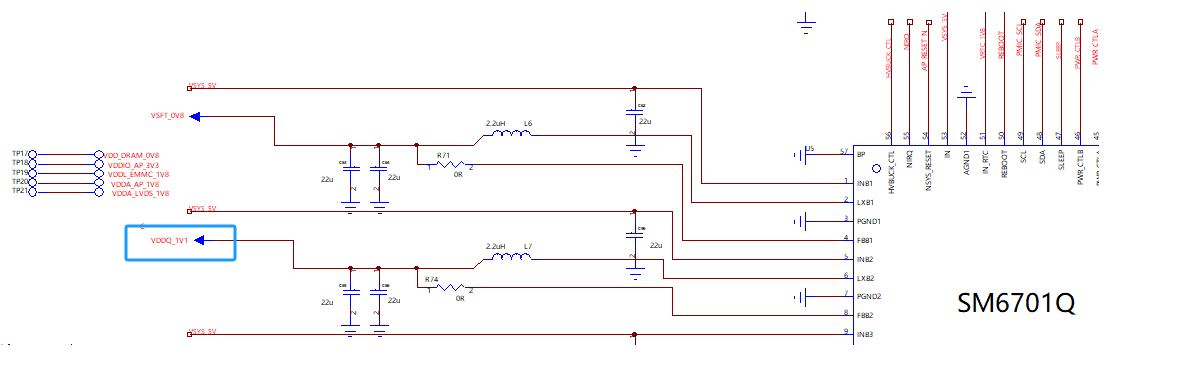

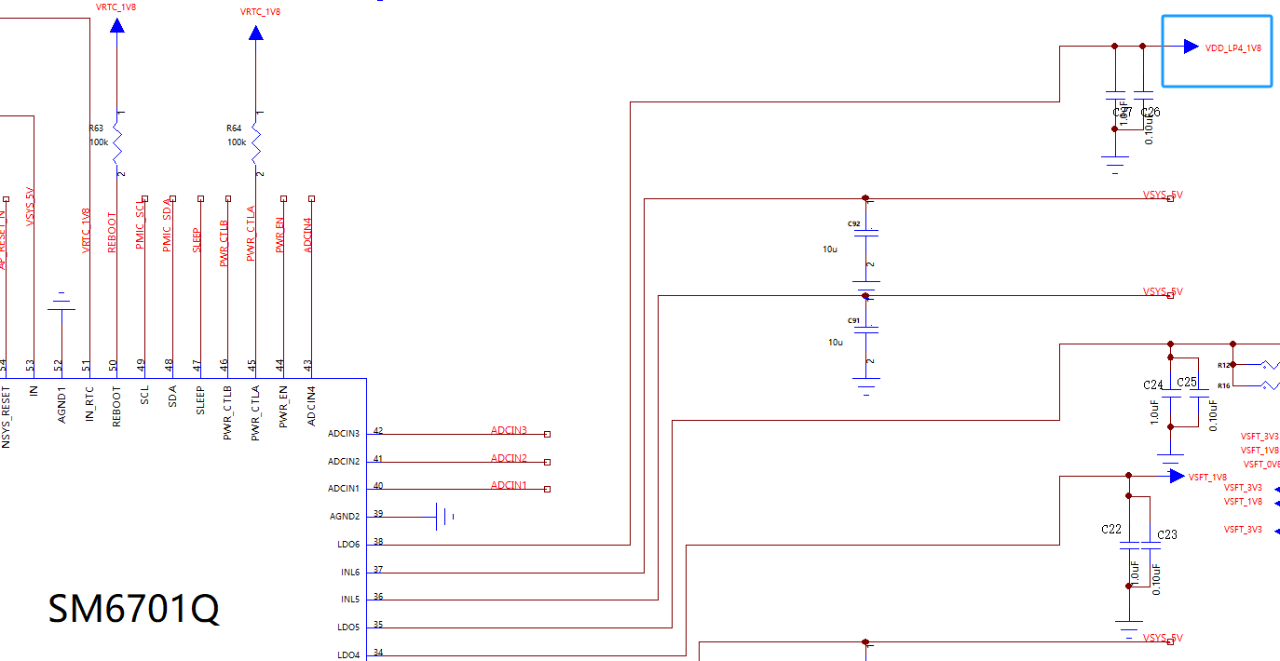

② 進入STR 模式時,需要 DRAM 的 1.1V 和 1.8V 不能下電,即 VDDQ_1V1 和 VDD_LP4_1V8 保持供電,使用 LPDDR4x 時,0.6V 可以斷電;

③ 進入 STR 模式時,系統的電流較小,供電電路如果使用 Buck 電路,需要設置 Buck 的工作模式為小電流下效率較高的模式;

④ 系統上如果有 CAN 電路,並支持 CAN 喚醒,那麼在進入 STR 模式前,需要先把 CAN 收發器配置進入 sleep 模式,要不會被 CAN 收發器一直喚醒,系統就不能進入 STR 模式。

三、Dragonfly-SM 核心板STR功能硬體電路介紹

1、RTC 域 1.8V 和 0.8V 電路採用分離 LDO 單獨供電,上電使能;當 MPU 進入 STR 模式時,RTC 1.8V 和 RTC 0.8V 仍然保持輸出給 RTC 域供電。

2、DRAM 的 1.1V 和 1.8V 保持供電電,即 VDDQ_1V1 和 VDD_LP4_1V8 保持供電;

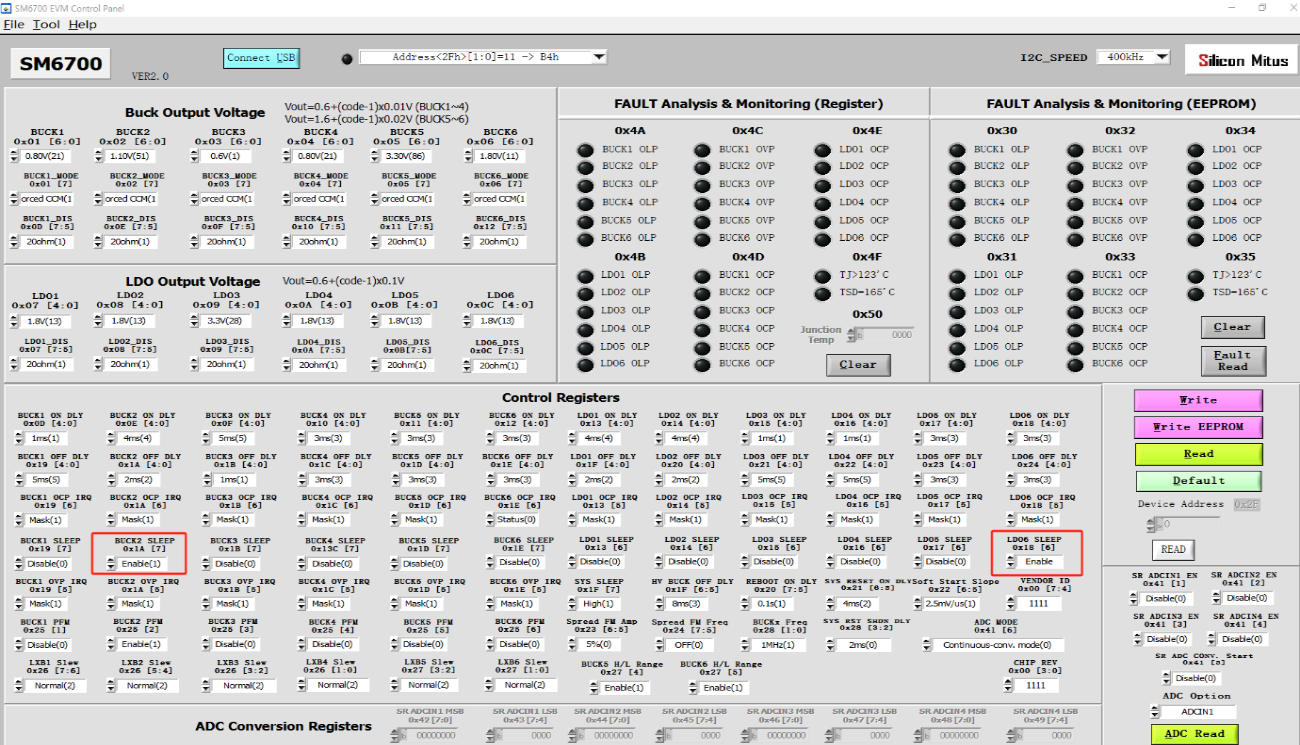

由原理圖中可以看出,VDDQ_1V1 和 VDD_LP4_1V8 是採用芯邁 PIMC 晶片 SM6701Q 的 BUCK2 和 LDO6 分別供電,為了是系統進入 STR 模式時這兩路電源仍能正常輸出,因此通過 I2C 配置程序配置, 使 VDDQ_1V1 和 VDD_LP4_1V8 的輸出與 PWR_EN 解綁, 不響應 PMIC 輸出使能控制, 能夠正常輸出電壓。

四、總結

在進入 STR 後,不能使用 BUCK 的 PWM 模式,效率較低,在小電流時切換到 PFM 模式,效率較高;

五、參考文獻

SD003_X9H_REF_硬體設計指導.pdf

X9H 處理器數據手冊_Rev04.00.pdf

DS_SM6700Q.pdf

Silicon Magic Auto PMIC.pdf

SM6700Q EVM Test Report.pdf

SemiDrive_9 系列_STR 功能_硬體設計手冊_Rev01.01.pdf

歡迎在博文下方留言評論,我們會及時回復您的問題。如有更多需求,歡迎聯繫大聯大世平集團 ATU 部門:atu.sh@wpi-group.com

作者:Ji Zhu / 朱吉

評論