1. S32K344 FlexIO 介紹

1.1 簡介

S32K344 包含一個 FlexIO 模塊,FlexIO 是一種高度可配置的模塊,可提供廣泛的功能,包括:

- 模擬各種串行或並行通信協議,比如 UART、I2C、SPI、SAI,它既可以作為主機,也可以作為從機;

- 靈活的 16 位定時器,支持各種觸發、復位、啟用和禁用條件;

- 可編程邏輯塊,它允許在片上實現數字邏輯功能和可配置的內部與外模模塊交互;

- 可編程狀態機,用於從 CPU 卸載基本系統控制功能。

表1.1.1 數據速率限制

|

FlexIO 操作 |

數據速率限制 |

|

Master Tx |

FlexIO_clk/4 |

|

Slave Tx |

FlexIO_clk/10 |

|

Master Rx |

FlexIO_clk/8 |

|

Slave Rx |

FlexIO_clk/6 |

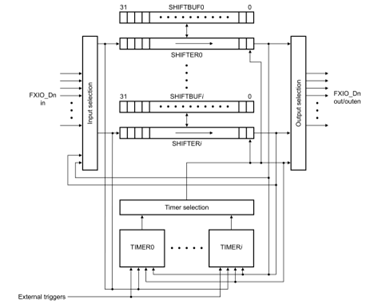

FlexIO 使用移位器、計時器和外部觸發器將數據移入或移出 FlexIO。如下圖所示,計時器控制數據移位的時間。可以將計時器配置為使用通用計時器功能、外部觸發器或其他各種條件來確定控制項。

圖1.1-1 FlexIO 框圖

FlexIO 包括一下特點:

- 具有發送、接收、數據匹配、邏輯和狀態模式的 32 位移位寄存器數組;

- 雙緩衝移位操作連續數據傳輸;

- 移位器串聯以支持大規模傳輸;

- 自動生成啟動與停止位;

- 支持 1、2、4、8、16 或 32 多位移位寬度並行接口;

- 中斷、DMA、輪詢發送和接收操作;

- 可編程波特率獨立於總線時鐘頻率;

- 高度靈活的 16 位定時器,支持各種內部或外部觸發、復位、使能和禁用條件;

- 可編程邏輯模式集成於外部數據邏輯功能片上,或結合引腳、移位器、定時器功能以產生複雜的輸出;

- 可編程狀態機從 CPU 卸載基本系統控制功能,支持多達八個狀態、八個輸出,何三個可選擇輸入的每個狀態;

- 集成通用輸入/輸出寄存器和引腳上升或下降沿中斷,以簡化軟體支持;

- 支持廣泛的協議,包括但不限於:UART、I2C、SPI、I2S、Camera IF、Motorola 68K 或 or Intel 8080 bus、PWM 或 waveform 生成、輸入捕獲(脈衝邊緣間隔測量)例如 SENT。

2. 功能描述

2.1 移位器操作

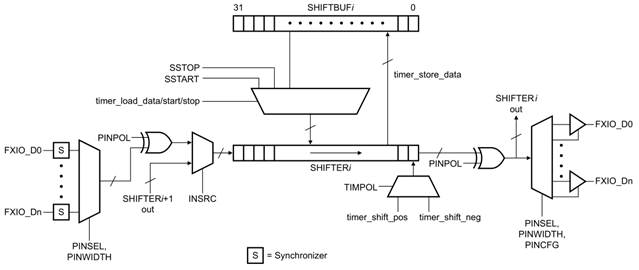

移位器負責緩衝和將數據移入或移出 FlexIO。移位、加載和存儲事件的時間通過 SHIFTCTL[TIMSEL] 寄存器分配給移位器的定時器控制。移位器被設計成支持 DMA、中斷或輪詢操作。下圖為移位器微架構的詳細視圖。

圖2.1-1 移位器微體系架構圖

移位器有發送、接收、匹配存儲、連續匹配、狀態、邏輯等模式,具體模式信息與寄存器讀寫操作本文不在此贅述詳細了解請閱讀 S32K344 用戶參考手冊。

2.2 定時器操作

FlexIO 16 位定時器控制移位寄存器的加載、移位和存儲。計數器加載比較寄存器的內容,並在 FlexIO 時鐘上遞減到零。計數器可以執行一般定時器功能,如產生時鐘或選擇輸出或 PWM 波形。定時器可以被配置為:

- 使能響應觸發器、引腳或移位器條件;

- 始終或僅在觸發器或者引腳邊沿遞減;

- 響應觸發器或引腳條件復位;

- 在觸發器、引腳條件或定時器比較上禁用。

定時器可以選擇性地包括開始條件和停止條件。

雖然每個定時器都可以獨立運行,但可以將一個定時器配置為與前一個定時器同時啟用或禁用(例如:定時器 1 可以與定時器 0 同時啟用或禁用),並且定時器輸出可用於觸發任何定時器。每個定時器使用的觸發器是獨立配置的,可以配置為定時器輸出、移位器狀態標識、引腳輸入或外部觸發輸入。觸發器配置與引腳配置分開,引腳配置可以配置為輸入、輸出數據或輸出使能。定時器配置寄存器(TIMCFGn)必須在設置定時器模式(TIMOD)之前進行配置。

定時器有 8 位波特計數器模式、8 位高 PWM 模式、16 位計數器模式、禁用 16 位計數器模式、8 位字計數器模式、8 位低 PWM 模式、計數器使能和開始位、定時器衰減和復位、定時器禁用和停止位等模式,具體模式信息與寄存器讀寫操作本文不在此贅述詳細了解請閱讀 S32K344 用戶參考手冊。

2.3 引腳操作

每個定時器和移位器的引腳配置可以配置為使用任何一個極性的任何 FlexIO 引腳。每個定時器和移位器可以配置為輸入、輸出數據、輸出使能或雙向輸出。配置為輸出啟用的引腳可以用作漏極(極性倒置,因為輸出啟用置位導致引腳上輸出邏輯零)或控制雙向輸出上的啟用。任何定時器或移位器都可以配置為控制引腳的輸出使能,其中雙向輸出數據有另一個定時器或移位器驅動。

引腳操作有並行接口、引腳同步、引腳覆蓋、引腳中斷等模式,,具體模式信息與寄存器讀寫操作本文不在此贅述詳細了解請閱讀 S32K344 用戶參考手冊。

2.4 低功耗模式

如果使能了 FlexIO 功能時鐘,則在低功耗模式下,FlexIO 仍能正常工作。

2.5 調試模式

如果設置了使能調試欄位(CTRL[DBGE]),則 FlexIO 在調試模式下保持功能。

2.6 時鐘

功能時鐘

FlexIO 功能時鐘與總線時鐘是異步的,可以在低功耗模式下使能。在訪問任何 FlexIO 寄存器之前,必須啟動 FlexIO 功能時鐘。如果 FlexIO 功能時鐘至少等於總線時鐘,則可以設置 CTRL[FASTACC] 欄位以支持快速寄存器訪問。

總線時鐘

總線時鐘僅用於總線訪問控制寄存器和配置寄存器。

2.7 復位

晶片復位

在晶片復位時,FlexIO 的邏輯和寄存器被重置為其默認狀態。

軟體復位

FlexIO 在其控制寄存器中實現了一個軟體復位欄位。CTRL[SWRST] 將除了 CTRL 外的所有邏輯和寄存器重置為默認狀態。

2.8 中斷與 DMA 請求

表2.8.1 FlexIO 中斷與 DMA 請求

|

標誌 |

描述 |

中斷 |

DMA 請求 |

低功耗喚醒 |

|

SSF |

移位器狀態標誌 |

Y |

Y |

Y |

|

SEF |

移位器錯誤標誌 |

Y |

N |

Y |

|

TSF |

計時器狀態標誌 |

Y |

Y |

Y |

|

PSF |

引腳狀態標誌 |

Y |

N |

Y |

|

ETSF |

外部觸髮狀態標誌 |

Y |

N |

Y |

2.9 外圍觸發器

FlexIO 外圍觸發器與其他外設之間的連接是特定於設備的。

輸出觸發器

每個 FlexIO 定時器產生一個等於定時器輸出的輸出觸發器。輸出觸發器不受定時器引腳極性配置的影響。

輸入觸發器

FlexIO 支持多個外部觸發輸入,可用於觸發一個或多個 FlexIO 定時器。當使能 FlexIO 時,如果在外部觸發器上檢測到上升沿,則設置外部觸髮狀態標誌。外部觸發器與 FlexIO 功能時鐘同步,並且必須置位至少兩個周期的 FlexIO 功能時鐘才能正確採樣。

3. FlexIO 模擬應用

3.1 UART

3.1.1 發送

可以使用一個定時器、一個移位器和一個引腳(如果支持 CTS,則為兩個引腳)來支持 UART 傳輸。開始和停止位插入是自動處理的,並且使用 DMA 控制器支持多次傳輸。定時器狀態標誌用於指示何時傳輸每個字的停止位。

中斷和空閒字符需要軟體干預。在發送中斷或空閒字符之前,必須更改 SSTART 和 SSTOP 欄位以傳輸所需的狀態,並且要傳輸的數據必須等於 FFh 或 00h。支持第二個停止位需要使用軟體將停止位插入數據流(並增加要傳輸的位數)。當對 SHIFTBUFn 執行字節寫入時(或者先傳輸 MSB 的 SHIFTBUBIS),寄存器的其餘部分保持不變。這允許地址標記位或額外的停止位保持不受干擾。

3.1.2 接收

可以使用一個定時器、一個移位器和一個引腳(如果支持 RTS,則使用兩個定時器和兩個引腳)來支持 UART 接收。開始和停止位驗證時自動處理的,並且使用 DMA 控制器支持多次傳輸。定時器狀態標誌用於指示何時接收到每個單詞的停止位。

FlexIO 不支持對接收到的數據進行三重投票;數據只在每個比特的中間採樣一次。可以使用定時器來實現傳入數據上的故障濾波器,並使用不同的定時器來檢測可編程長度的空閒路線。中斷字符導致錯誤標誌被設置,移位器緩衝區寄存器將返回 00h。

3.2 SPI

3.2.1 控制器

可以使用兩個定時器、兩個移位器和四個引腳支持 SPI 控制器模式。支持 CPHA=0 或 CPHA=1,並且可以使用 DMA 控制器支持傳輸。對於 CPHA=1,可以對多個傳輸保持置位選擇,並且可以使用定時器狀態標識來指示傳輸的結果。

停止位用於保證在目標選擇否定和下一次傳輸之前至少有一個時鐘周期。要啟動每次傳輸,需要通過核心或 DMA 向傳輸緩衝區寫入數據。

3.2.2 目標

SPI 目標模式可以使用一個定時器、兩個移位器和四個引腳。支持 CPHA=0 或 CPHA=1,並且可以使用 DMA 控制器進行傳輸。對於 CPHA=1,可以對多個傳輸保持置位選擇,並且可以使用定時器狀態標誌來指示傳輸的結束。

在外部目標選擇置位之前,必須將傳輸數據寫入傳輸緩衝區寄存器,否則將設置移位錯誤標誌。

3.3 I2C

3.3.1 控制器

可以使用兩個定時器、兩個移位器和兩個引腳來實現 I2C 控制器模式。一個定時器用於 SCL 輸出,一個定時器用於控制移位器;兩個移位器用於發送和接收字符,接收時發送機必須發送 FFh 到 3 狀態輸出。FlexIO 在每個字後插入一個停止位,以生成和驗證 ACK 或 NACK。在啟用 SCL 生成之前,FlexIO 等待第一次寫入傳輸數據緩衝區。數據傳輸可以使用 DMA 控制器和在發送欠運行或接收溢出上設置移位錯誤標誌來支持。

第一個定時器為整個包生成時鐘(從 START 到Repeat START 或 STOP),因此比較寄存器必須用包中的時鐘邊總數(減去 1)進行編程。當引腳等於輸出時,定時器支持使用復位定時器進行時鐘拉伸。但是這將使始終高周期和時鐘低周期各增加至少 1 個 FlexIO 時鐘周期。第二個定時器使用 SCL 輸入引腳來控制發送和接收移位寄存器。這使 SDA 數據保持時間增加了 2 個 FlexIO 時鐘周期。

發送和接收移位器都必須為傳輸中的每個字進行檢修。接收時,發送移位器必須發送 FFh,接收移位器返回 SDA 引腳上的數據。傳輸移位器在 SCL 引腳的最後下降沿上加載一個額外的字。如果生成 STOP 條件或重複 START 條件,則該字必須分別為 00h 或 FFh。在控制器-接收器傳輸的最後一個字期間,必須設置發送 SSTOP 位以生成 NACK。

如果檢測到 NACK,接收移位寄存器置位一個錯誤中斷,但是負責生成 STOP 或重複 START 條件。如果在控制器發送過程中檢測到 NACK,中斷必須立即將 00h(如果產生 STOP)或 FFh (如果產生重複 START)寫入發送移位寄存器。在禁用兩個定時器之前,必須等待 SCL 上的下一個上升邊沿。在等待設置延遲重複啟動或停止條件後,要禁用傳輸移位器。

為了保證 SDA 保持時間,I2C 控制器數據有效延遲兩個周期,因為時鐘輸出在發送或接收移位器之前通過同步器。由於 SCL 輸出與 FlexIO 時鐘同步,因此同步延遲為一個周期,然後一個周期生成輸出。

3.4 I2S

3.4.1 控制器

可以使用兩個定時器,兩個移位器和四個引腳支持實現 I2S 控制器模式。一個定時器用於生成位時鐘和控制移位器,一個定時器用於生成幀同步。在啟用位時鐘和幀同步生成之前,FlexIO 等待第一次寫入傳輸數據緩衝區。數據傳輸支持使用 DMA 控制器和移位器錯誤標誌設置在發送欠運行或接收溢出。

位時鐘頻率是 FlexIO 時鐘頻率的偶數除法。初始幀同步置位與第一個位時鐘邊緣同時發生。計時器使用起始位確保在第一個輸出數據之前一個時鐘周期生成幀同步。

3.4.2 目標

可以使用三個定時器,兩個移位器和四個引腳。對於單發送和單接收,可以使用其他的發送和接收組合。

傳輸數據必須在外部幀同步置位之前寫入傳輸緩衝區寄存器,否則將設置移位錯誤標誌。

I2S 目標的輸出有效時間最大為 2.5 個周期,因為時鐘同步的最大延遲為 1.5 個周期,再加上 1 個周期輸出數據。

定時器 2 檢測幀同步的下降沿(新幀的開始)並置位輸出直到位時鐘的上升沿(當幀同步正常採樣時)。定時器 0 檢測位時鐘的上升沿,定時器 2 輸出置位,並置位幀長度輸出。定時器 1 檢測位時鐘下降沿定時器 0 輸出置位和控制移位寄存器位 32 位傳輸。

3.5 發送接收器

使用一個定時器和一個引腳可以支持發送接收器。定時器配置為輸入捕獲模式,捕獲引腳輸入下降沿的計數器值。捕獲計數器值後,將自動從計數器值 0 重新啟動計數器。因此,捕獲值總是表示前一個下降沿和當前下降沿之間的周期。CPU 中斷或 DMA 觸發器可以在每次捕獲計數器時配置。整個發送幀解碼與最新的刻度寬度調整是由 CPU 軟體執行。

3.6 低功耗狀態機

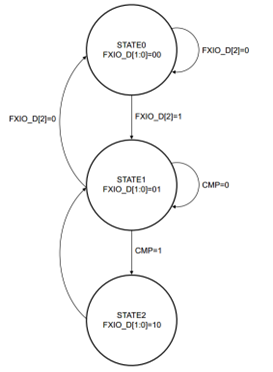

下表顯示了假設狀態機的示例,以說明移位器狀態模式中允許的靈活性。

在這個示例里,FlexIO 等待 FXIO_D[2] 引腳置位,然後在比較器輸出置位時在 FXIO_D[1:0] 引腳上以 FLEXIO_CLK/131072 的頻率驅動互補方波輸出,假設改比較器連接到外部觸發器 15。有關實際 FlexIO 觸發器映射,請參閱晶片特定的 FlexIO 信息。下圖顯示了此示例現實的狀態和轉換。

圖3.6-1 狀態圖

3.7 鍵盤接口

鍵盤接口可以使用三個定時器和三個移位器支持 3×4 鍵盤矩陣,不過可以使用附加移位器支持更大的矩陣。該配置設計為四列配置為低電平有效開漏引腳,三行配置為啟用上拉電阻的輸入引腳。

一個移位器被配置為邏輯模式,以在任何行為輸入為低電平(表明按下了某個鍵)時置位其輸出。使用計時器來過濾移位器輸出,以確保在執行列掃描之前按下按鍵的時間最短。

配置不同的移位器用於並行傳輸。當檢測到按鍵時,使用此移位器掃描每一列。不掃描時,移位器輸出配置為置位所有低電平有效開漏列輸出以檢測任何按鍵。使用專用定時器來控制發送移位器。

最後一個移位器配置為並行接收。使用此移位器捕獲列掃描的結果,以便軟體解碼按下的鍵(或多個鍵)。儘管行狀態也可以通過移位順序推斷,但此配置捕獲每次掃描的行和列引腳的狀態。使用專用定時器來控制接收移位器,其移位評率為發送移位器頻率的一半。

當接收移位寄存器中存在按鍵掃描的結果時,FlexIO 繼續監視行輸入,並可以通過一次按鍵觸發多次掃描。為了支持去抖動,可以將多少次連續臊面視為單詞按鍵。

4. 外部信號

表4-1 外部信號

|

信號 |

描述 |

方向 |

|

FXIO_Dn(n=0…31) |

雙向 FlexIO 移位器和定時器引腳 |

輸入或輸出 |

5. FlexIO 寄存器描述

FlexIO 基礎地址:4032_4000h

|

偏移 |

寄存器 |

寬度 (以位為單位) |

存取 |

復位值 |

|

0h |

Version ID Register (VERID) |

32 |

RO |

0201_0003h |

|

4h |

Parameter Register (PARAM) |

32 |

RO |

0420_0808h |

|

8h |

FlexIO Control Register (CTRL) |

32 |

RW |

0000_0000h |

|

Ch |

Pin State Register (PIN) |

32 |

RO |

0000_0000h |

|

10h |

Shifter Status Register (SHIFTSTAT) |

32 |

W1C |

0000_0000h |

|

14h |

Shifter Error Register (SHIFTERR) |

32 |

W1C |

0000_0000h |

|

18h |

Timer Status Register (TIMSTAT) |

32 |

W1C |

0000_0000h |

|

20h |

Shifter Status Interrupt Enable (SHIFTSIEN) |

32 |

RW |

0000_0000h |

|

24h |

Shifter Error Interrupt Enables (SHIFTEIEN) |

32 |

RW |

0000_0000h |

|

28h |

Timer Interrupt Enable Register (TIMIEN) |

32 |

RW |

0000_0000h |

|

30h |

Shifter Status DMA Enable (SHIFTSDEN) |

23 |

RW |

0000_0000h |

|

38h |

Timer Status DMA Enable (TIMERSDEN) |

32 |

RW |

0000_0000h |

|

40h |

Shifter State Register (SHIFTSTATE) |

32 |

RW |

0000_0000h |

|

48h |

Trigger Status Register (TRGSTAT) |

32 |

W1C |

0000_0000h |

|

4Ch |

External Trigger Interrupt Enable Register (TRIGIEN) |

32 |

RW |

0000_0000h |

|

50h |

Pin Status Register (PINSTAT) |

32 |

W1C |

0000_0000h |

|

54h |

Pin Interrupt Enable Register (PINREN) |

32 |

RW |

0000_0000h |

|

58h |

Pin Rising Edge Enable Register (PINREN) |

32 |

RW |

0000_0000h |

|

5Ch |

Pin Falling Edge Enable Register (PINFEN) |

32 |

RW |

0000_0000h |

|

60h |

Pin Output Data Register (PINOUTD) |

32 |

RW |

0000_0000h |

|

64h |

Pin Output Enable Register (PINOUTE) |

32 |

RW |

0000_0000h |

|

68h |

Pin Output Disable Register (PINOUTDIS) |

32 |

WORZ |

0000_0000h |

|

6Ch |

Pin Output Clear Register (PINOUTCLR) |

32 |

WORZ |

0000_0000h |

|

70h |

Pin Output Set Register (PINOUTSET) |

32 |

WORZ |

0000_0000h |

|

74h |

Pin Output Toggle Register (PINOUTTOG) |

32 |

WORZ |

0000_0000h |

|

80h-9Ch |

Shifter Control N Register (SHIFTCTL0-SHIFTCTL7) |

32 |

RW |

0000_0000h |

|

100h-11Ch |

Shifter configuration N Register (SHIFTCFG0-SHIFTCFG7) |

32 |

RW |

0000_0000h |

|

200h-21Ch |

Shifter Buffer N Register (SHIFTBUF0-SHIFTBUF7) |

32 |

RW |

0000_0000h |

|

280h-29Ch |

Shifter Buffer N Bit Swapped Register (SHIFTBUFBIS0-SHIFTBUFBYS7) |

32 |

RW |

0000_0000h |

|

300h-31Ch |

Shifter Buffer N Byte Swapped Register (SHIFTBUFBYS0-SHIFTBUFBBS7) |

32 |

RW |

0000_0000h |

|

380h-39Ch |

Shifter Buffer N Bit Byte Swapped Register (SHIFTBUFBBS0-SHIFTBUFBBS7) |

32 |

RW |

0000_0000h |

|

400h-41Ch |

Timer Control N Register (TIMCTL0-TIMCTL7) |

32 |

RW |

0000_0000h |

|

480h-49Ch |

Timer Configuration N Register (TIMCFG0-TIMCFG7) |

32 |

RW |

0000_0000h |

|

500h-51Ch |

Timer Compare N Register (TIMCMP0-TIMCMP7) |

32 |

RW |

0000_0000h |

|

680h-69Ch |

Shifter Buffer N Nibble Byte Swapped Register (SHIFTBUFNBS0-SHIFTBUFNBS7) |

32 |

RW |

0000_0000h |

|

700h-71Ch |

Shifter Buffer N Halfword Swapped Register (SHIFTBUFHWS0-SHIFTBUFHWS7) |

32 |

RW |

0000_0000h |

|

780h-79Ch |

Shifter Buffer N Nibble Swapped Register (SHIFTBUFNIS0-SHIFTBUFNIS7) |

32 |

RW |

0000_0000h |

|

800h-81Ch |

Shifter Buffer N Odd Even Swapped Register (SHIFTBUFOES0-SHIFTBUFOES7) |

32 |

RW |

0000_0000h |

|

880h-89Ch |

Shifter Buffer N Even Odd Swapped Register (SHIFTBUFEOS0-SHIFTBUFEOS7) |

32 |

RW |

0000_0000h |

|

900h-91Ch |

Shifter Buffer N Halfword Byte Swapped Register (SHIFTBUFHBS0-SHIFTBUFHBS7) |

32 |

RW |

0000_0000h |

由於篇幅所限本文僅介紹 S32K344 FlexIO 模塊部分內容,如想了解更多資料與設計,請聯繫我們 atu.sh@wpi-group.com。

6. 參考文獻

[1] S32K3XX Reference Manual.pdf,NXP

[2] S32K3XX Data Sheet.pdf,NXP

歡迎在博文下方留言評論,我們會及時回復您的問題。如有更多需求,歡迎聯繫大聯大世平集團 ATU 部門:atu.sh@wpi-group.com

作者:Hobo Xu/ 許寧

評論