Layout設計中的幾個關鍵步驟是布局、走線、鋪銅、散熱,英諾賽科高壓單管GaN的Layout設計也不例外。

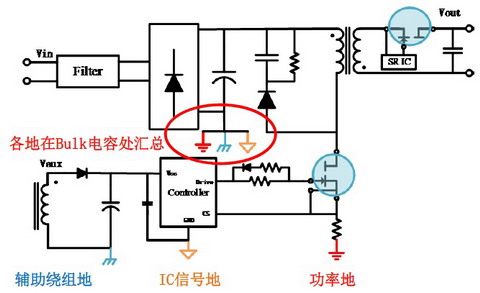

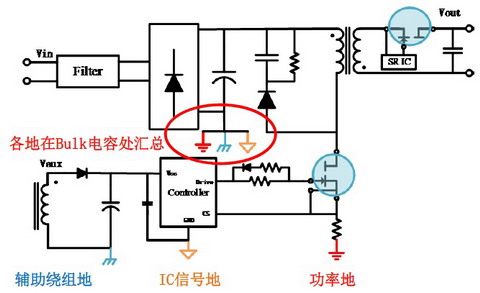

反激拓撲是高壓單管GaN的典型應用,快充場合常用。該拓撲在地線的處理上都需特別注意,如下圖所示,Layout時輔助繞組地、IC信號地功率地在bulk電容處匯合,避免IC地受干擾導致驅動振盪。

在GaN應用時,Layout上還需注意以下方面:

1) 由於電流檢測電阻的存在,此種場合GaN的開爾文腳與源極直接連接,否則電流採樣電阻失去作用。

2) Source端與bulk電容地的走線儘可能短、粗,減小寄生電感LS。

3) 驅動電路和功率電路分開布置,避免干擾

4) 驅動IC及驅動電路儘量靠近GaN一些,減小驅動迴路的走線和面積

5) 高壓場合,GaN的漏源極交疊銅皮的寄生電容儘量小,以優化開關loss。

反激拓撲是高壓單管GaN的典型應用,快充場合常用。該拓撲在地線的處理上都需特別注意,如下圖所示,Layout時輔助繞組地、IC信號地功率地在bulk電容處匯合,避免IC地受干擾導致驅動振盪。

在GaN應用時,Layout上還需注意以下方面:

1) 由於電流檢測電阻的存在,此種場合GaN的開爾文腳與源極直接連接,否則電流採樣電阻失去作用。

2) Source端與bulk電容地的走線儘可能短、粗,減小寄生電感LS。

3) 驅動電路和功率電路分開布置,避免干擾

4) 驅動IC及驅動電路儘量靠近GaN一些,減小驅動迴路的走線和面積

5) 高壓場合,GaN的漏源極交疊銅皮的寄生電容儘量小,以優化開關loss。

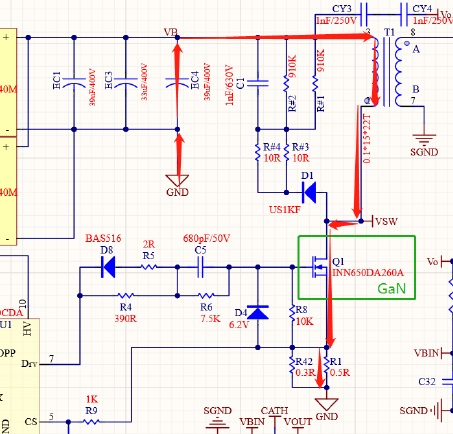

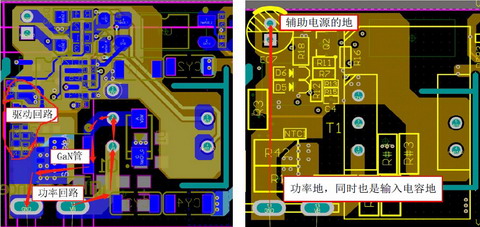

下面為DFN封裝的高壓GaN在65W快充應用中的layout案例:

QR反激拓撲,GaN在高網下無法零電壓開通,GaN的漏極和源極的鋪銅如果形成寄生電容,會額外增大開通loss,該案例的Layout中避免了該問題,由左圖可見。同時,GaN的功率迴路和驅動迴路在布局上較好的分開,避免了功率電路對驅動電路的干擾。

另由圖可見,通過中間層的大鋪銅將輔助電源的地和功率的地線相連,地線的處理乾淨清晰.

評論