本文旨在介紹使用 NXP i.MX RT1170 時,在需要外掛 SDRAM 的情況下,Layout 上的一些細節以及注意事項;

首先先簡單介紹一下 SDRAM,這是一種很常見的高速記憶體,但它的性能和可靠性會直接影響到裝置的運行速度和穩定性。

在進行 SDRAM 的設計時,Layout 是非常重要的一個環節。一個好的 Layout 設計可以保證 SDRAM 的性能和可靠性,而一個不良的 Layout 設計則可能導致 SDRAM 的性能下降、資料傳輸錯誤、EMI 過高等問題。因此,在進行 SDRAM 的 Layout 設計時,為了確保設計的成功,有一些重要的注意事項。

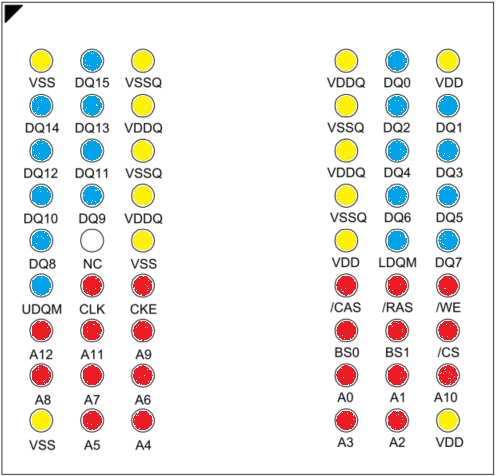

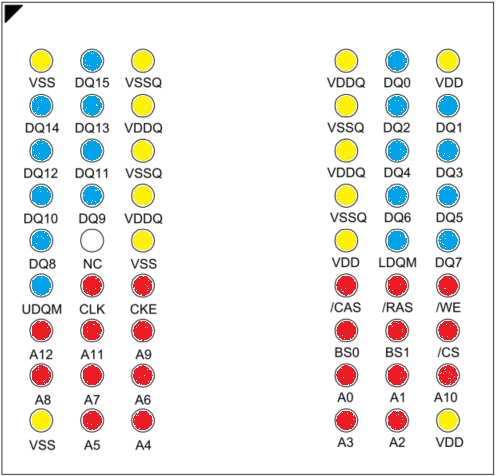

二. SDRAM Pin 介紹

以 Winbond 的 W9825G6KB 16 Bits SDRAM 為例,它的 PIN 可以分為以下三類,不同類型的 Pin 在 Layout 時有不同的注意事項:

1. Power PIN ( 黃色 ):包含 VDD、VSS、VDDQ、VSSQ,

*VDDQ 和 VSSQ 為驅動 Pin 腳的電源 & 地

2. Control PIN ( 紅色 ):包括 CLK、CS、RAS、CAS、WE、BA 和 A0-A11,這些 PIN 用於控制 SDRAM 的操作。

*CS 是 Chip Select,用於選擇 SDRAM ( 使用複數 SDRAM 時 )

*RAS 和 CAS 是 Row Address Select 和 Column Address Select,用於選擇存取的記憶體位置,並將其讀取或寫入

*WE 是 Write Enable,用於決定此次操作是讀取或寫入

*BA 是 Bank Address,用於選擇 SDRAM 中對應的 Bank

*A0-A11 是 Address 輸入,用於指定要操作的 SDRAM 位址

3. Data PIN ( 藍色 ):包含 DQ0-DQ15 和 DM0-DM1,這些 PIN 用於傳輸實際的資料

*DM0 和 DM1 是 Data Mask,用於指示哪些資料位是有效的。

三. Layout 重點

1. 在 SDRAM 的 Layout 中,電源系統是非常重要的一個部分,關係到裝置的穩定性和可靠性,提供 SDRAM 的 Power Pin 足夠的電才能保證其正常啟動和運作。

在整個系統中,首先需要關注的是總共需要多少的電流才能驅動,必須確保源頭有足夠的供電,否則連 SDRAM 都開不起來就更別提後續了。

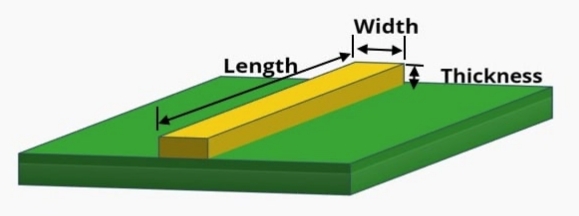

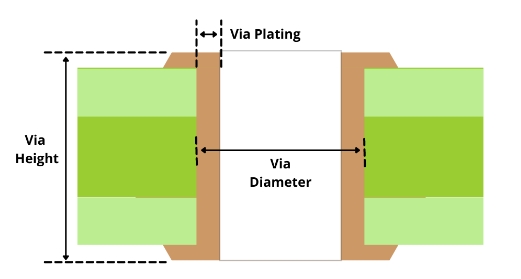

確認了供電之後要怎麼把電導入 SDRAM 呢?答案是透過 Trace 和 VIA,Trace 是指 PCB 上的線路,VIA 是指 PCB 上的貫孔,兩者皆為銅箔,可導電;

但是當 Current 流過時,由於有直流阻抗的存在,部分電流會被耗損並轉換成熱,導致溫度上升,甚至是過熱的情況產生,因此有兩點需要確認;

Trace 的載流能力,取決於走線的厚度、寬度和可以容忍的溫度上升

VIA 的載流能力,取決於孔的內壁厚度、內徑寬度、高度和可以容忍的溫度上升

具體計算公式如下:

I = K△T0.44A0.725

I = 載流能力,能通過多少的電流 ( 安培 )

K = 校正常數,在內層取 0.024,在外層取 0.048

T = 通電後相比於原始溫度提升的溫度,如 5 代表原本 25°C 通電後變成 30°C

A = 電流通過的截面積,Trace = 走線的寬度 x 厚度,VIA = π ( 孔外徑2 - 孔內徑2 )

注:盡量不要使用到理論上的最大電流量,保留一些餘裕,例如只抓八成。

鋪銅的厚度和寬度會影響 PCB 的載流能力,簡單說相同環境條件下越多銅能流過的電流就越大。

2. Control 和 Data Pin 則都需要先進行 controlled impedance ( 阻抗控制或稱阻抗匹配 ),

阻抗匹配是指在設計電路時,將信號源的阻抗和目標的阻抗調整到相等或相近的狀態,以確保信號能夠穩定地傳輸,適當的調整可以減少信號的反射、失真和能量損失;在 PCB 設計中可以透過調整 PCB 的疊構和線寬來達成。

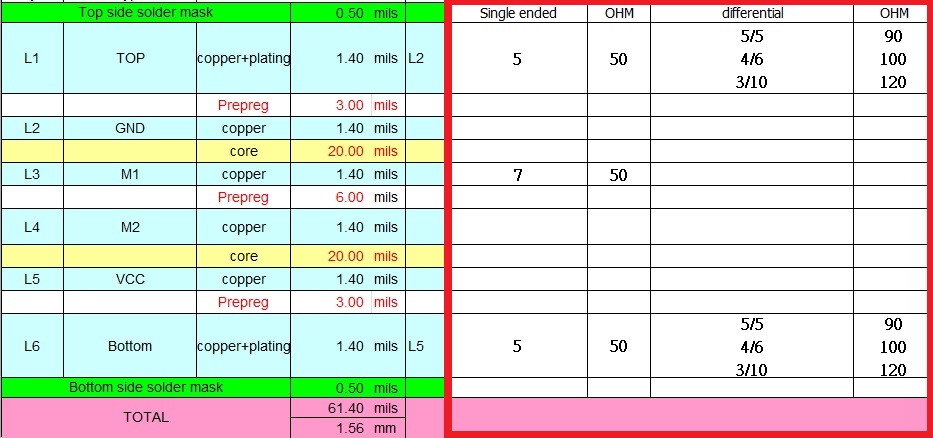

以 SDRAM 為例,根據 Datasheet 需要 50Ω 的 single-ended traces controlled impedance,將此需求提供給製板廠後會收到一張類似下方的疊構建議,可以看到紅框左側是 Single-ended,下方的數字是走線的線寬 ( mil ),旁邊則是阻抗,代表在 Top 或 Bottom 層走 5 mil 的線會得到 50Ω 的 controlled impedance,在 M1 層則須達到 7 mil;紅框右側 differential 下方的數字則是代表 線寬/線距,代表在 Top 或 Bottom 層走 5mil 的線,兩條 differential pair 的線距保持 5mil,可以得到 90Ω 的 controlled impedance;具體可以參考下方示意圖;不同的高速訊號都會有不同的阻抗要求,在向製板廠詢問時需一併提出需求 ( 須先決定各個高速訊號分別要走在哪一層,才能在對應的層透過疊構調出需要的阻抗 )。

3. 接著要進行等長處理,等長處理是指在 PCB 設計中,將信號線的長度設計成相等的長度,以避免信號在傳輸過程中產生反射和干擾,同時確保信號的穩定性和可靠性。

舉個例子:MCU 同時在 8 條 Data 線上送出 High,結果因為每條線的長度落差太大,High 訊號到達的時機有快有慢,導致 SDRAM 取值時原本應該全是 High,結果變成有 High 有 Low,傳送的 Data 變成錯誤的。

故類似 SDRAM 這種高速訊號,一起傳值的 PIN 要進行等長處理;又因為資料的計量單位為 1Byte = 8Bit,故根據這個觀念可以把剩餘的 PIN 拆成以下三組:

第一組:Data0~Data7 + DM0 ( 1 Byte + Data mask )

第二組:Data8~Data15 + DM1 ( 1 Byte + Data mask )

第三組:Control Pin ( CLK、CS、RAS、CAS、WE、BA 和 A0-A11 )

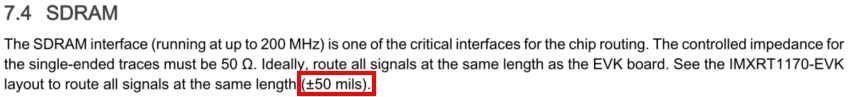

每組線個別進行等長處理,詳細的線長差允許值可以參考各自的 Datasheet 或是 Hardware Designed Guide,以 MIMXRT1170 的 Hardware Development Guide 為例,有提到每組線的長度差要控制在 50 mil 以內,如下圖,

即每組線中最長減最短要小於 50 mil。

4. 在進行 SDRAM 走線時,需要注意參考層 ( 平面 )。

參考層是指最靠近走線的另一層,作為信號傳輸的參考點,提供阻抗和電流回流路徑。通常,參考層是 GND 或電源層。這樣可以減少信號傳輸中的干擾和雜訊,提高信號的穩定性和可靠性。

如 SDRAM 這樣的高速訊號需要確保參考層的連續性,如前文所提到,高速訊號需要進行阻抗控制以保持整組訊號的同步性,參考層如果有變化會導致阻抗跟著有變化,進而造成阻抗不連續,將會導致信號的傳輸中斷、失真和干擾,進而影響整個系統,故其走線下方的參考層不可被切割也不可有其他走線;同時根據上文提到的,為了保證每組訊號的傳輸條件可以一致,同一組線的參考層要始終保持一致,同一時間不要有的線參考 GND 層、有的線參考 VCC 層,如果需要切換參考層則整組線一起切換。

更多的細節和實際範例可以參考本系列的其他文章

四. 參考資料

- Hardware Development Guide for the MIMXRT1160/1170 Processor

- Winbond W9825G6KB Datasheet

評論