DC-DC同步降壓電路設計是一種非常受歡迎與常見的降壓電路設計,而在DC-DC降壓電路設計中,目前業界可以分為傳統式分離式降壓設計與整合式降壓設計,本文主要為探討與比較DC-DC降壓電路中傳統式的分離式降壓電路設計與整合式降壓的電路設計之間優缺:

- 整合式降壓電路與分離式降壓電路設計的優缺點:

2.Layout佈局上的差異:

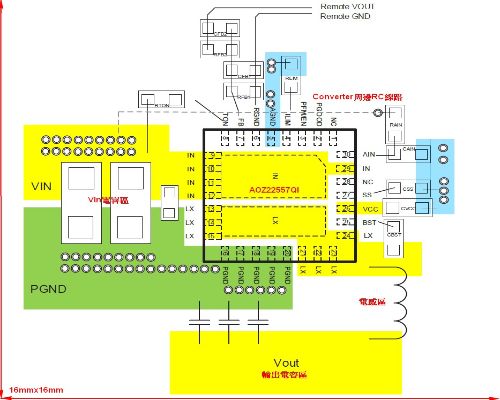

- 整合式設計降壓: 將Controller與H/L Mos皆設計進同一個包裝元件之中,因此設計上所佔用PCB面積較傳統分離式降壓電路設計上的PCB面積少許多。

以AOS所推出AOZ22557QI為設計範例,其整合式降壓本體包裝為4mm×4mm QFN-30L package,包含周邊元件的設計,可實現於16mmx16mm PCB 面積內將一完整降壓電路設計與佈局完成:

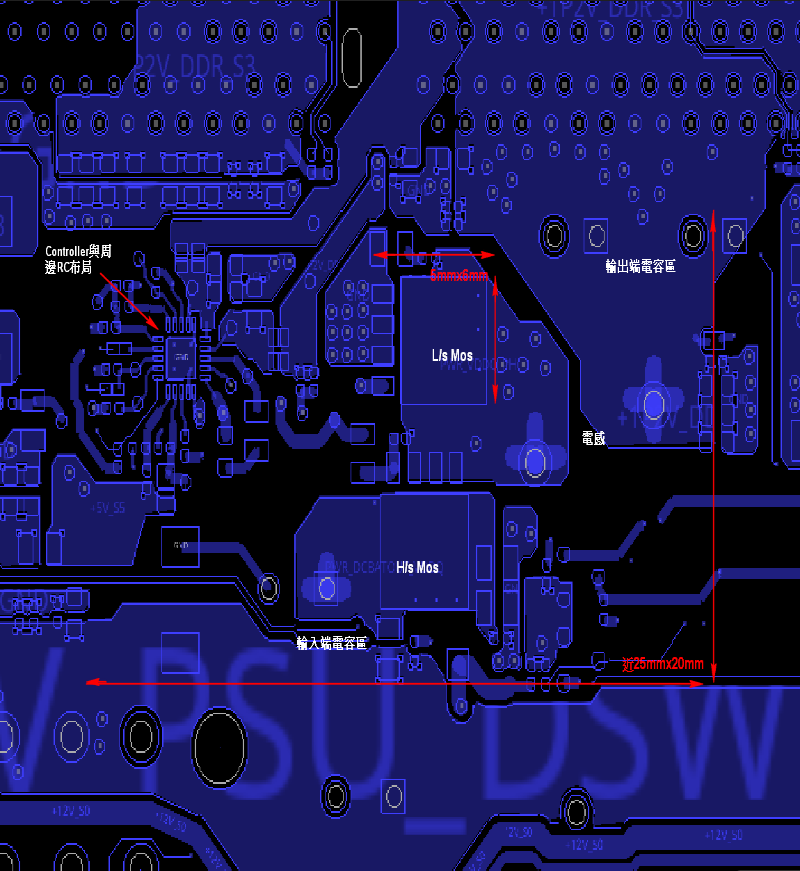

- 分離式設計降壓電路設計的佈局來看,就算選用目前最小包裝的單體Mos 也要3mmx3mm 兩顆再外加上Controller與其周邊線路以及降壓電路所需電感元件等等,也極難滿足在極小的空間中完成電路的設計與PCB佈局.所需空間25mm*20mm.

分離式設計降壓電路 (以常見QFN5x6 package)範例:

結論:

從上比較來看可以很明顯的觀察出, 整合式設計降壓在電路設計與PCB佈局中具有相當大的優勢,可使電路設計在極小的空間中完成設計,現如今許多電子產品皆追求著輕薄短小,不論是桌上型電腦,筆記型電腦,顯示卡,平板,手機等設計都是如此,在此之中整合式降壓的設計優勢不難看出為何可以成為佔據現行設計中達到接近75%份額的香餑餑!

附上AOS COT AOZ22557QI簡介,歡迎各位有需要的至AOS官網搜尋整合式降壓產品或尋找詮鼎的AOS PM,謝謝。

Q&A:

Q1: AOZ22557QI 內部包裝的H/L Mos Rds(on)為多少?

Ans: H-S Mos:11mΩ / L-S Mos:4mΩ.

Q2: AOZ22557QI最高操作頻率?

Ans: 1MHz工作頻率.(Based on application and temperature)

Q3: AOZ22557QI內部Minimum Off Time為多少?

Ans: 規格為Minimum Off Time為350ns.

Q4: AOZ22557QI的靜態電流Quiescent Supply Current為多少?

Ans: 規格為Quiescent Supply Current為400uA.

Q5: AOZ22557QI的應用領域適用哪些部分?

Ans: 數位視訊轉換盒與LCD TV以及伺服器等Point-of-load DC/DC converters皆適用.