UP1727PDDA (WDFN3x3-10)PACKAGE為例說明。

uP1727 是一款具有內部電源開關的高效同步整流降壓轉換器。 固定 1.0MHzPWM 操作可實現最小的輸出紋波和外部組件尺寸

應用於:

- 電池供電的便攜式設備

- 11 WLAN 電源

- FPGA/ASIC 電源

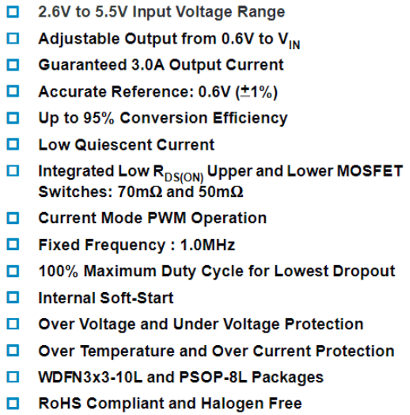

1、UP1727PDDA參數:

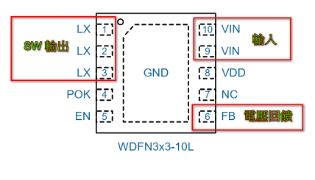

2、IC PIN腳位置圖,可以讓大家進一步了解輸入、輸出、回饋等信號位(圖一)。

說明:VIN為輸入PIN腳、LX為SW輸出PIN腳、FB為電壓回饋PIN腳。 (圖一)

(圖一)

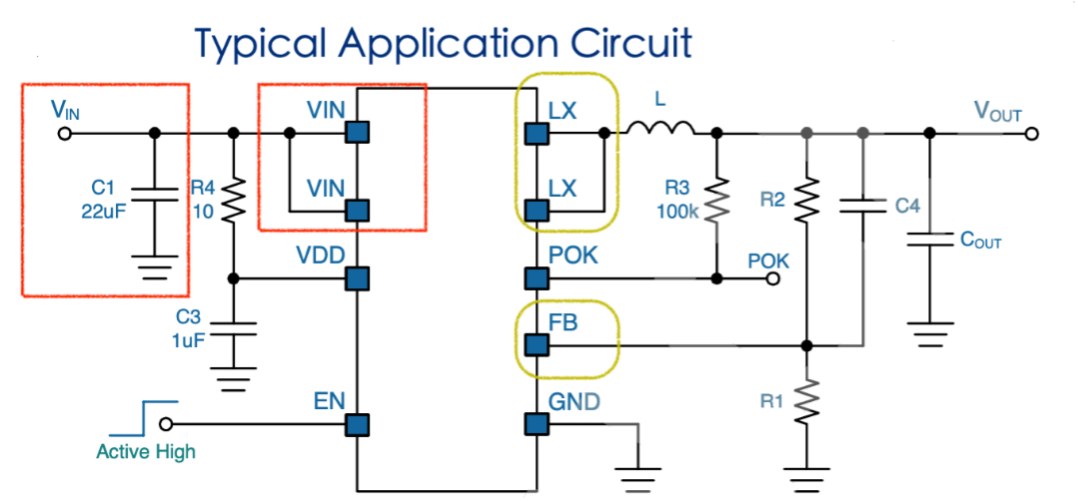

3、UP1727PDDA電路圖(圖二):

說明:VIN為輸入PIN腳、LX為SW輸出PIN腳、FB為電壓回饋PIN腳 (圖二)

(圖二)

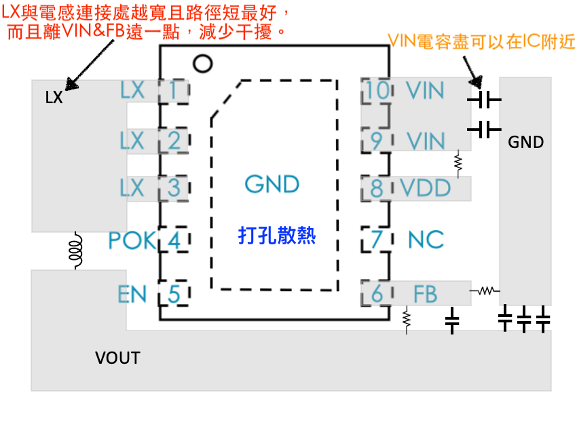

4、下圖為PCB Layout 建議設計方向(圖三):

(圖三)

(圖三)

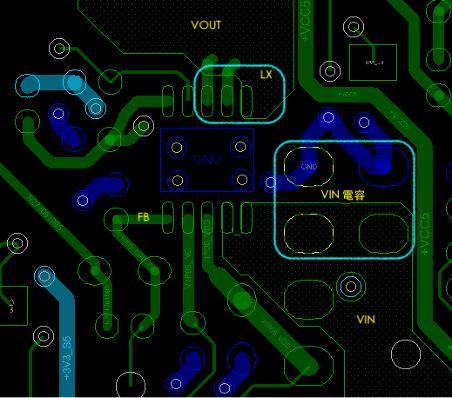

5、uP1727PDDA的PCB 零件佈置(圖四)。

(圖四)

(圖四)

6、PCB Layout佈置注意事項:

1、VIN銅箔面積需大。

2、LX離電感近且用較大銅箔連接。

3、FB遠離VIN、VOUT,減少干擾。

4、VIN電容接近電源IC Vin Pin。

5、電源IC 的中間GND區需打孔散熱。

6、電源IC下方盡量不要走線,避免干擾。

以上為簡易的UP1727PDDA (WDFN3x3-10)PACKAGE PCB佈置時需要注意事項。

參考文獻:UPI uP1727PDDA datasheet

https://www.upi-semi.com/files/2140/6c28df7a-f853-11e8-8d44-d30dc7bf67c5

PCB佈置技術應用問答:

Q/A1 問:若FB放在VIN或VOUT旁邊,會有什麼問題發生?

答:回饋訊號將被嚴重干擾,使得回饋訊號失針。

Q/A2 問:如果因為板子空間有限,使得FB在無法避免的情況之下,需要放在VIN或VOUT附近,請問有沒有其他可以建議的方向?

答:若真的無法避免,那就放在不同層面!例如VIN & VOUT在第一層,一般第二層會是GND,就看看是否可以放在第三層之後,越遠越好。

Q/A3 問:文內介紹的電源IC,有在市售中的板子上嗎?!

答:有。有應用在Lenovo的MOTHER BOARD中。

Q/A4 問:IC中的GND區,要是沒有打孔,會怎樣嗎?

答:會因為散熱不良,造成效率變差。且在打孔的時候,盡量平均分配,不要太集中。

Q/A5 問:請問有這一顆IC實測的效率表嗎?

答:有,如下。

|

Win(W) |

Wout(W) |

efficiency |

|

0.00153 |

0.00000 |

0.00% |

|

1.05682 |

1.00000 |

94.62% |

|

0.66321 |

0.60432 |

91.12% |

|

0.97802 |

0.90648 |

92.68% |

|

1.29158 |

1.20864 |

93.58% |

|

1.60794 |

1.51080 |

93.96% |

|

1.92557 |

1.81296 |

94.15% |

|

2.24499 |

2.11428 |

94.18% |

|

2.56630 |

2.41632 |

94.16% |

|

2.88901 |

2.71836 |

94.09% |

|

3.21299 |

3.02040 |

94.01% |

|

3.53879 |

3.32244 |

93.89% |

|

3.86675 |

3.62448 |

93.73% |

|

4.19710 |

3.92652 |

93.55% |

|

4.52734 |

4.22856 |

93.40% |

|

4.86081 |

4.53060 |

93.21% |

|

5.19528 |

4.83264 |

93.02% |

|

5.53263 |

5.13468 |

92.81% |

|

5.87179 |

5.43672 |

92.59% |

|

6.21165 |

5.73876 |

92.39% |

|

6.55463 |

6.04080 |

92.16% |