作者:Friedrichs Peter 翻譯:趙佳

碳化矽(SiC)的性能潛力是毋庸置疑的,但設計者必須掌握一個關鍵的挑戰:確定哪種設計方法能夠在其應用中取得最大的成功。

先進的器件設計都會非常關注導通電阻,將其作為特定技術的主要基準參數。 然而,工程師們必須在主要性能指標(如電阻和開關損耗),與實際應用需考慮的其他因素(如足夠的可靠性)之間找到適當的平衡。

優秀的器件應該允許一定的設計自由度,以便在不對工藝和版圖進行重大改變的情況下適應各種工況的需要。 然而,關鍵的性能指標仍然是儘可能低的比電阻,並結合其他重要的參數。 圖1顯示了我們認為必不可少的幾個標準,或許還可以增加更多。

圖1:SiC MOSFET的魯棒性和製造穩定性(右)必須與性能參數(左)相平衡

元件在其目標應用的工作條件下的可靠性是最重要的驗收標準之一。 與已有的矽(Si)器件的主要區別是:SiC元件在更強的內部電場下工作。 因此,設計者應該非常謹慎地分析相關機制。 矽和碳化矽器件的共同點是,元件的總電阻是由從漏極和源極的一系列電阻的串聯定義的。

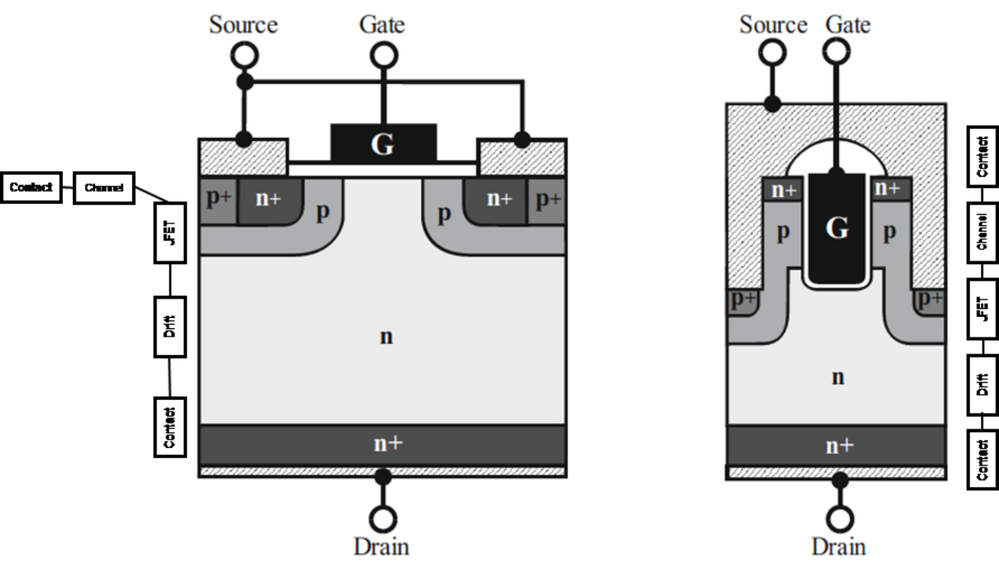

這包括靠近接觸孔的高摻雜區域電阻、溝道電阻、JFET(結型場效應電晶體)區域的電阻以及漂移區電阻(見圖2)。 請注意,在高壓矽MOSFET(金屬氧化物半導體場效應電晶體)中,漂移區阻顯然在總電阻中占主導地位。 而在碳化矽器件中,工程師可以使用具有更高電導率的漂移區,從而降低漂移區電阻的總比重。

圖2:平面DMOS SiC MOSFET(左)和垂直溝槽TMOS SiC MOSFET的剖面圖,以及與電阻有關的貢獻的相應位置

設計者必須考慮到,MOSFET的關鍵部分——碳化矽外延與柵極氧化層(二氧化矽)之間的界面,與矽相比有以下差異:

♦ SiC的單位面積的表面態密度比Si高,導致Si-和C-懸掛鍵的密度更高。 靠近界面的柵極氧化層中的缺陷可能在帶隙內出現,並成為電子的陷阱。

♦ 熱生長氧化物的厚度在很大程度上取決於晶面。

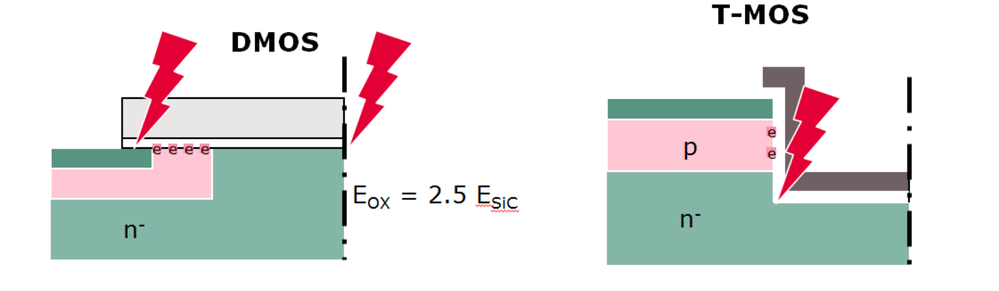

♦ 與矽器件相比,SiC器件在阻斷模式下的漏極誘導電場要高得多(MV而不是kV)。 這就需要採取措施限制柵極氧化物中的電場,以保持氧化物在阻斷階段的可靠性。 另見圖3:對於TMOS(溝槽MOSFET),薄弱點是

溝槽拐角,而對於DMOS(雙擴散金屬氧化物半導體),薄弱點是元胞的中心。

♦ 與Si器件相比,SiC MOS結構在給定的電場下顯示出更高的隧穿電流,因為勢壘高度較低。 因此,工程師必須限制界面上SiC一側的電場。

上面提到的界面缺陷導致了非常低的溝道遷移率。 因此,溝道對總導通電阻的貢獻很大。 所以,SiC相對於矽,因為非常低的漂移區電阻而獲得的優勢,被較高的溝道電阻削弱。

控制柵氧化層的電場強度

一個常用的降低溝道電阻的方法,是在導通狀態下增加施加在柵氧化層上的電場——或者通過更高的柵源(VGS(on))偏壓進行導通,或者使用相當薄的柵極氧化層。 所應用的電場超過了通常用於矽基MOSFET器件的

數值(4至5MV/cm,而矽中最大為3MV/cm)。 在導通狀態下,處於這種高電場的柵氧化層有可能加速老化,並限制了篩選外在氧化物缺陷的能力[1]。

左圖:平面MOSFET(半元胞)的典型結構。 它顯示了與氧化物場應力有關的兩個敏感區域。

右圖:溝槽式MOSFET(半元胞)的典型結構。 這裡的關鍵問題是溝槽邊角的氧化層應力。

基於這些考慮,很明顯,SiC中的平面MOSFET器件實際上有兩個與氧化物場應力有關的敏感區域,如圖3的左邊部分所示。 首先,在反向阻斷模式下,漂移區和柵極氧化物界面存在高電場應力。 其次,柵極和源極之間的重疊部分在導通狀態下有應力。

在導通狀態下的高電場被認為是更危險的,因為只要保證導通時的性能,就沒有器件設計措施可以減少導通狀態下的電場應力。 我們的總體目標是在儘量減小SiC的RDS(on)的同時,保證柵極氧化層安全可靠。

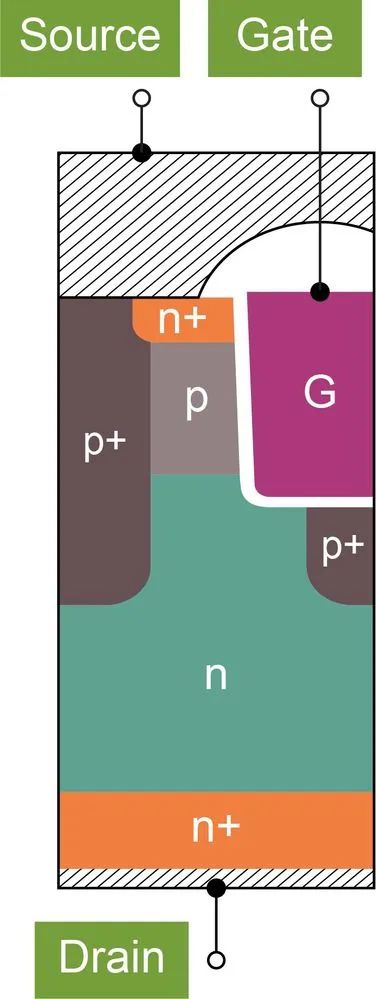

因此,我們決定放棄DMOS技術,從一開始就專注於溝槽型器件。 從具有高缺陷密度的晶面轉向其他更有利的晶面方向,可以在低柵氧化層場強下實現低通道電阻。

我們開發了CoolSiC™ MOSFET元胞設計,以限制通態和斷態時柵極氧化物中的電場(見圖4)。 同時,它為1200V級別提供了一個有吸引力的比導通電阻,即使在大規模生產中也能以穩定和可重複的方式實現。 低導通電阻使得VGS(on)電壓可以使用低至15V的偏壓,同時有足夠高的柵源-閾值電壓,通常為4.5V。 這些數值是SiC電晶體領域的基準。

該設計的特點包括通過自對準工藝將溝道定位在一個單一的晶面。 這確保了最高的溝道遷移率,並縮小了閾值電壓分布範圍。 另一個特點是深p型與實際的MOS溝槽在中心相交,以便允許窄的p+到p+間距尺寸,從而有效地屏蔽溝槽氧化層拐角。

總之,我們可以說,應用於我們的CoolSiC™器件的設計理念不僅提供了良好的導通電阻,而且還為大規模生產提供了可靠的製造工藝。

參考閱讀

文章來源:英飛凌工業半導體

請掃描二維碼關注英飛凌工業半導體微信

評論