1. 前言

MAC 是 Media Access Control 的縮寫,是以太網標準里定義的一個 Control,通常集成在晶片裡,掛在 CPU 的數據總線上,主要功能是打包 CPU 發送的數據給 PHY,或者解包從 PHY 收到的數據給 CPU。

MAC(Media Access Control) 和 MII(Media Independent Interface) 是以太網中的兩個重要組件。MII 用於連接 MAC 和 PHY(Physical Layer) 晶片。

RMII(Reduced Media Independent Interface)只需使用半雙工模式,是一種更為精簡的 MII 接口,用於減少接口引腳數和功耗。

在方案設計時,工程師可根據實際需要來選擇適合的接口。本文旨在通過 E3110 開發板的以太網 MII & RMII 做一個簡單的介紹。

2. MII 接口

2.1 MII 概述

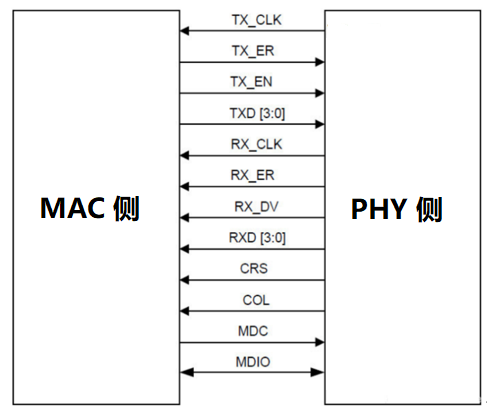

MII(Media Independent Interface),它是一種標準化的接口,定義了一組信號,這些信號包括數據、時鐘、同步、控制等。MII 接口通常用於以太網交換機、網絡接口卡等設備中,它可以支持傳輸速率為 10 Mbps 或 100 Mbps 的以太網協議。MII 接口還可以與 PHY(物理層)器件相連,從而將數據從邏輯層傳輸到物理層,完成數據的編碼、調製和解調等操作。下圖為 MAC 與 PHY 的 MII 硬體連接示意圖:

圖 2-1 MII 硬體連接示意圖

2.2 MII接口引腳解析

MII 包括一個數據接口,以及一個 MAC 和 PHY 之間的管理接口:

MII 數據接口包含 16 個信號和 2 個管理接口信號,當 CLK 信號為 25MH(對應100Mb/s)或 2.5MHz(對應10Mb/s),數據傳輸的位寬為 4 位。

|

信號名稱 |

描述 |

方向 |

|

TX CLK |

發送數據使用的時鐘信號,對於10M位/s的數據傳輸,此時鐘為2.5MHz,對於100M位/s的數據傳輸,此時鐘為25MHz。 |

PHY->MAC |

|

TX ER |

發送數據錯誤 |

MAC->PHY |

|

TX EN |

傳輸使能信號,此信號必需與數據前導符的起始位同步出現,並在傳輸完畢前一直保持。 |

MAC->PHY |

|

TXD(O-3) |

發送數據線,每次傳輸4位數據,數據在MII_TX_EN信號有效時有效。MII_TXD[0]是數據的最低位,MII_TXD[3]是最高位。當MII_TX_EN信號無效時,PHY忽略傳輸的數據。 |

MAC->PHY |

|

RX CLK |

接收數據使用的時鐘信號,對於10M位/s的數據傳輸,此時鐘為2.5MHz,對於100M位/s的數據傳輸,此時鐘為25MHz。 |

PHY->MAC |

|

RX DV |

接收數據使能信號,由PHY控制,當PHY準備好數據供MAC接收時,使能該信號。此信號必需和幀數據的首位同步出現,並保持有效直到數據傳輸完成。在傳送最後4位數據後的第一個時鐘之前,此信號必需變為無效狀態。為了正確的接收一個幀,有效電平不能滯後於數據線上的SFD位出現。 |

PHY->MAC |

|

RX ER |

接收出錯信號,保持一個或多個時鐘周期(MII_RX_CLK)的有效狀態,表明MAC在接收過程中檢測到錯誤。具體錯誤原因需配合MII_RX_DV的狀態及MII_RXD[3:0]的數據值。 |

PHY->MAC |

|

RXD(O-3) |

接收數據線,每次接收4位數據,數據在MII_RX_DV信號有效時有效。MII_RXD[0]是數據的最低位,MII_RXD[3]是最高位。當MII_RX_EN無效,而MII_RX_ER有效時,MII_RXD[3:0]數據值代表特定的信息 |

PHY->MAC |

|

CRS |

載波偵聽信號,僅工作在半雙工模式下,由PHY控制,當發送或接收的介質非空閒時,使能此信號。 PHY必需保證MII_CRS信號在發生衝突的整個時間段內都保持有效,不需要此信號與發送/接收的時鐘同步。 |

PHY->MAC |

|

COL |

衝突檢測信號,僅工作在半雙工模式下,由PHY控制,當檢測到介質發生衝突時,使能此信號,並且在整個衝突的持續時間內,保持此信號有效。此信號不需要和發送/接收的時鐘同步。 |

PHY->MAC |

|

MDIO |

是 PHY 和 STA 之間的雙向信號。 它用於在 PHY 和 STA 之間傳輸控制信息和狀態。 控制信息由 STA 同步地針對 MDC 驅動並且由 PHY 同步地採樣。 狀態信息由 PHY 針對 MDC 同步驅動並由 STA 同步採樣。 |

MAC 雙向 PHY |

|

MDC |

由站管理實體向 PHY 提供,作為在 MDIO 信號上傳送信息的定時參考。 MDC 是一種非周期性的信號,沒有最高或最低時間。 無論 TX_CLK 和 RX_CLK 的標稱周期如何,MDC 的最小高低時間應為 160 ns,MDC 的最小周期為 400 ns。 |

MAC->PHY |

表 2-2 MII 數據接口和管理接口引腳解析

2.3 MII 時鐘源

MII 時鐘源通常由一個晶體振盪器或者一個外部時鐘源提供時鐘信號,以確保設備在傳輸數據時保持同步。此外,MII 時鐘源還可能包含一個鎖相環電路(PLL),用於生成一個更高精度的時鐘信號,以適應不同的網絡速率和協議。

在設計網絡通信設備時,選擇適當的 MII 時鐘源至關重要。正確的時鐘源可以確保網絡設備之間的數據傳輸和同步,從而提高網絡性能和可靠性

總之,MII 時鐘源通過提供一個統一的時鐘信號來同步數據的傳輸,從而確保了數據的可靠性和穩定性,是計算機網絡中重要的接口標準之一。

3. RMII 接口

3.1 RMII 概念

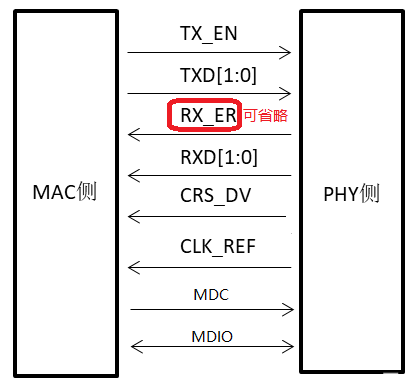

RMII(Reduced Media Independent Interface) 是 MII 的簡化接口。RMII 接口比 MII 接口擁有更少的 I/O 傳輸,RMII(8 根線)只有7根數據線 和 1 根控制線,其中 RX_ER 可以省略不接。此外,RMII 還需要一個時鐘線,這個時鐘線可以是 50MHz 或 25MHz 的時鐘信號。RMII 傳輸速率和 MII 一樣,支持 10Mb/s 和 100Mb/s。不同的是 RMII 在 10Mb/s 和 100Mb/s 下 CLK 都為 50MHz。即在相同速率下 RMII 比 MII 數據線少了一半,極大的減小了走線壓力和埠壓力。下圖為 MAC 與 PHY 的 RMII 硬體連接示意圖,需要注意的是:如果是需要自適應 10Mb/s 和100Mb/s,TX_CLK 是由 PHY 晶片發出。

圖 3-1 RMII 硬體連接示意圖

3.2 RMII 數據接口和管理接口引腳解析

|

信號名稱 |

描述 |

方向 |

|

RXD(O-1) |

接收數據線,分別傳輸高位和低位數據,數據位寬為2,是MII接口的一半。 |

PHY->MAC |

|

TXD(O-1) |

數據發送信號線,數據位寬為2,數據位寬為2,是MII接口的一半。 |

MAC->PHY |

|

CRS_DV |

信號是由MII接口中的RX_DV和CRS兩個信號合併而成。當介質不空閒時,CRS_DV和RECLK相異步的方式給出。當CRS比RXDV早結束時(即載波消失而隊列中還有數據要傳輸時),就會出現CRSDV在半位元組的邊界以25MHz/2.5MHz的頻率在0、1之間的來回切換。因此,MAC能夠從 CRSDV中精確的恢復出RXDV和CRS。 |

PHY->MAC |

|

CLK_REF |

是由外部時鐘源提供的50MHz參考時鐘,與MII接口不同,MII接口中的接收時鐘和發送時鐘是分開的,而且都是由PHY晶片提供給MAC晶片的。這裡需要注意的是,由於數據接收時鐘是由外部晶振提供而不是由載波信號提取的,所以在PHY層晶片內的數據接收部分需要設計一個FIFO,用來協調兩個不同的時鐘,在發送接收的數據時提供緩衝。PHY層晶片的發送部分則不需要FIFO,它直接將接收到的數據發送到MAC就可以了。 |

PHY->MAC |

|

RX_ER |

數據接收錯誤提示信號,與MII接口中的該信號線功能一樣。 |

PHY->MAC |

|

TX_EN |

數據發送使能信號,與MII接口中的該信號線功能一樣。 |

MAC->PHY |

|

MDIO |

管理數據輸入輸出,用於傳輸管理數據的輸入和輸出 |

MAC 雙向 PHY |

|

MDC |

管理數據時鐘,用於傳輸管理數據 |

MAC->PHY |

表 3-2 RMII 數據接口和管理接口引腳解析

3.3 RMII 時鐘源

RMII 時鐘源是一種嵌入式系統和網絡設備中常用的接口標準。RMII 時鐘源的原理與 MII 類似,也是通過一個統一的時鐘信號來同步數據的傳輸。與 MII 不同的是,RMII 時鐘源採用了較少的引腳來傳輸數據和時鐘信號。具體來說,RMII 時鐘源將原來 MII 中的 4 條數據線(TXD0、TXD1、RXD0、RXD1)壓縮成了 2 條數據線(TXD、RXD),同時將原來 MII 中的 2 條時鐘線(TX_CLK、RX_CLK)壓縮成了 1 條時鐘線 REF_CLK。這樣做既可以降低成本,又可以提高系統的可靠性和穩定性。需要注意的是,由於 RMII 時鐘源採用了壓縮的數據和時鐘線,因此在設計和實現時需要仔細考慮電路布局和信號完整性等因素,以確保系統的正常運行。

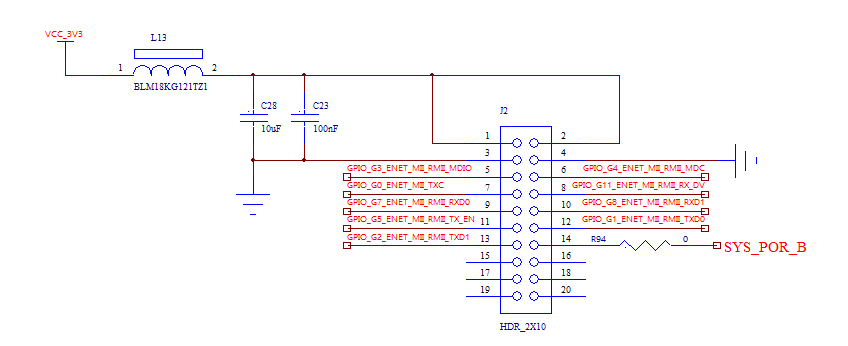

4. E3110 開發板的以太網設計

E3110 開發板設計的以太網外設選用的是在開發板上預留 RMII 的接口,通過 NXP SBC FS5600給以太網 RMII 接口進行 3.3V 供電,開發板上預留的 RMII 接口可以與景略的板子相互接插,實現以太網功能。下圖是 E3110 開發板的 RMII 接口原理圖。

圖 4-1 RMII Ethernet Interface 原理圖

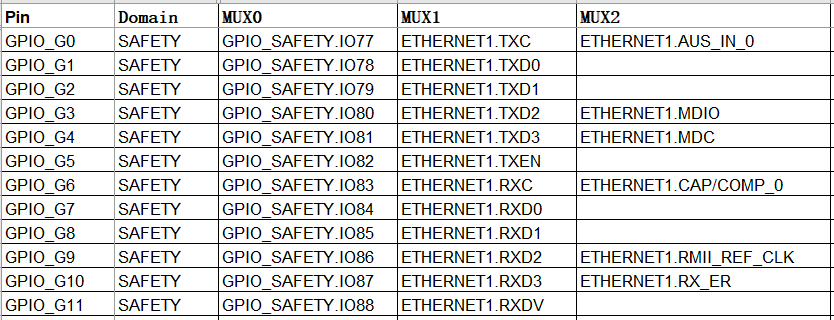

E3110 開發板通過選用 GPIO_G 實現串行輸入輸出 RMII 的接口配對,完成引腳復用,可以通過GPIO(General Purpose Input/Output)來模擬,GPIO 可實現串行輸入輸出,E3110 開發板上會提供 PIN MUX 供用戶自定義使用。具體 E3110 PIN MUX 配置表參考下圖:

圖 4-2 表 E3110 PIN MUX 配置表

每組 SMI 需要兩個 GPIO 口分別來模擬 MDC 和 MDIO,首先需要保證這兩個 GPIO 口不作其他用途,且相應的復用模式設置為 GPIO 模式。

模擬 MDC 是將相應 GPIO 設置為輸出模式(由 MAC 提供時鐘),在 MDIO 上發送和讀取數據時提供時鐘即可,具體來說,向 GPIO 寫 0 即為低電平,向 GPIO 寫 1 即為高電平,電平持續時間可通過 usleep 等待或執行數條空指令來實現。

模擬 MDIO 就是實現一套 read/write 時序,也通過向 GPIO 寫 0 或寫 1 實現,實現原則為改變 GPIO 的輸入/輸出模式,而 read 的後半段即為從 GPIO 上讀數據。

如對此有更多需求,敬請聯繫世平集團 ATU 部門,atu.cn@wpi-group.com。

5. 參考文獻

[1] 以太網詳解(一)-MAC/PHY/MII/RMII/GMII/RGMII基本介紹

[2] 相關網址:https://blog.csdn.net/weixin_44415816/article/details/122280157

[3] 相關網址:https://blog.csdn.net/wjcqwe/article/details/129102669

歡迎在博文下方留言評論,我們會及時回復您的問題。如有更多需求,歡迎聯繫大聯大世平集團 ATU 部門:atu.sh@wpi-group.com

作者:Sandy Yang / 楊羽潔

評論