前言:

在前一篇博文”淺談AOS DRMOS 的LAYOUT (上)”,有提到三點DRMOS 在LAYOUT上需要注意的地方,這篇博文就讓我們繼續的來討論DRMOS 還有哪些在LAYOUT上,還需多加注意地點。

DRMOS 對於LAYOUT設計上,有著特別需要注意的要點,以下再提供三點說明:

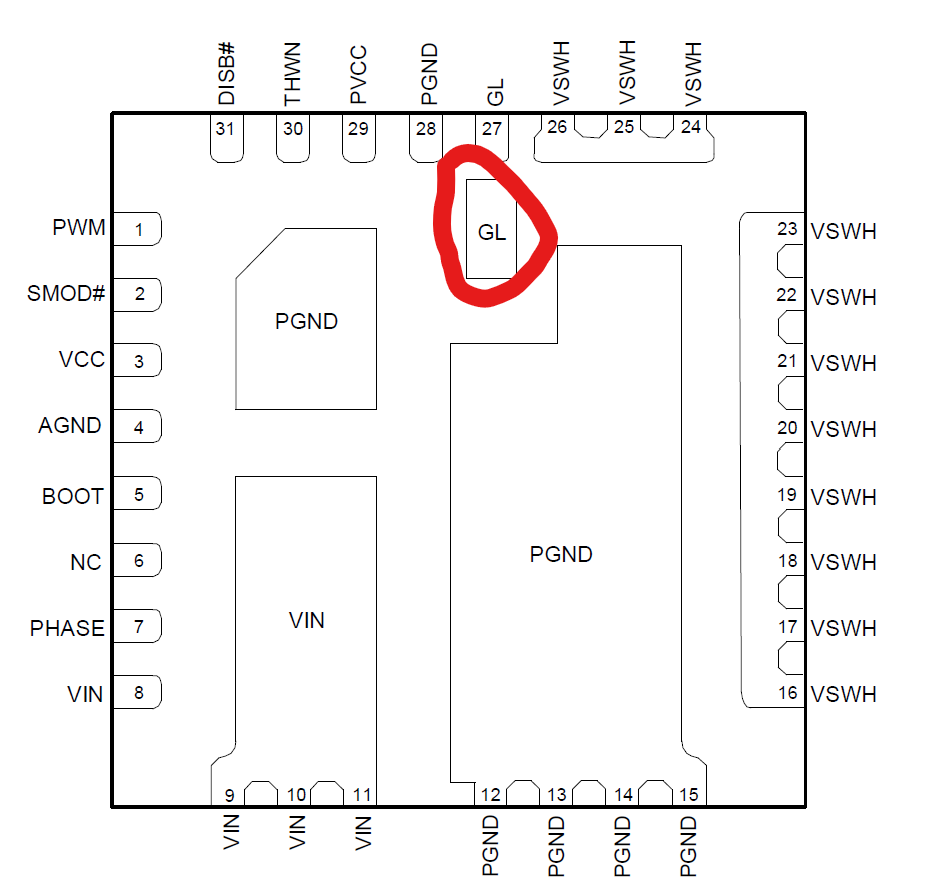

1.DRMOS 底部LOW SIDE GATE 的處理:

以AOS AOZ5311NQI為例,其DRMOS的LOE SIDE GATE一共有2 PIN,除了27 PIN以外,還有在DRMOS 底部還有1 個PIN。以DRMOS零件的設計來看,所有的控制機制,理應全數包在IC內部,無須再從外部給予控制訊號,而底部的GATE PIN 其實是作為DRMOS 腳架上的一個支撐點。當我們在做LAYOUT設計時,因DRMOS的底部,有著三個大的PAD作為VIN及GND使用,當GL的PAD在SMT加工稍微偏差時,其較容易與PGND 產生錫橋(solder bridge),當這樣狀況發生時,負責下橋MOSFET驅動的控制單元會因短路的狀況,而產生過大的電流,進而將DRIVER內部燒毀。基於上述的情形來看,我們會建議這個PIN腳,不製作PAD做焊接也不上錫。

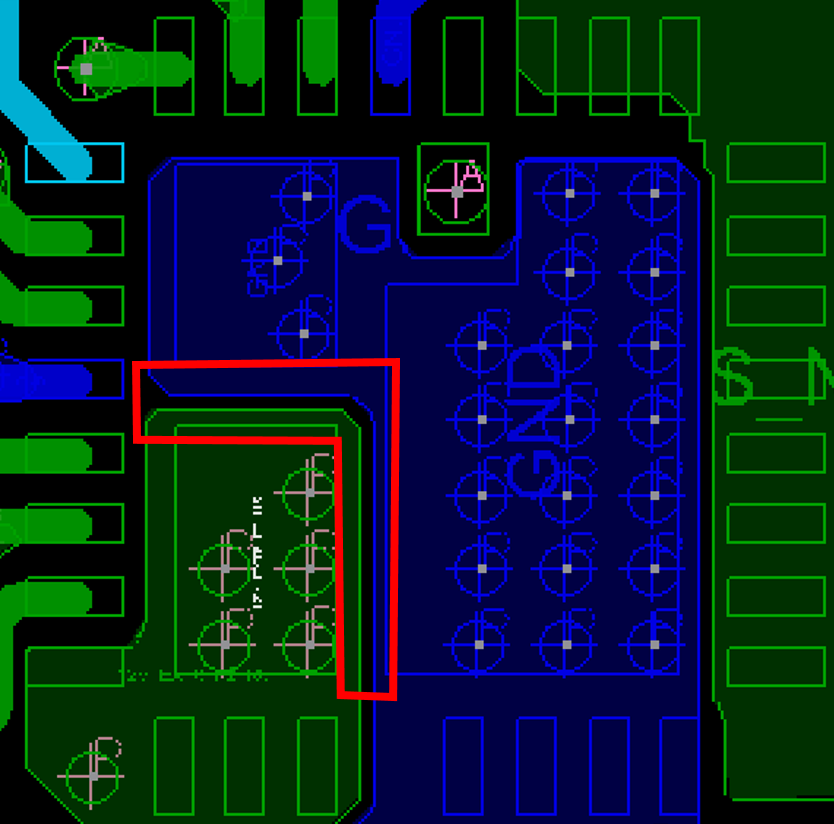

2.底部VIN PAD 與 PGND PAD 的處理:

以AOS AOZ5311NQI為例,下圖所匡列的區域,是在處理DRMOS FA CASE時常見有異常的地方。因為藍色與綠色的這兩塊PAD,其尺寸及面積都不小,在SMT REFLOW迴焊時,錫膏容易產生相互拉扯的狀況,造成DRMOS位移,產生短路的狀況。

當我們在設計DRMOS LAYOUT時,建議在DRMOS 的PAD 與PAB上的PAD能保有最大的接觸面積及最大的間距,同時與PE確認刷錫鋼板開孔的大小與位置,以避免過多的錫量造成REFLOEW 時的拉扯及短路的現象發生。

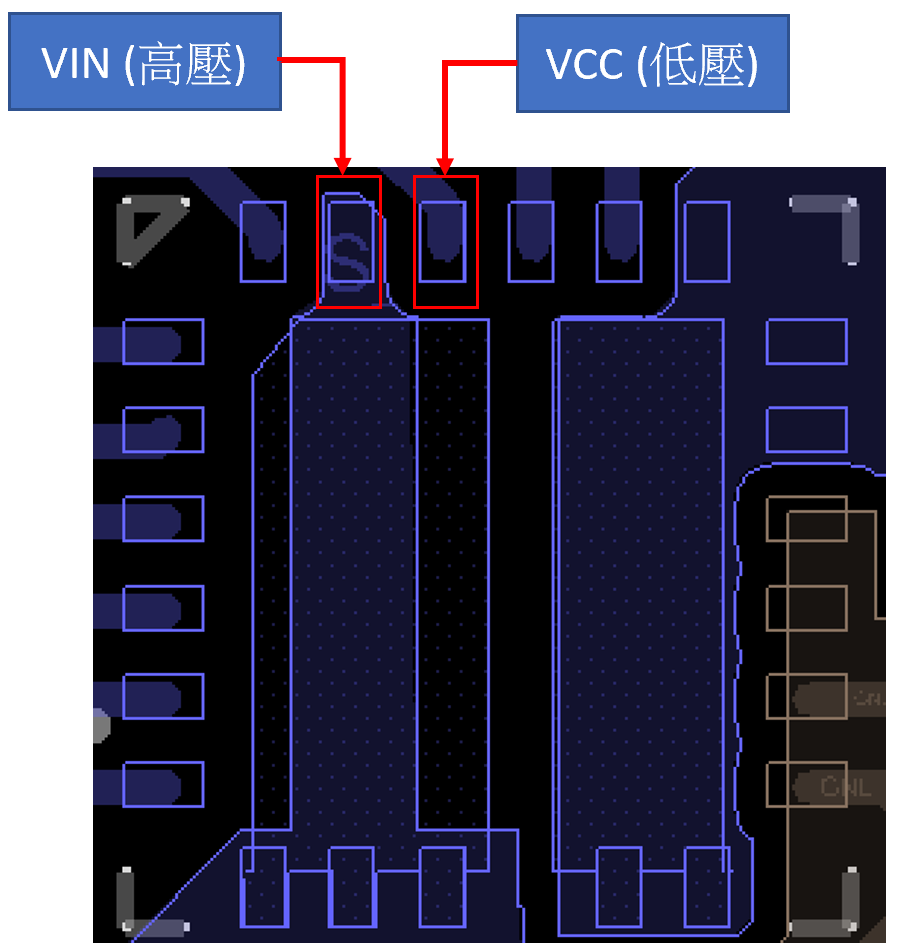

3.高低壓PIN及C PIN 的處理:

其實這類的問題,並不是只有DRMOS會碰到。我們常使用的POL (CONVERTER),這樣的情形,也非常常見。當我們選擇了POWER SOLUTION來做使用時,從IC的腳位上,我們應該就能分辨出哪些是屬於高輸入或低壓PIN腳。當這兩PIN處在相鄰時,對於LAYOUT的設計,我們必須要謹慎一些。因為當碰上IC位移時,高壓便會灌進低壓側,而低壓PIN 一般多為VCC / PVCC / GL 這類的PIN,一旦發生了,DRMOS 或POL 一定會產生DAMAGE,輕則IC損毀,嚴重的有可能因過大的電流產生高熱,進而連PCBA上的PAD一併熔毀。

另外,N.C PIN的問題,當IC本身無需增加FUNCTION時,其多出來的腳位就會被定義為NC。但這樣的腳位有可能會被當作IC腳架的支撐點,所以當我們使用到這類的IC元件時,一般我會建議就保留PAD焊接就好,無須走線或接到GND去。因為我們無法判斷是否有功能,這樣多餘的動作,反而會造成其他的問題發生。

總結

當電子產品走向了輕,薄,短,小之際,相對的在POWER SOLUTION也只能朝向高度集成方向發展。當電子元件功能越來越多,尺寸越來越小的情形下,PIN腳的間距也會越來越小,除了考量SMT製程精度外,LAYOUT設計的優化,也可以協助避免加工上的困難。在這兩篇博文上的概述,希望能對小型化的產品設計,提供一些幫助。

評論