Peripheral component interconnect express (PCIe),為 Intel 於 2004 年發表,剛開始設計是針對高速的聲音與影像串流,之後被用來提升裝置到 Host side 的傳輸速率,常見的應用有 NB、Server的SSD、周邊裝置的傳輸。

PCIe的應用愈來越廣泛,速度也越來越快,相對的layout也需要更加的注意,以避免不必要的應用上之問題。

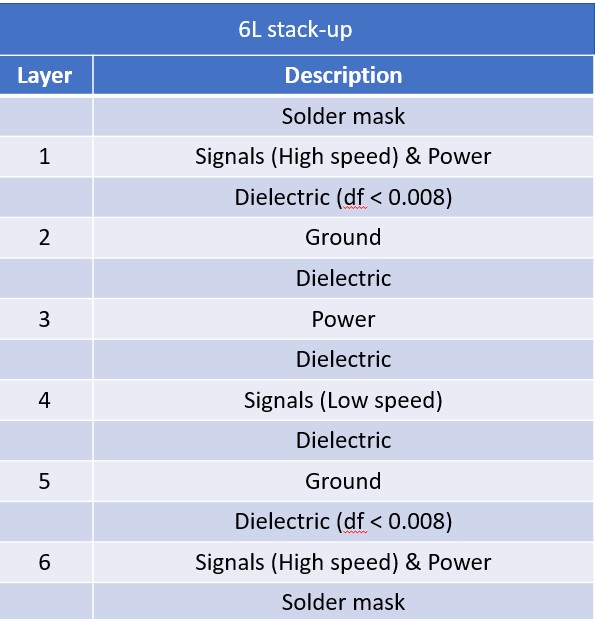

一般而言,建議使用6 或 8 層板,PCIe的高速信號走線,建議以top layer 或 bottom layer 為主,並鄰近 GND layer,以省略 back-drilling ,其它的低速信號與 power 則建議以內層為主。

- PCIe 信號線的differential impedance 務必控制在 85Ω ± 10%

- PCIe 信號線建議reference GND 層 ,而不是 power層,以避免不必要 noise 干擾

- 盡量減少長 Traces 的 insertion lose , 可以選擇 low lose 的 PCB 材質 , 且在traces 佈建的layer (ex. Top layer.) 以下需選用 low lose 電介質 (df < 0.008)

- Power層與 GND層之間電介質厚度不宜超過 3 mil

評論