上一篇我們已經介紹了 MOSFET 的旁路二極體的逆向回復電流,接下來我們將介紹MOSFET切換時Turn on 和 Turn off 的Vds dv/dt 波形探討,本篇會已先介紹MOSFET Turn on 時的Vds dv/dt 波形,本分析都會以圖一作為電路分析,並假設為電感性負載作為討論。

圖一:

圖一:『Switching of the upper and lower MOSFETs』(註1) 出處 TOSHIBA Impacts of the dv/dt Rate on MOSFETs Application Note。

接下來我們介紹MOSFET Turn on 時 Vds dv/dt 波形。

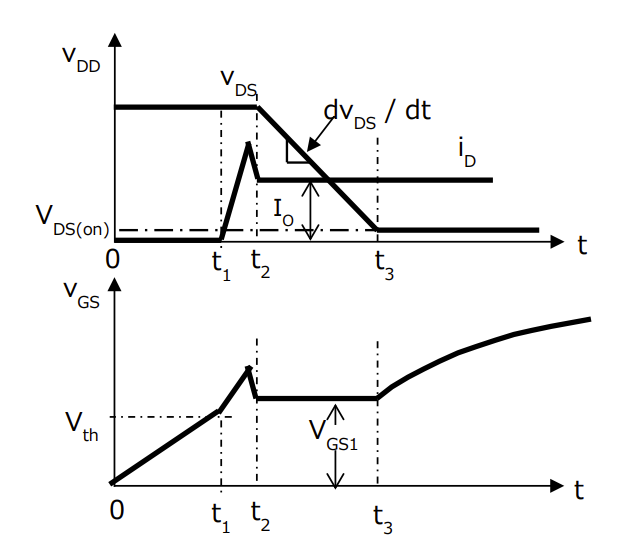

圖二 顯示了圖 一 電路的Turn on 時波形,MOSFET 具有 dv/dt ramp

在 t2 到 t3 期間(即在開關轉換期間)

(1) 0 至 t1(MOSFET 處於 off )

此區間的VGS 電壓作為Gate電阻 R、G-S電容的函數而增加

Cgs 和Gate -drain 電容 Cgd:

VGS = VGG{1-exp{-t/[ R (Cgs+Cgd)]}}----- (1)

(2) t1 至 t2(MOSFET 正在Turn on)

在 t1 時刻,MOSFET 的VGS電壓超過其 VGSth,導致電流流向

開始流入Drain,當 ID 電流等於負載電流 IO 時,形成續流電流,此時為正偏模式二極體進入逆向恢復,ID

由於續流二極體的逆向恢復電流而增加,在此區間,MOSFET 的 VDS電壓保持等於 VDD電壓,Gate電壓 VG 增加會

與從 0 到 t1 的時間段的VG幾乎相同,可由公式(1)所示.

(3) t2 至 t3(MOSFET 正在切換)

隨著續流二極體的逆向恢復電流降至為零,MOSFET 的ID電流達到負載電流IO,然後,Gate電壓下降到 VGS1,此時ID電流會等於 IO。

隨著VD電壓降低,dVDS/dt 導致電流流過Gate-drain 電容 Cgd,該電流表示為

IDG=Cgd・dVDS /dt.

dVDS/dt 斜率是這樣確定的IDG = (VGG-VGS)/R, VGS為Gate pulse 電壓R為Gate電阻。

在此期間,Gate電壓 VGS幾乎保持恆定在VGS1.(此為米勒平台)

(4) t3 後(MOSFET 處於Turn on)

由於Drain 電壓 VDS 在 t3 下降到幾乎為零,Gate電壓開始上升再次由於 R 和 (Cgs+ Cgd)。

Gate電壓計算如下:

VGS= [ VGG–VGS1]{1-exp[-(t-t3) / R ( Cgs+Cgd ) ]}+ VGS1

圖一:

圖一:『Switching of the upper and lower MOSFETs』(註1) 出處 TOSHIBA Impacts of the dv/dt Rate on MOSFETs Application Note。

接下來我們介紹MOSFET Turn on 時 Vds dv/dt 波形。

圖二 顯示了圖 一 電路的Turn on 時波形,MOSFET 具有 dv/dt ramp

在 t2 到 t3 期間(即在開關轉換期間)

(1) 0 至 t1(MOSFET 處於 off )

此區間的VGS 電壓作為Gate電阻 R、G-S電容的函數而增加

Cgs 和Gate -drain 電容 Cgd:

VGS = VGG{1-exp{-t/[ R (Cgs+Cgd)]}}----- (1)

(2) t1 至 t2(MOSFET 正在Turn on)

在 t1 時刻,MOSFET 的VGS電壓超過其 VGSth,導致電流流向

開始流入Drain,當 ID 電流等於負載電流 IO 時,形成續流電流,此時為正偏模式二極體進入逆向恢復,ID

由於續流二極體的逆向恢復電流而增加,在此區間,MOSFET 的 VDS電壓保持等於 VDD電壓,Gate電壓 VG 增加會

與從 0 到 t1 的時間段的VG幾乎相同,可由公式(1)所示.

(3) t2 至 t3(MOSFET 正在切換)

隨著續流二極體的逆向恢復電流降至為零,MOSFET 的ID電流達到負載電流IO,然後,Gate電壓下降到 VGS1,此時ID電流會等於 IO。

隨著VD電壓降低,dVDS/dt 導致電流流過Gate-drain 電容 Cgd,該電流表示為

IDG=Cgd・dVDS /dt.

dVDS/dt 斜率是這樣確定的IDG = (VGG-VGS)/R, VGS為Gate pulse 電壓R為Gate電阻。

在此期間,Gate電壓 VGS幾乎保持恆定在VGS1.(此為米勒平台)

(4) t3 後(MOSFET 處於Turn on)

由於Drain 電壓 VDS 在 t3 下降到幾乎為零,Gate電壓開始上升再次由於 R 和 (Cgs+ Cgd)。

Gate電壓計算如下:

VGS= [ VGG–VGS1]{1-exp[-(t-t3) / R ( Cgs+Cgd ) ]}+ VGS1

圖二:

圖二:『Turn-on curve』(註1) 出處 TOSHIBA Impacts of the dv/dt Rate on MOSFETs Application Note。

接下來我們介紹MOSFET Turn off 時 Vds dv/dt 波形。

圖三顯示了圖一電路的 turn off 波形,MOSFET 在 t2 到 t3 期間為即開關轉換期間,有一個 dv/dt 的波形,

(1) 0 到 t1(MOSFET 處於 on)

此區間的 Gate 電壓 VGS 作為 Gate電阻 R、Gate-Source 電容 Cgs 和 Gate-Drain 電容 Cgd 的函數而降低,公式如下:

VGS = VGG・exp{-t/ [R・(Cgs+Cgd)] ----- (2)

(2) t1 至 t2(MOSFET 正在 Turn off)

當Gate 電壓達到 VGS1 時,MOSFET 的 Drain 電流達到負載電流 IO,Drain電壓開始升高。隨著Drain電壓的增加,dVDS/dt 斜坡導致電流流過Gate-Drain電容 Cgd。 該電流表示為

IDG=Cgd・dVDS /dt.

確定 dVDS/dt 比率,使 IDG 等於電流 VGS/R (VGG=0),它是Gate pluse 電壓 (=0 V) 和 Gate 電阻 R 的函數.

在 t1 到 t2 期間,Gate電壓 VGS 幾乎保持在 VGS1 不變,而 MOSFET 的Drain電壓 vDS 增加到電源電壓 VDD.

(3) t2 至 t3(MOSFET 正在切換)

當Drain電壓 VDS 達到電源電壓 VDD 時,續流二極體導通. 同時,Drain電流ID 開始下降,由於 R 和 (Cgs+Cgd),Gate電壓 VGS 再次開始下降並繼續下降,直到達到 Vth. 在此期間,VGS表示為:

VGS1・exp{-(t-t2) / [R・(Cgs+Cgd)]}.

(4) t3 後(MOSFET 處於 off 狀態)

由於電流Drain為零,Drain電壓VDS等於電源電壓VDD, dVDS/dt為零, Gate電壓因R和(Cgs+Cgd)再次開始下降.在此期間,VGS表示為:

VGS =VGS1・exp{-(t-t2)/[R・(Cgs + Cgd)]}.

圖三:

圖三:『Turn-off curve』(註1) 出處 TOSHIBA Impacts of the dv/dt Rate on MOSFETs Application Note。