- SPI 簡介

1. SPI 全名為 Serial Peripheral Interfaces,又稱 ”串列外設介面“

2. 串列外設介面一般標準為主機和從機,可分為單工 / 半雙工 / 全雙工

3. 有 4 條通道,分別是 : SCLK ( 時脈通道 ) , MOSI ( 主機輸出通道,從機輸入通道 ) , MISO ( 主機輸入通道,從機輸出通道 ) , SS / CS ( 從機選擇通道 )

- SPI 4種模式

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 638 )

1. Mode 0 : CPHA = 0 , CPOL = 0 , SCK reset state is low, Data sample in first edge

2. Mode 1 : CPHA = 0 , CPOL = 1 , SCK reset state is high, Data sample in first edge

3. Mode 2 : CPHA = 1 , CPOL = 0 , SCK reset state is low, Data sample in second edge

4. Mode 3 : CPHA = 1 , CPOL = 1 , SCK reset state is high, Data sample in second edge

- SPI 通訊 ( 8 bit , mode 0 為例 )

* 註 : 資料出處, iT邦幫忙 "Day 13:SPI (Part 1) - 原來是 Shift Register 啊!我還以為是 SPI 呢!" ( https://ithelp.ithome.com.tw/articles/10245910 )

1. Mater 工作於 mode 0,所以 SS 閒置十為高電平

2. Master 透過 SS 拉為低電平向 slave 告知即將傳送訊號

3. MOSI 開始發送 8 bit 數據

4. 因為 mode 0,故在 SS 拉為低電平後的第一個 SCL 邊緣判定數據,所以此時會有一段 thold,在這段時間內訊號必須穩定輸出

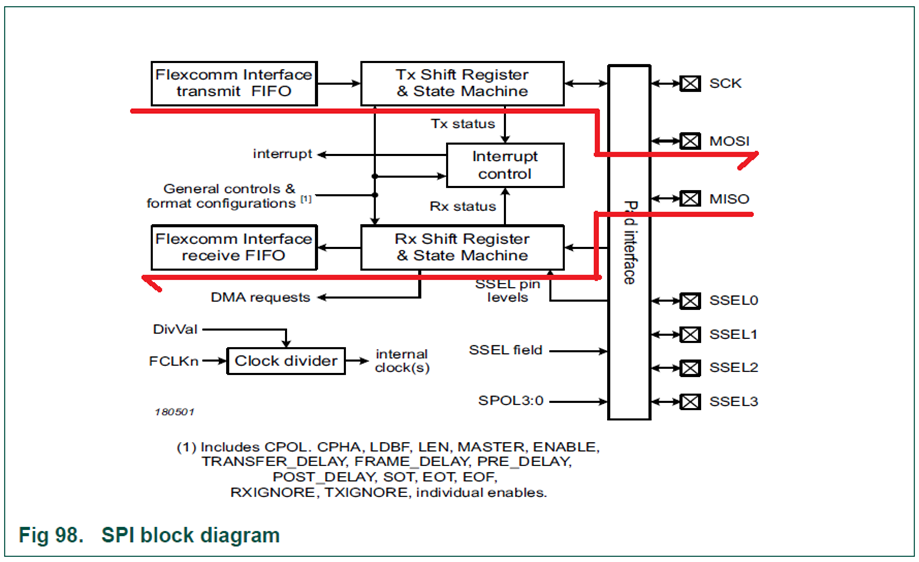

- SPI 方塊圖

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 622 )

1. 搭配 Flexcomm 可支援 6 組標準和 1 組高速的 SPI

2. 皆可設置為主機 ( master ) 或從機 ( slave );主機最多可支援 4 個從機

3. 支援最小 4 bits 最大 16 bits 的數據傳輸,可透過軟體傳輸更大的數據

4. SPI 支援各自傳送 FIFO 與接收 FIFO

5. SPI 支援 DMA ( DIRECT MEMORY ACCESS )

6. 使用標準 Flexcomm 時,主機時脈不得超過 30 MHz,從機不得超過 20 MHz;高速 Flexcomm 則皆不得超過 50 MHz

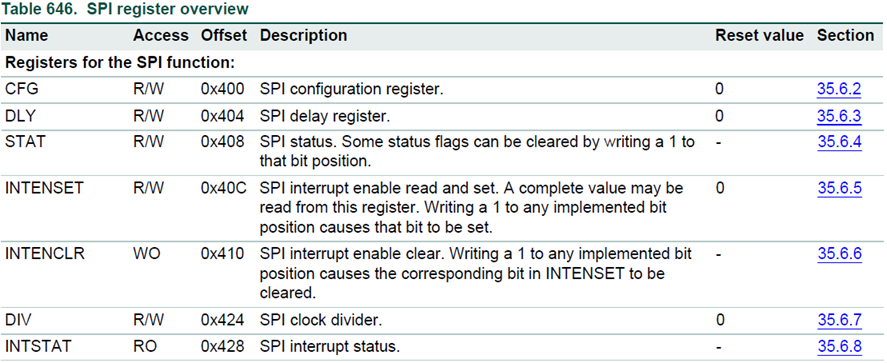

- SPI 暫存器

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 622 )

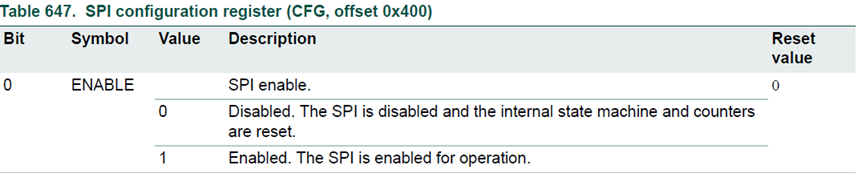

1. CFG : SPI 功能配置

2. DLY : SPI 延遲設置

3. STAT : SPI 狀態暫存器

4. INTENSET : SPI 中斷設置

5. INTENCLR : SPI 中斷清除

6. DIV : SPI SCL 除頻器

7. INTSTAT : SPI 中斷狀態暫存器

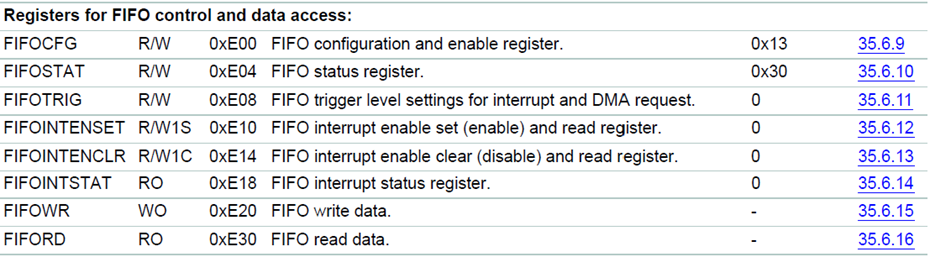

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 623 )

8. FIFOCFG : FIFO 功能配置

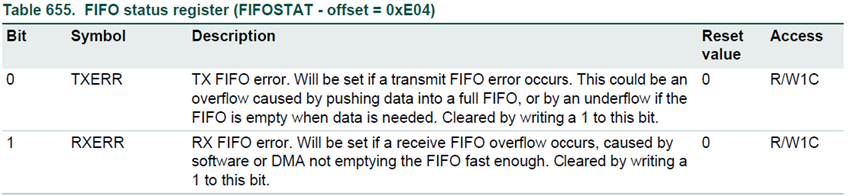

9. FIFOSTAT : FIFO 狀態暫存器

10. FIFOTRIG : FIFO 中斷和 DMA ( DIRECT MEMORY ACCESS ) 請求

11. FIFOINTENSET : FIFO 中斷設置

12. FIFOINTENCLR : FIFO 中斷清除

13. FIFOINTSTAT : FIFO 中斷狀態暫存器

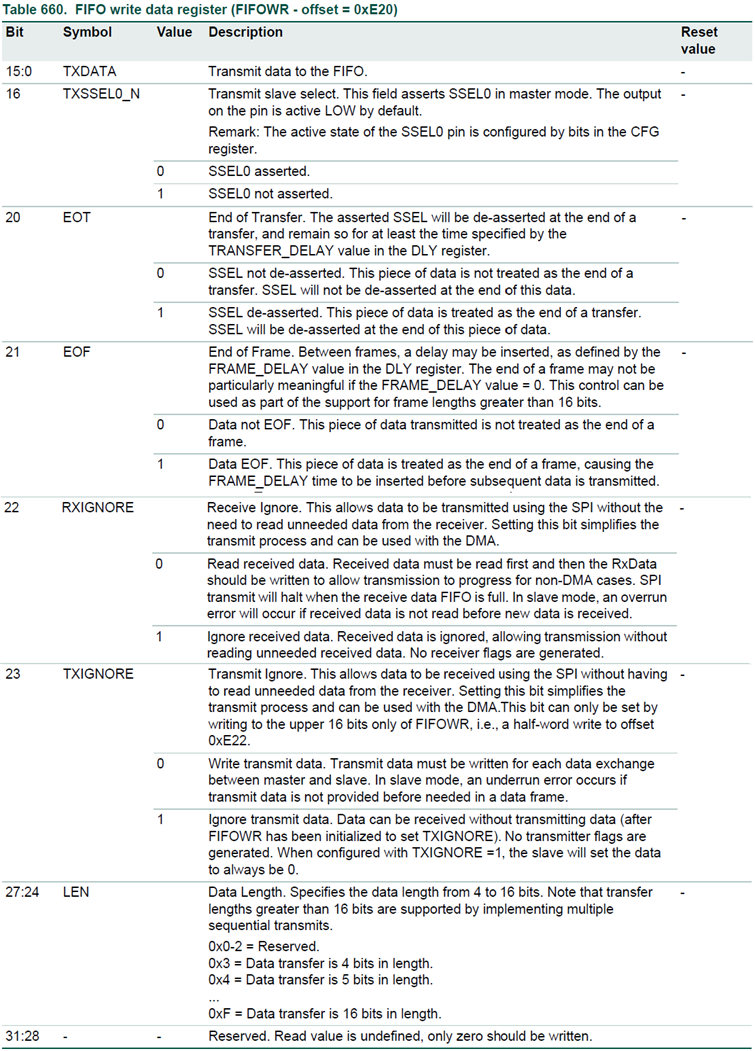

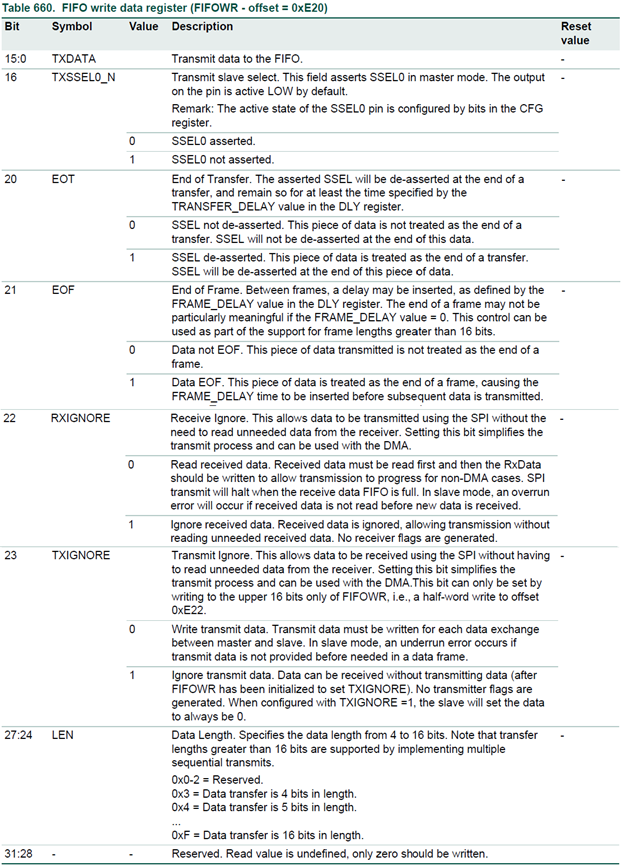

14. FIFOWR : FIFO 寫入

15. FIFORD : FIFO 讀取

- Flexcomm 支持 6 組標準 SPI 和 1 組高速 SPI

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 555 )

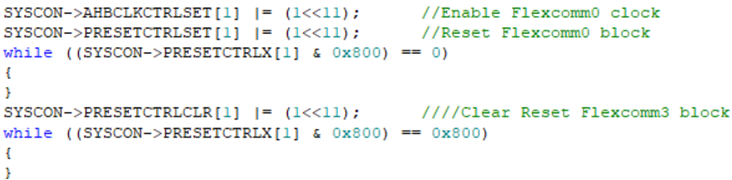

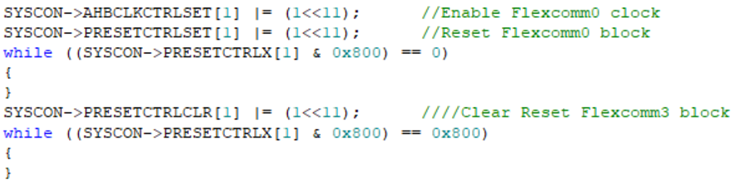

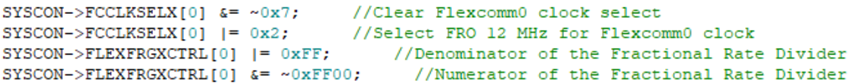

- SPI 設定範例

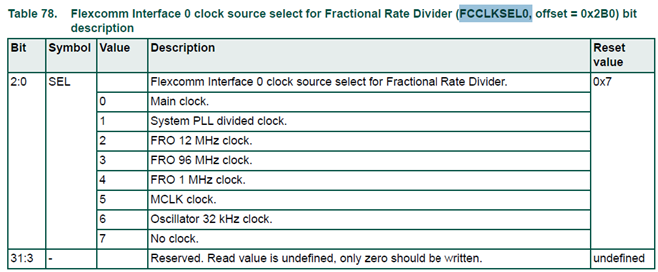

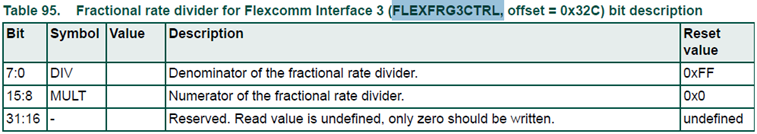

2. 設定 System control,由 FCCLKSEL 暫存器將 FC clock 來源設為 FRO 12 MHz。設置 FRG 除頻器為 1 使 FCCLK 為 12 MHz

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 66 )

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 73 )

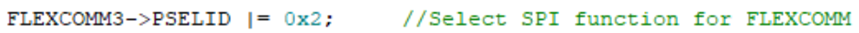

3. Flexcomm 功能選擇 SPI

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 557 )

4. 設置 SPI 為 MSB 先發送的 Master 且為 mode 0 ( CPHA = 0, CPOL = 0 )

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 624 )

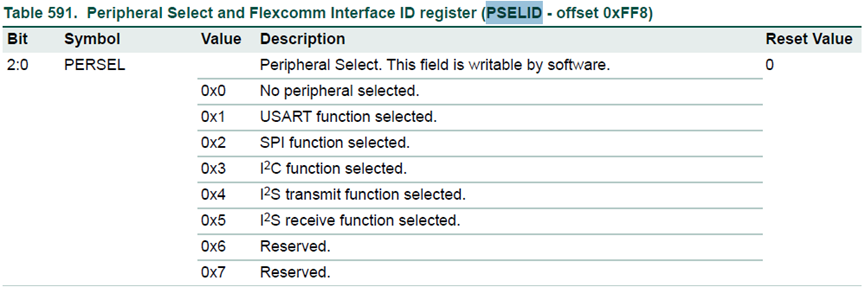

5. 設定 SPI 的 SCLK clock

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 627 )

6. 設定 FIFO,將 TXFIFO 和 RXFIFO 功能開啟,並將 TXFIFO , RXFIFO , TXFIFO error , RXFIFO error 清空

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 628 )

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 629 )

7. 設置 CFG 將 SPI 功能開啟

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 624 )

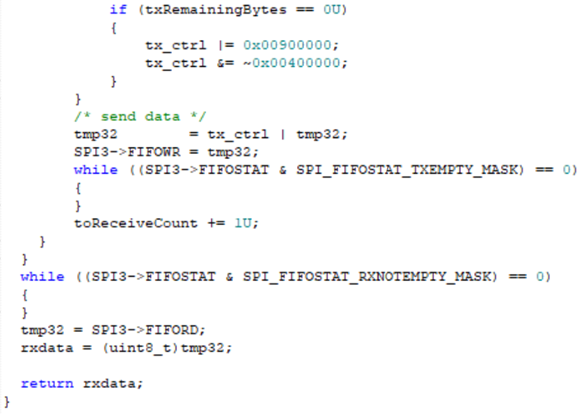

- SPI 寫入範例

2. 搭配 tx_ctrl 的操作來設置 FIFOWR,此以 0x070E 0000 為例,對 SS 0 的從機發送 7 bits data length 的數據

( 發送最後一筆資料則需再加 EOT 指令來結束 SPI )。最後將 tmp32 寫入 FIFOWR 發送出去

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 633 )

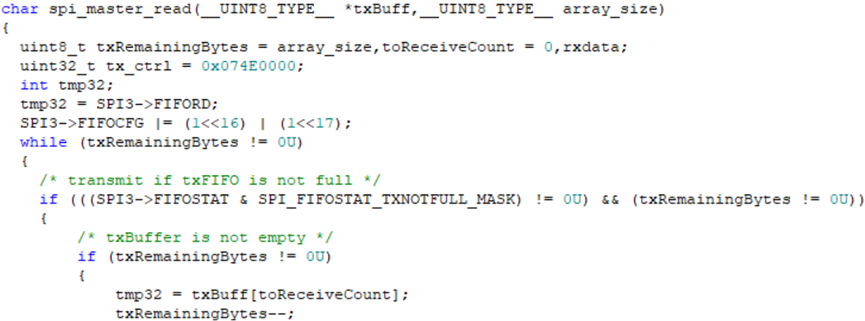

- SPI 讀取範例 ( 此為第三筆才將資料做讀取 )

2. 讀取函式會帶入 2 個參數,分別是 txbuffer , array size

首先把 FIFORD 的數據讀取出來。再將 TXFIFO 和 RXFIFO 清空,如同寫入步驟,此時 TXFIFO 判斷未滿,則將傳送的第一筆資料放入 tmp32

3. 搭配 tx_ctrl 的操作來設置 FIFOWR,此以 0x070E 0000 為例,對 SS 0 的從機發送 7 bits data length 的數據( 發送最後一筆資料則需再加 EOT 指令來結束 SPI )。

最後將 tmp32 寫入 FIFOWR 發送出去。由於全雙功,因此 FIFORD 會接收到從機傳送的數據,將 FIFORD 數據讀取出來後回傳

* NXP LPC55S0x/LPC550x user maunal ( UM11424.pdf page 633 )

- SPI 讀寫實測示波器波形

* 註一 : 圖片來源 NXP LPC55S0x/LPC550x User manual ( UM11424.pdf )