1.1 CapSense功能

PSoC 4和PSoC 6 MCU中的CapSense具有以下特性:

支持自電容和互電容觸摸感應

功能強大的CapSense Sigma Delta(CSD)和CapSense Crosspoint(CSX)感應技術,能夠為基於自電容和互電容的觸摸感應提供一流的信噪比。

在覆蓋材料和厚度不同的條件下仍能提供高性能感應(請參考CapSense基本原理、覆蓋層材料和覆蓋層厚度)

SmartSense™自動調試技術

接近感應的範圍較大(接近感應距離可達30 cm)

防水功能(請參見防水功能)

偽隨機序列(PRS)時鐘源可降低電磁干擾(EMI)

功耗較低:工作電壓低至1.71 V,休眠模式下的電流消耗低至150 nA

所有GPIO引腳都支持電容式感應和屏蔽1

允許將CapSense模塊重新配置為ADC,並且所有GPIO引腳都支持ADC輸入1

通過使用可編程參考電壓(VREF),可提供優越的信噪比

支持用於降低電磁干擾(EMI)的擴頻和可編程電阻開關

在CapSense掃描過程中,通過將初始化和配置過程分擔給CapSense序列發生器,可降低CPU開銷。

與PSoC 4100S器件相比,PSoC 4100S Plus器件具有以下附加功能:

提供更大的閃存存儲器和更多的I/O

提供一個控制區域網絡(CAN)模塊

為加密應用提供用於安全密鑰生成的真隨機數

接受4至33 MHz頻率範圍的外部晶振(ECO)

1.2 PSoC 4和PSoC 6 MCU CapSense Plus特性

您可創建帶有電容式觸摸感應和其他系統功能的PSoC 4 CapSense Plus應用。 除了CapSense外,這些器件還有以下關鍵特性:

帶單周期乘法的ARM® Cortex®-M0/M0+CPU,其工作頻率為48 MHz,並且它的指令執行速度高達43 DMIPS

在環境溫度範圍為–40至85 °C中,工作電壓範圍為1.71 ~ 5.5 V

高達128 KB的閃存空間(CM0+的代碼容量超過了採用8位解決方案的晶片的代碼容量兩倍)

高達16 KB的SRAM

多達94個可編程GPIO

獨立的中心對齊PWM,其特點包括互補死區可編程輸出、已被同步化的ADC操作(在PWM周期中用戶可指定的時間內觸發ADC的能力)和同步刷新(在所有的PWM上對PWM占空比變化進行同步化操作,以避免發生異常波形)

基於比較器的PWM停止(Kill)信號觸發(以便在檢測到過電流條件時終止電機驅動)

PSoC 4和PSoC 6 MCU中的CapSense具有以下特性:

支持自電容和互電容觸摸感應

功能強大的CapSense Sigma Delta(CSD)和CapSense Crosspoint(CSX)感應技術,能夠為基於自電容和互電容的觸摸感應提供一流的信噪比。

在覆蓋材料和厚度不同的條件下仍能提供高性能感應(請參考CapSense基本原理、覆蓋層材料和覆蓋層厚度)

SmartSense™自動調試技術

接近感應的範圍較大(接近感應距離可達30 cm)

防水功能(請參見防水功能)

偽隨機序列(PRS)時鐘源可降低電磁干擾(EMI)

功耗較低:工作電壓低至1.71 V,休眠模式下的電流消耗低至150 nA

所有GPIO引腳都支持電容式感應和屏蔽1

允許將CapSense模塊重新配置為ADC,並且所有GPIO引腳都支持ADC輸入1

通過使用可編程參考電壓(VREF),可提供優越的信噪比

支持用於降低電磁干擾(EMI)的擴頻和可編程電阻開關

在CapSense掃描過程中,通過將初始化和配置過程分擔給CapSense序列發生器,可降低CPU開銷。

與PSoC 4100S器件相比,PSoC 4100S Plus器件具有以下附加功能:

提供更大的閃存存儲器和更多的I/O

提供一個控制區域網絡(CAN)模塊

為加密應用提供用於安全密鑰生成的真隨機數

接受4至33 MHz頻率範圍的外部晶振(ECO)

1.2 PSoC 4和PSoC 6 MCU CapSense Plus特性

您可創建帶有電容式觸摸感應和其他系統功能的PSoC 4 CapSense Plus應用。 除了CapSense外,這些器件還有以下關鍵特性:

帶單周期乘法的ARM® Cortex®-M0/M0+CPU,其工作頻率為48 MHz,並且它的指令執行速度高達43 DMIPS

在環境溫度範圍為–40至85 °C中,工作電壓範圍為1.71 ~ 5.5 V

高達128 KB的閃存空間(CM0+的代碼容量超過了採用8位解決方案的晶片的代碼容量兩倍)

高達16 KB的SRAM

多達94個可編程GPIO

獨立的中心對齊PWM,其特點包括互補死區可編程輸出、已被同步化的ADC操作(在PWM周期中用戶可指定的時間內觸發ADC的能力)和同步刷新(在所有的PWM上對PWM占空比變化進行同步化操作,以避免發生異常波形)

基於比較器的PWM停止(Kill)信號觸發(以便在檢測到過電流條件時終止電機驅動)

12位的1 Msps ADC,具有“採樣和保持”(S&H)功能,且無需序列開銷,因而,可將整個ADC帶寬使用於信號轉換,而無需將其用於定序器開銷

具有比較器模式和SAR輸入緩衝能力的運算放大器

Segment LCD直接驅動器支持4個共用引腳

T/I2C串行通信通道

藍牙低功耗(BLE)通信與版本4.0和版本4.1的多項特性相兼容。

可編程的邏輯模塊,每個模塊包括八個宏單元和一個可級聯的數據路徑(即為通用數字模塊(UDB)),用於有效地執行可編程外設(如I2S)

控制器區域網絡(CAN)

全面支持PSoC Creator設計入口、開發和調試環境,從而提供:

設計入口和構建(了解模擬路由)

用於所有的固定功能外設和通用的可編程外設的組件

文檔和培訓模塊

支持將編譯內容導入到MDK ARM環境(前面將其稱為RealView)和其他環境內。

除了CapSense外,PSoC 6 MCU器件還有以下主要特性:

單CPU器件(Arm Cortex-M4),雙CPU器件(Cortex-M4 and Cortex-M0+)。硬體中支持處理器間的通信

在1.71 V ~ 3.6 V的器件工作電壓範圍內,用戶可以選擇1.1 V或0.9 V的內核邏輯操作

高達2 MB的閃存存儲器以及高達1 MB的SRAM

多達78個GPIO,可用於模擬、數字、CapSense或segment LCD功能

可編程模擬模塊:兩個運算放大器、可配置PGA、比較器、12位SAR ADC(1 Msps)、12位電壓模式DAC

可編程數字模塊、通信接口

12個UDB、32個TCPWM,可配置為16位/32位定時器、計數器、PWM或正交解碼器

九個串行通信模塊(SCB),可配置為I2C、SPI或UART接口

具有一個I2S接口和兩個PDM通道的音頻系統

SMIF接口,支持從外部四路SPI閃存實現的晶片內執行(XIP)以及動態加密和解密。

符合BLE 5.0規範的藍牙智能連接(僅適用於BLE器件系列的PSoC 6 MCU)

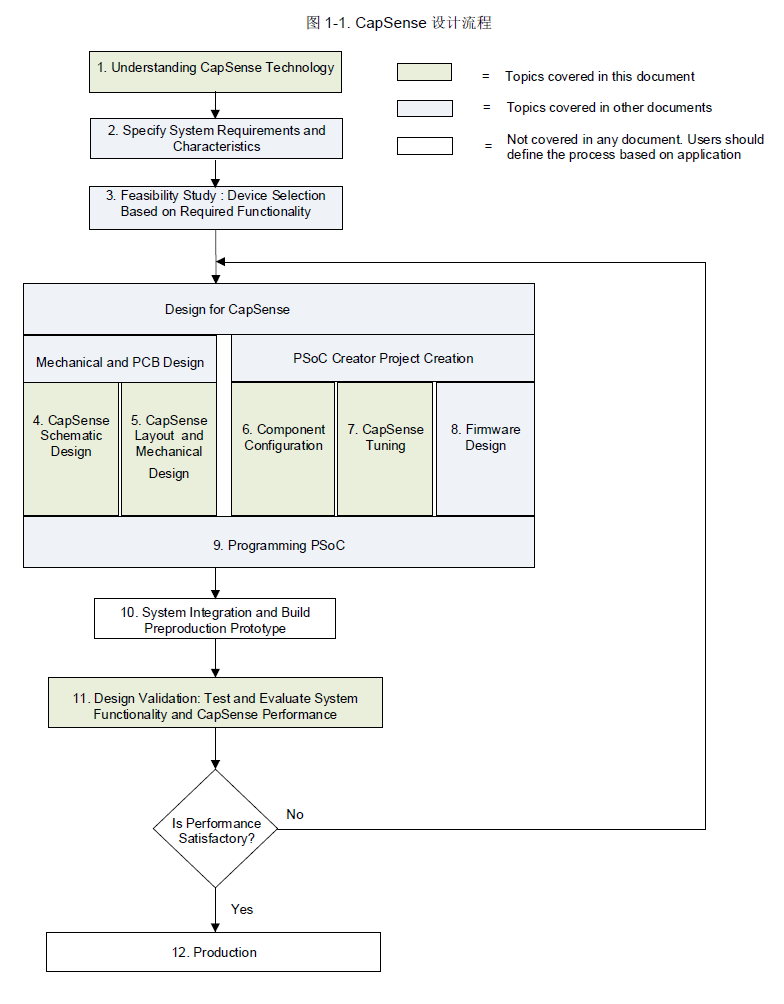

1.3 CapSense 設計流程

圖1-1 顯示的是典型的電容式感應產品的設計周期流程;本指南中提供的內容以綠色高亮顯示。

評論