-

LPC55S0x / LPC550x 支持 2 個外部和 3 個內部時鐘源:

- 內部自由運行振盪器(FRO)。FRO 提供可選擇的 96 MHz 輸出和可用作系統時鐘的 12 MHz 輸出。

- 32 KHz 內部自由運行振盪器 FRO。

- 內部低功耗振盪器(FRO 1 MHz)。

- 外部時鐘輸入支持工作頻率為 1 MHz 至 25 MHz 的晶體振盪器。

- 工作頻率為 32.768 KHz 的晶體振盪器。

-

PLL0 和 PLL1 允許以最大 CPU 速率運行,而無需高頻外部時鐘。

- PLL0 和 PLL1 可以從內部 FRO 12 MHz 輸出、外部振盪器、內部 FRO 1 MHz 輸出或 32.768 kHz RTC 振盪器運行。

- 系統 PLL 接受 2 kHz - 150 MHz 範圍內的輸入時鐘頻率。

- 輸入頻率通過電流控制振盪器 ( CCO ) 倍增至高頻。

-

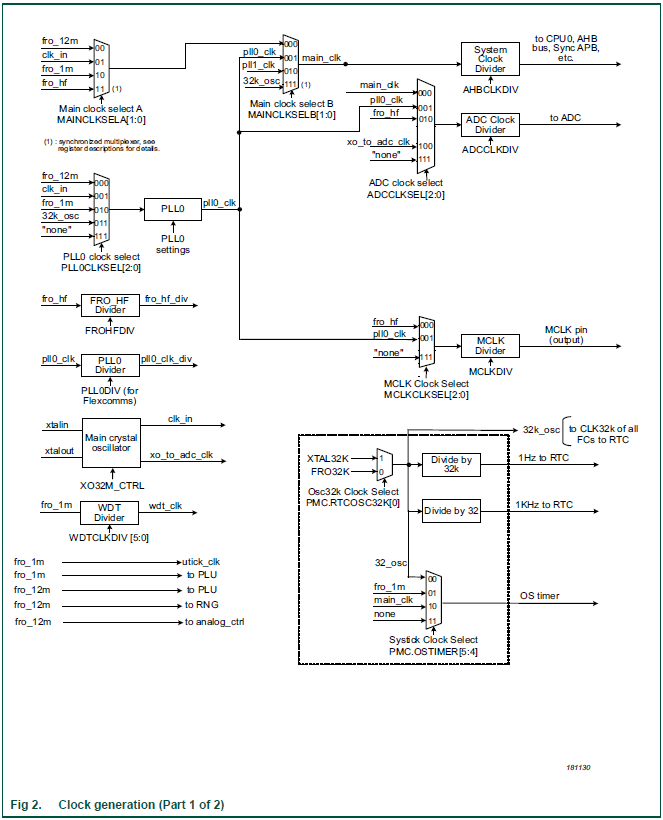

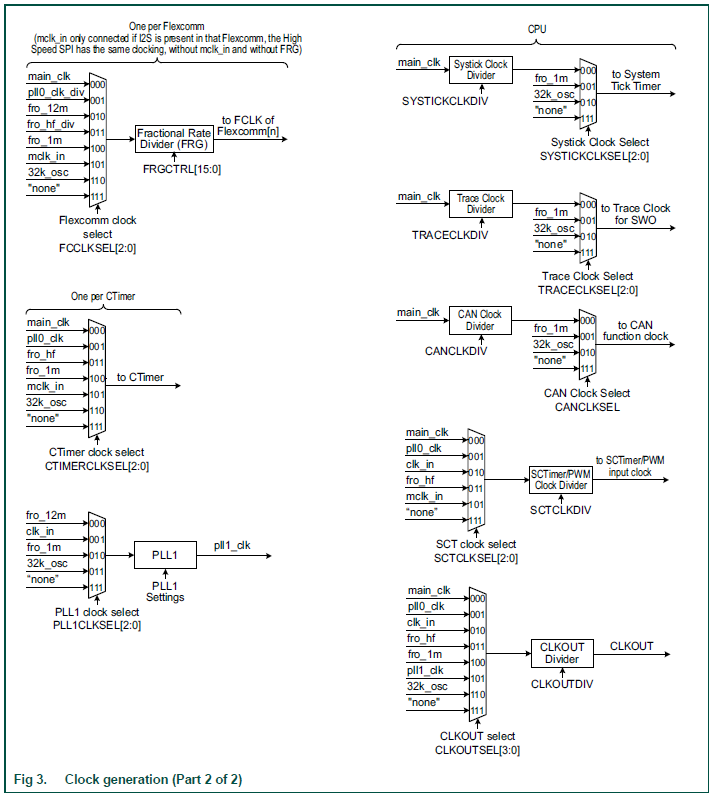

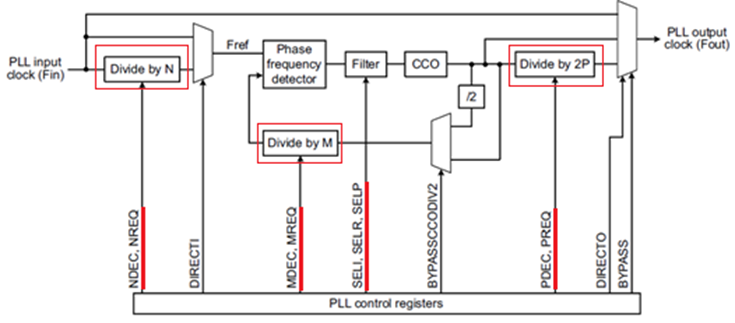

Black diagram

( 圖一 )

( 圖二 )

-

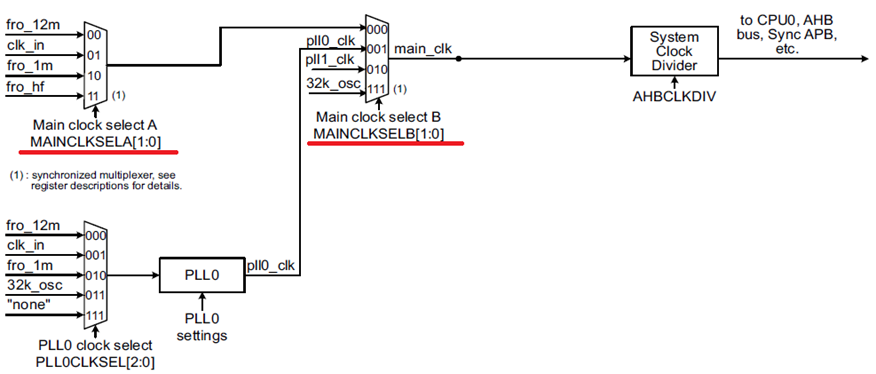

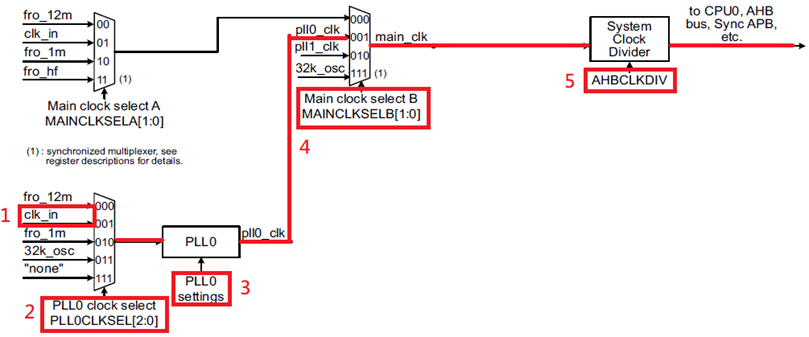

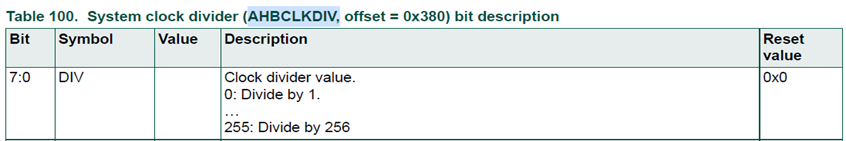

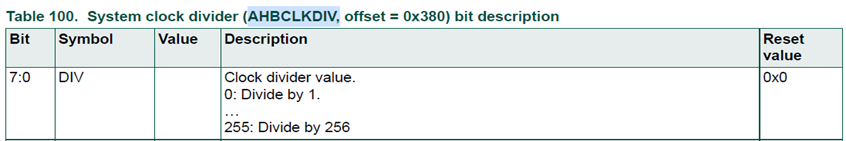

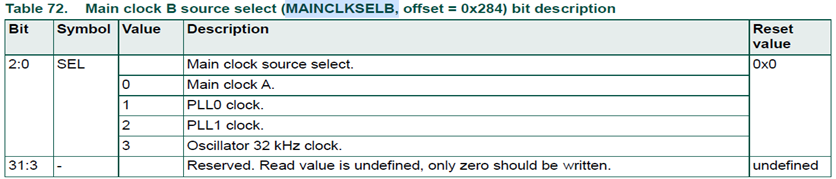

參考上方圖一,擷取出下方圖三,可設置 MAINCLKSELA 和 MAINCLKSELB 來選擇 main_clk,經 AHBCLKDIV 除頻後可得 system clock。system clock 最大工作頻率為 96MHz。

( 圖三 )

-

PLL ( PHASE-LOCKED LOOP,中文稱鎖相環 )

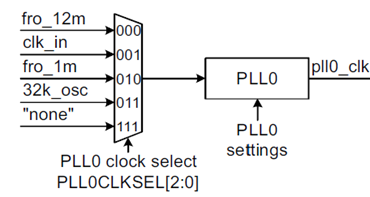

( 圖四 )

( 圖五 )

- 如圖四,PLL0 和 PLL1 可以從內部 FRO 12 MHz 輸出、內部 FRO 1 MHz 輸出、32.768 KHz RTC 振盪器或外部振盪器運行

- 透過圖五的 PLL 架構,由 Phase frequency detector ( 相位頻率檢測器 ),將除頻後的 CCO 輸出與輸入進行比較。再把其誤差值輸出至過濾器濾掉不需要的頻段訊號,並於 CCO 調整輸出頻率。

- PLL 輸入範圍為:2 KHz 至 150 MHz

- 電流控制振盪器 ( CCO ) 頻率範圍為:275 MHz - 550 MHz。

- 預除頻器 N ( 1 to 28-1 )、反饋除頻器 M ( 1 to 216-1 )、後除頻器 P*2 ( 1 to 25-1 )

- PLL 輸入最初會被 N 除頻。之後是 PLL 乘法器,乘法器是通過使用電流控制振盪器 ( CCO ) 將輸入除頻器輸出乘以值 M。PLL 輸出可以進一步除以值 2P。

- 軟件應使用 6 ms 的時間間隔來確保 PLL 穩定。

- Fout = Fcco/2*P = Fin*M/( N*2*P )

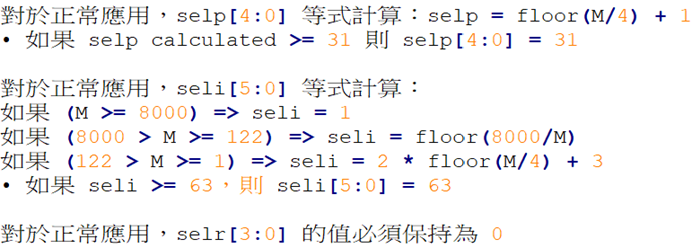

- Bandwidth 的 R、I、P 計算

( 圖六 )

-

使用外部 16MHz 震盪器經 PLL0 倍頻出 96MHz 作為工作頻率的程式範例

( 圖七 )

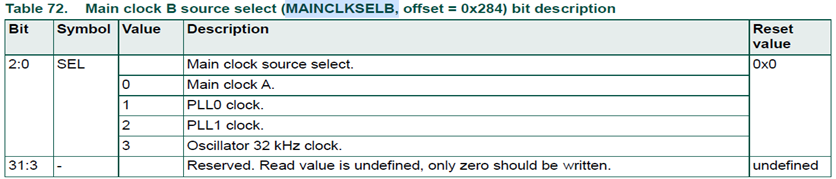

- 如圖七,設置流程:將 PLL0CLKSEL 選擇 clk_in 外部震盪器為 PLL 輸入源,設置 PLL0 暫存器參數後可得 pll0_clk,再設置 MAINCLKSELB 選擇 pll_clk 為 main_clk 輸入源,再設置 AHBCLKDIV 後可得 system clock

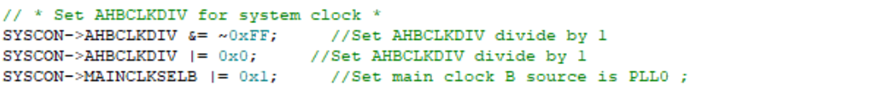

- 程式範例:

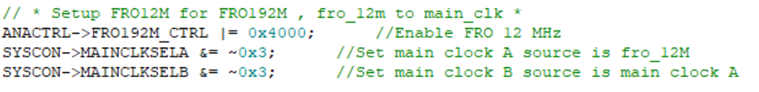

- 確認 Analog control 將 FRO 192MHz 暫存器中的內部 FRO 12 MHz 震盪器開啟,並透過 MAINCLKSELA & MAINCLKSELB 產生 main clock & system clock

( 圖八 )

-

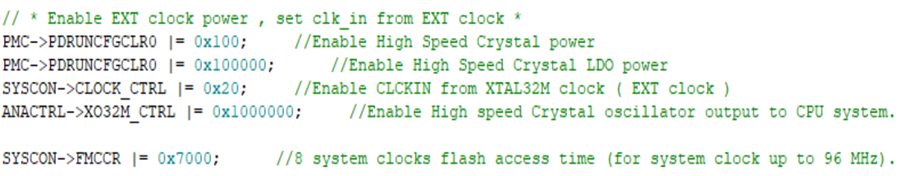

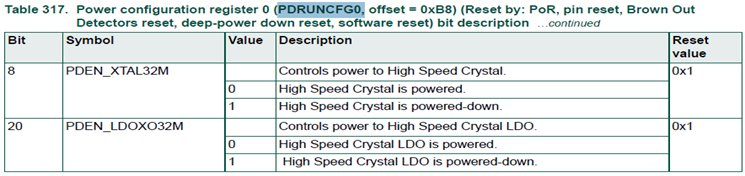

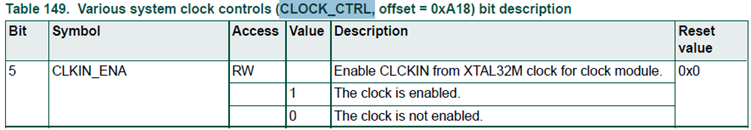

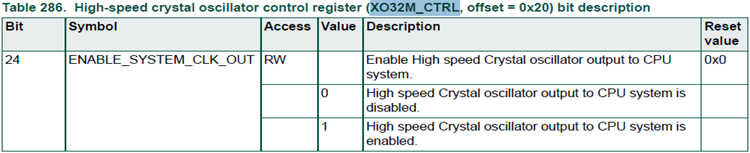

- 設定 Power manger control,將外部震盪器模塊電源開啟,再使外部震盪器的 clock 連接到 CLKIN & CPU。同時設定 flash 拜訪時間。

( 圖九 )

( 圖十 )

( 圖十一 )

( 圖十二 )

-

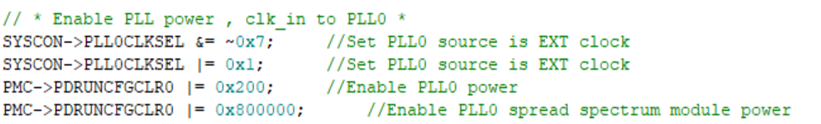

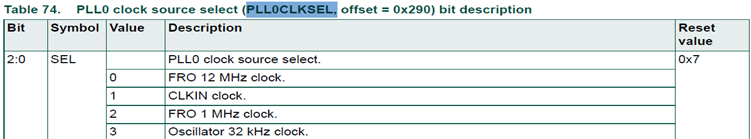

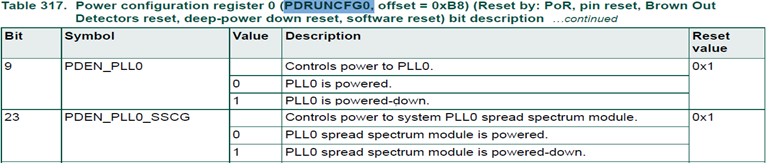

- 設定 System control,將 PLL0 clock 來源設為外部 16 MHz 震盪器。設定 Power manger control 將 PLL0 模塊電源開啟

( 圖十三 )

( 圖十四 )

( 圖十五 )

-

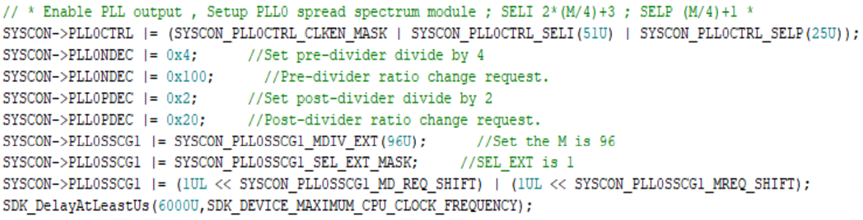

- 設定 System control 的 PLL0 & PLL0SSCG1 暫存器,啟動 PLL0 模塊。經計算 : SELI is 51 , SELP is 25 , N is 4 , P is 2,將上述計算值代入 PLL0 相關暫存器。設置 6 ms 的時間間隔來確保 PLL0 穩定

( 圖十六 )

-

- 設置 AHBCLKDIV 為 0 的除頻而產生 System clock。由 MAINCLKSELB 將 main clock 來源設為 PLL0 clock 的 96 MHz,使 System clock 為 96 MHz

( 圖十七 )

( 圖十八 )

( 圖十九 )

-

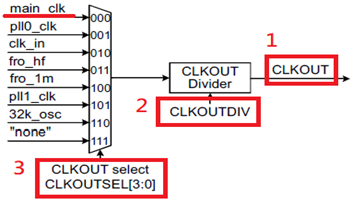

將 System clock 透過 CLKOUT 輸出

( 圖二十 )

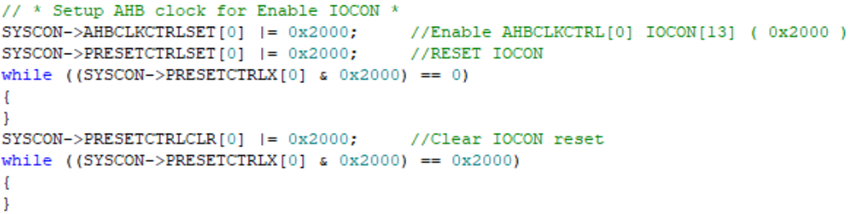

- 設定 System control,透過 AHBCLKCTRL 啟動 IOCON 模塊的 clock,並透過 PRESETCTRL 將其模塊重置

( 圖二十一 )

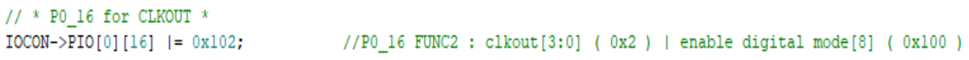

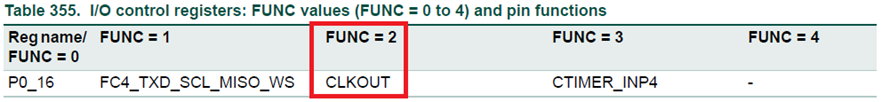

- 設定 IOCON,將 P0_16 腳位功能設為 CLKOUT 且為 digital mode

( 圖二十二 )

( 圖二十三 )

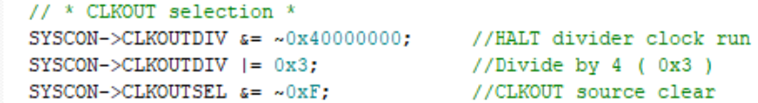

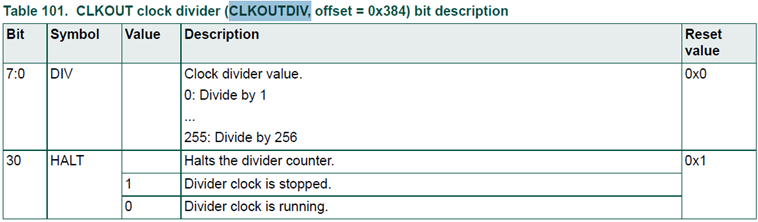

- 設置 System control,啟用 CLKOUTDIV 並將其設為 3,使 CLKOUT 除 4 後做輸出。再設置 CLKOUTSEL 選擇來源 clock

( 圖二十四 )

( 圖二十五 )

- 使用示波器量測 CLKOUT 腳位,可得到 24MHz 輸出波形。將其反算便是 96MHz 的main_clk 主頻率

( 圖二十六 )

參考資料

LPC55S0x/LPC550x Preliminary data sheet (nxp.com)

LPC55S0x/LPC550x User manual (nxp.com)

評論