這篇微信文章,其實構思已久。為了有所鋪墊,已在2020和2021發布了兩篇基礎篇:

2022,讓我們再次聊聊在SiC單管並聯中的寄生導通問題。

特別提醒:仿真只是工具,仿真無法替代實驗,仿真只供參考。

在展開仿真的宏大序章之前,我們不妨先回顧之前的一些小結論:

▌ 2020《仿真世界之SIC單管的寄生導通現象》

► 機理澄清:寄生導通現象來自米勒電容和源極電感的綜合影響。

► 封裝影響:事物皆有兩面。TO247-3封裝內的功率源極電感也處於驅動迴路中,導致封裝內外Vgs波形差異容易引起誤判,同時增加了開關損耗,但是好處是降低了開關速度和di/dt,客觀上也削弱了源極電感對寄生導通的風險。TO247-4封裝的開爾文結構,解耦了功率迴路與驅動迴路的源極電感,封裝內外Vgs一致(表里如一),雖然減少了開關損耗,但是增加了開關速度和di/dt,這在客觀上也加劇了源極電感對寄生導通的風險。總的來說,TO247-4還是更優的選擇。

► 在TO247-4pin的SiC單管並聯的均流特性仿真中,主迴路的源極電感Lex,對器件均流的影響最為顯著,同時還會形成源極的環流。

► 由源極電感Lex引起的器件均流差異,用輔助源極電阻Rgee和門級電容Cgs去補救,其收效有限。因此,在SiC並聯布局初始,一定要儘可能保證源極電感Lex一致。

為了搞清楚SiC單管並聯中的寄生導通問題,我們將繼續通過仿真,層層深入:

► SiC單管並聯中的寄生導通與源極環流的關係

► 既然“源極環流擋不住”,我們又該何去何從?

01 選取仿真研究對象

SiC MOSFET: IMZ120R045M1(1200V/45mΩ)、

TO247-4pin、兩並聯

Driver IC:

1EDI40I12AF、單通道、磁隔離、

驅動電流±4A(min)

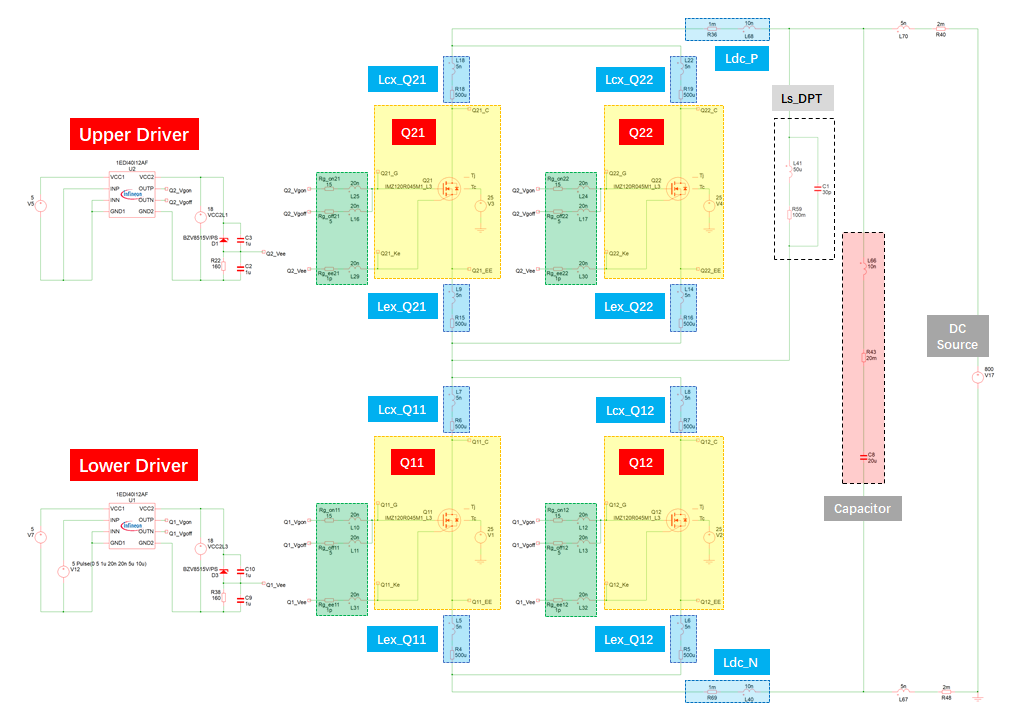

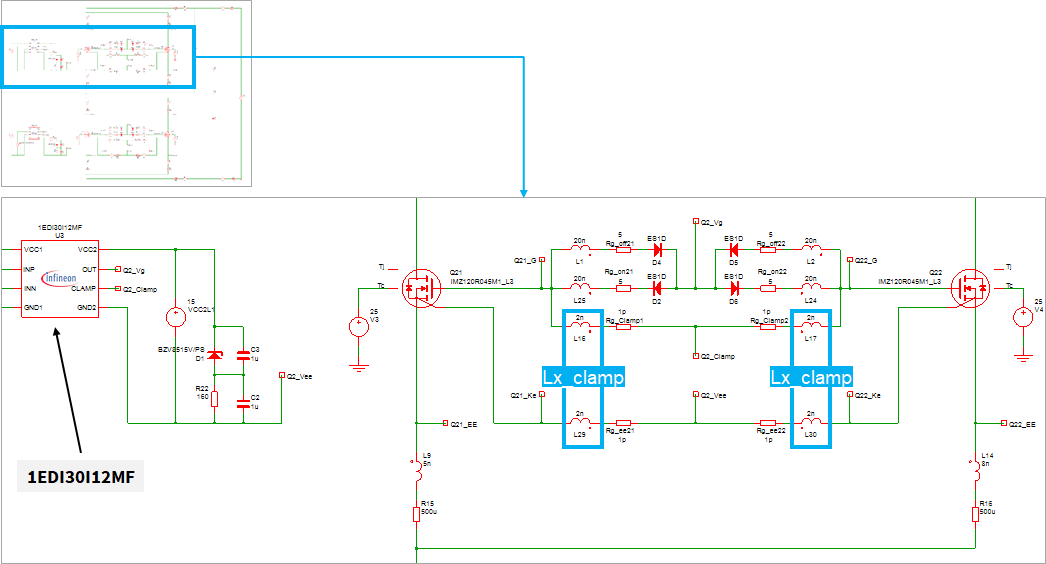

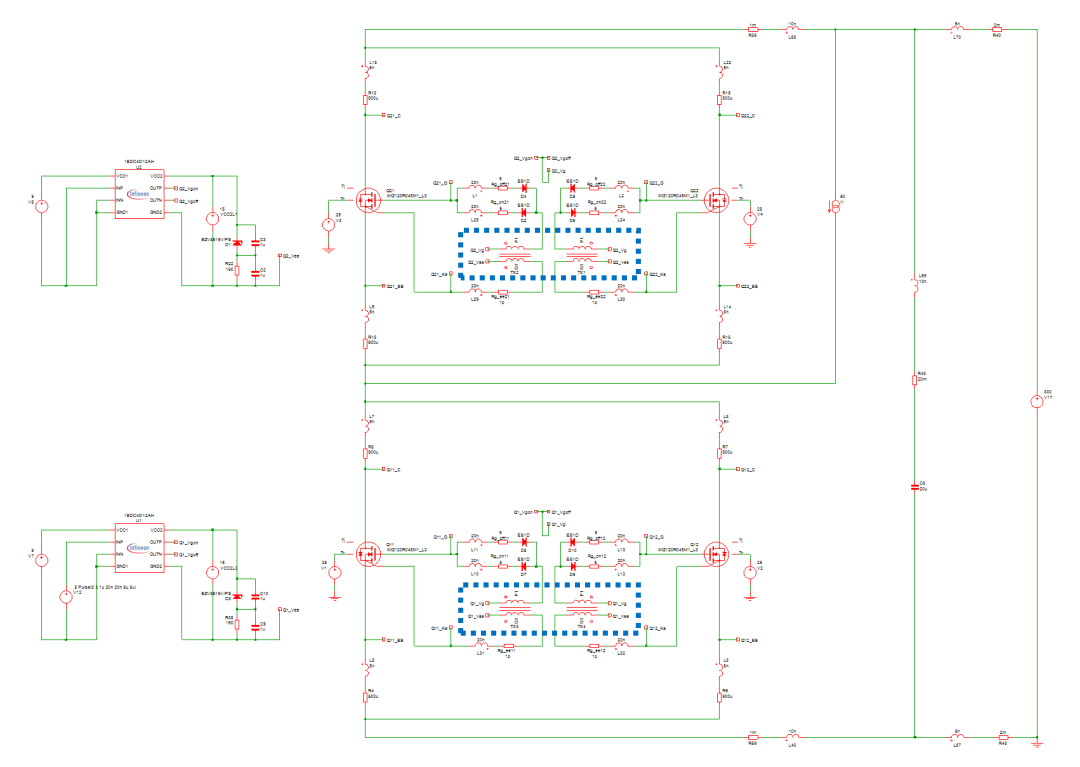

02 仿真電路Setup

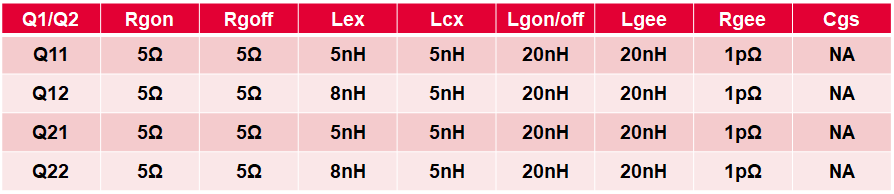

如圖1所示,基於雙脈衝的思路,搭建雙管並聯的主迴路和驅動迴路,並設置相關雜散參數,環境溫度為室溫。

1. 外部主迴路

直流源800Vdc、母線電容Capacitor(含寄生參數)、母線電容與半橋電路之間的雜散電感Ldc_P和Ldc_N、雙脈衝電感Ls_DPT

2. 並聯主迴路

整體為半橋結構,雙脈衝驅動下橋SiC MOSFET,與上橋的SiC MOSFET Body Diode進行換流。下橋為Q11和Q12兩顆IMZ120R045M1,經過各自發射極(源極)電感Lex_Q11和Lex_Q12,以及各自集電極(漏極)電感Lcx_Q11和Lcx_Q12並聯到一起;同理上橋的Q21和Q22的並聯結構也是類似連接。

3. 並聯驅動迴路

基於TO247-4pin的開爾文結構,功率發射極與信號發射級可彼此解耦,再加上1EDI40I12AF這顆驅動晶片已配備OUTP與OUTN管腳,所以,每個單管的驅動部分都有各自的Rgon、Rgoff和Rgee(輔助源極電阻),進行兩並聯後與驅動IC的副邊相應管腳連接。

4. 驅動部分設置

通過調整驅動IC副邊電源和穩壓電路,調整門級電壓Vgs=+15V和Vgs=0V~-3V,然後設置門極電阻Rgon、Rgoff,和輔助源極電阻Rgee默認設為0Ω(1pΩ),外加單管門極與驅動IC之間的PCB走線電感Lgon/Lgoff/Lgee等。

圖1.SiC MOSFET並聯(驅動一推二)的雙脈衝仿真Setup示意圖

03 SiC單管並聯中的寄生導通與源極環流的關係

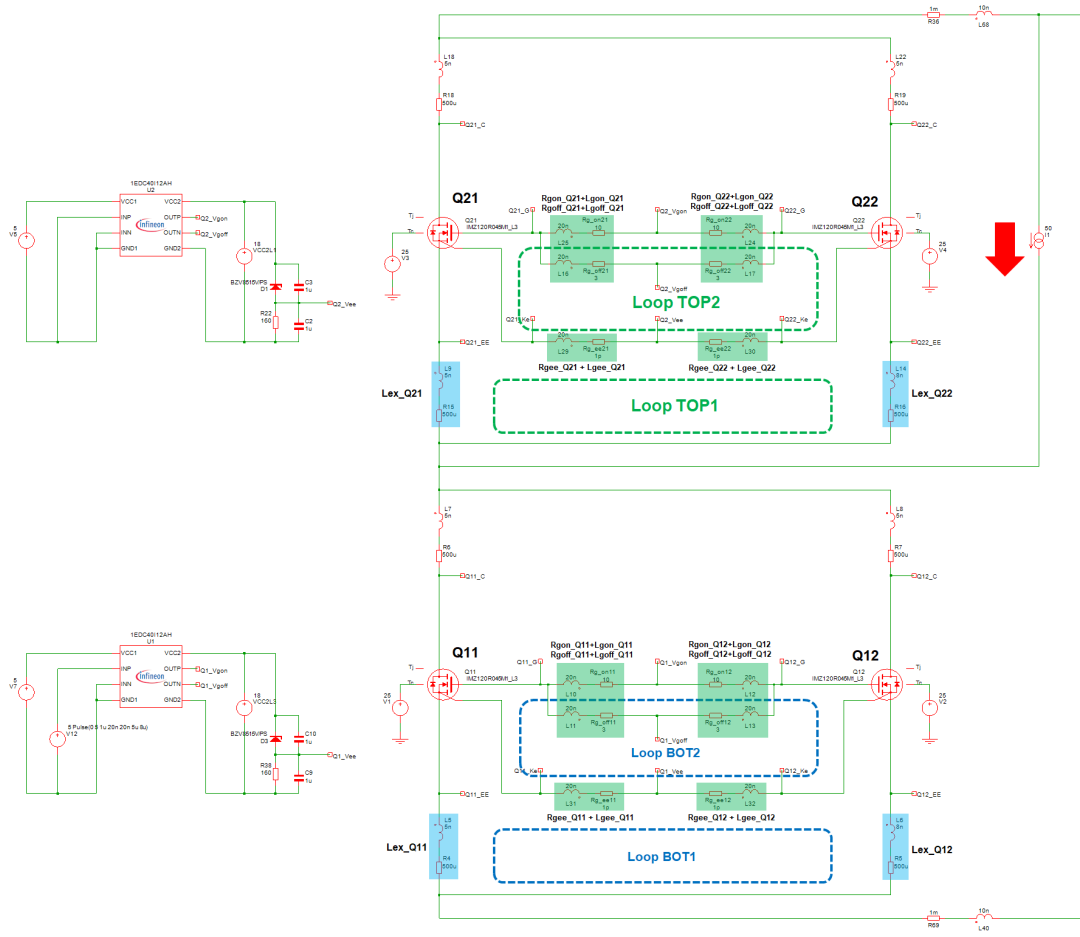

圖2.由圖1變換的並聯上管和下管的環路示意圖

具體過程,我們通過仿真舉例分析:[下管雙脈衝,上管關斷]

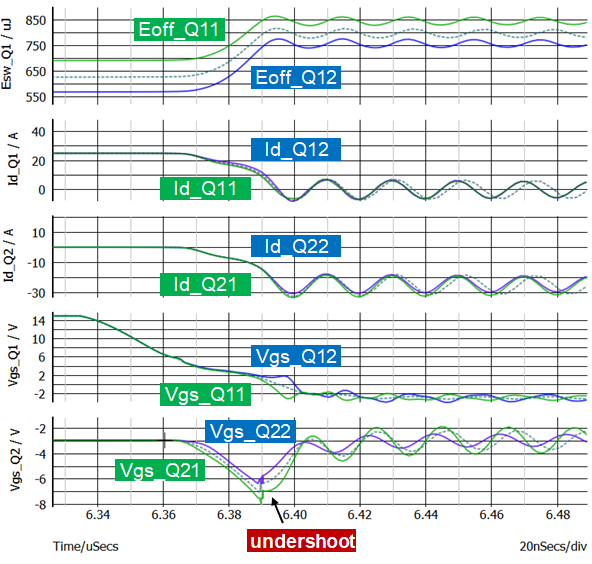

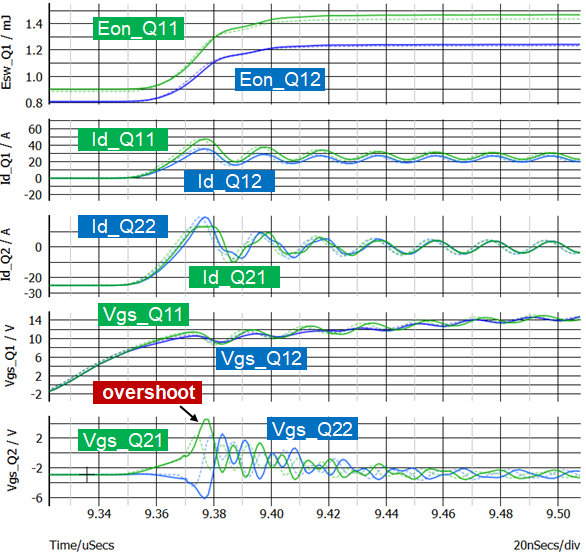

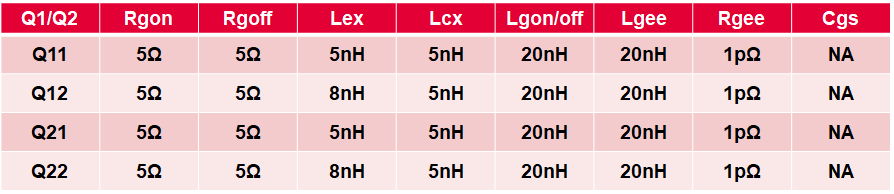

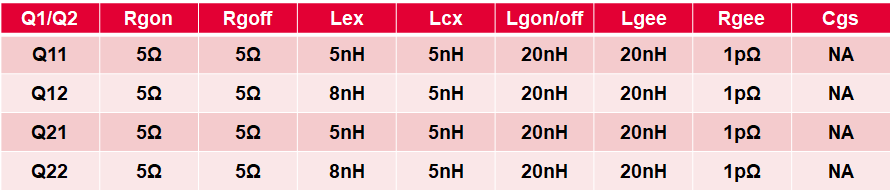

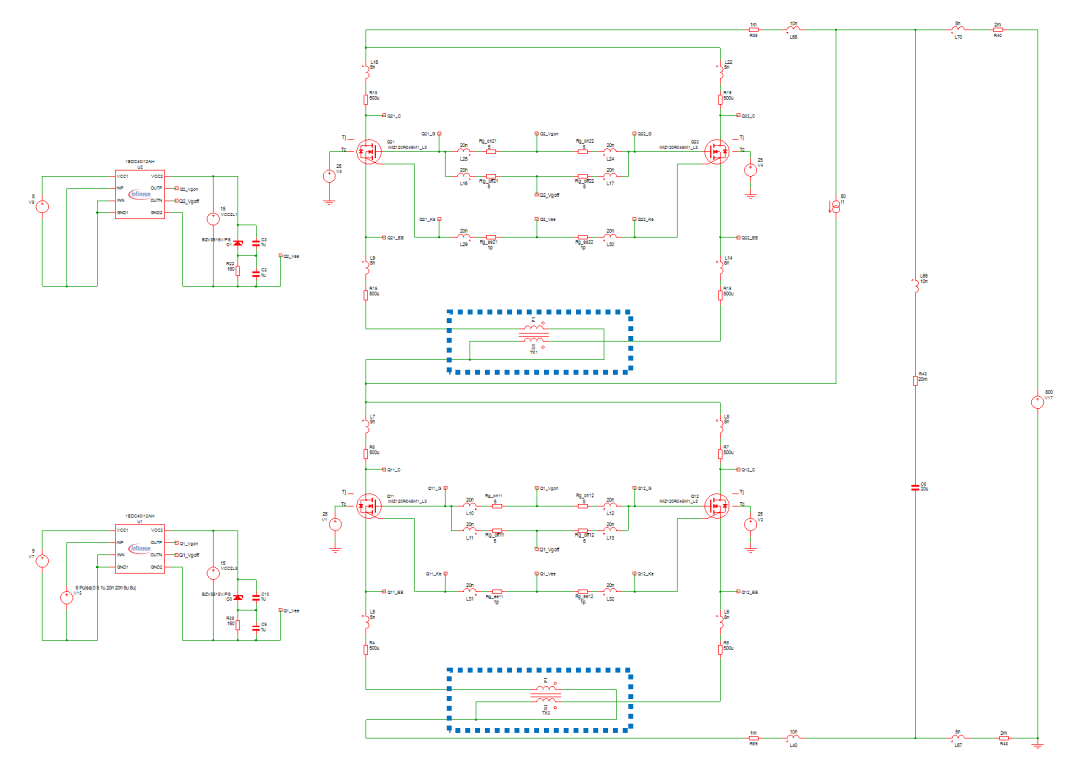

門級設置Vgs=+15V/-3V,Q1和Q2的並聯源極電感先設為8nH,然後再將Q11和Q21的Lex電感改為5nH,如圖3所示,製造並聯的源極電感Lex的差異,看開關波形的變化。

圖3.並聯仿真的電感與電阻設置

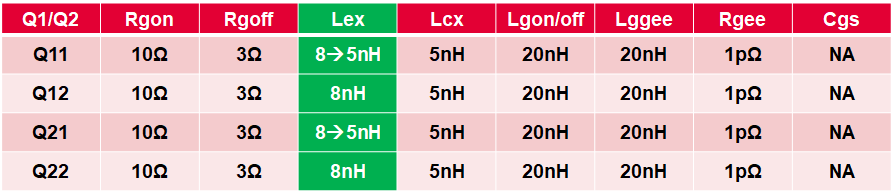

圖4.關斷過程仿真波形

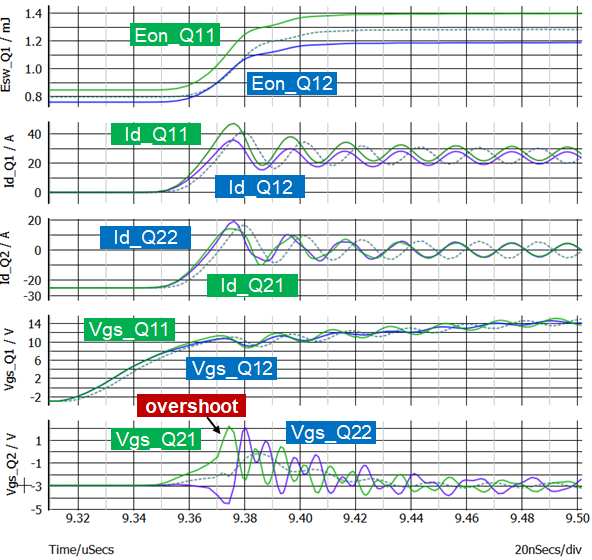

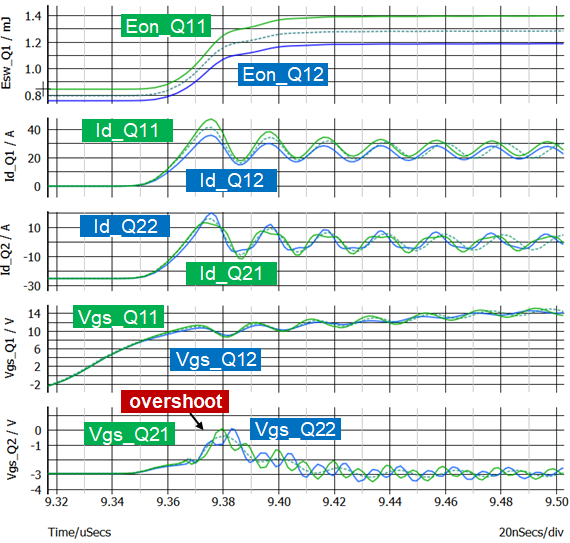

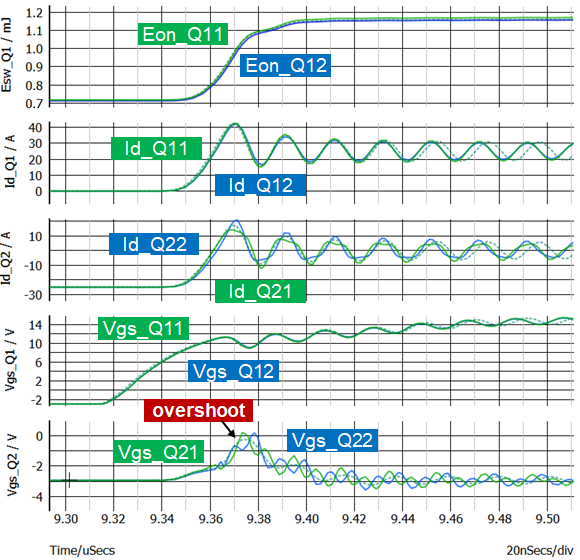

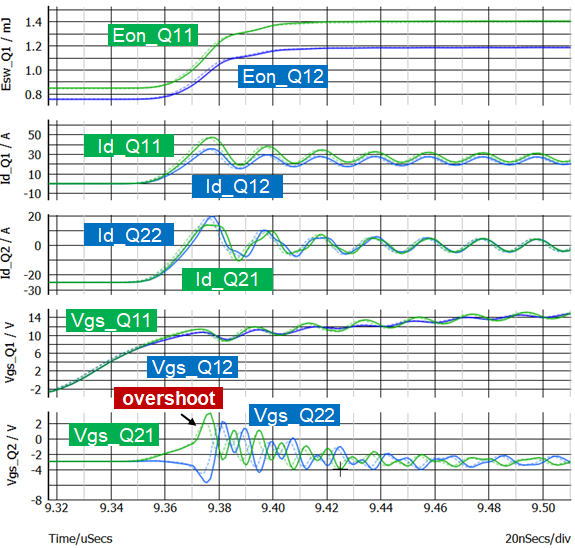

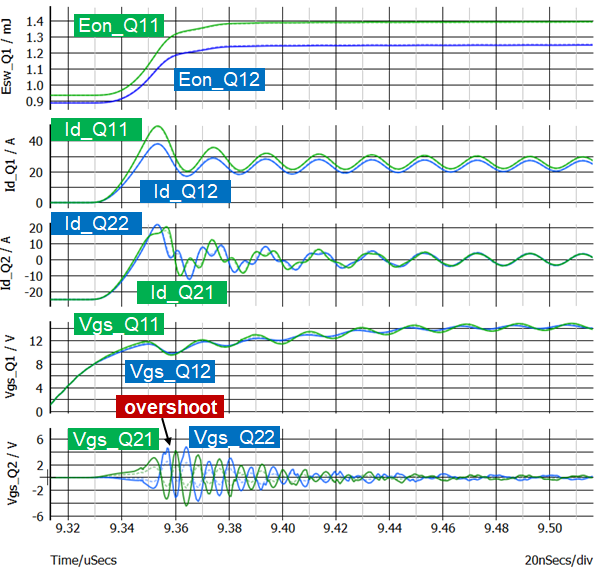

如圖4所示:關斷過程的仿真波形,虛線為並聯支路的源極電感Lex皆為8nH的波形,實線為並聯支路其中Q11和Q21的Lex=5nH後的波形。

圖5.開通過程仿真波形

如圖5所示:開通過程的仿真波形,虛線為並聯支路的源極電感Lex皆為8nH的波形,實線為並聯支路其中Q11和Q21的Lex=5nH後的波形。

由上述開關過程的仿真可知,源極電感除了對自身Q11/Q12的Id和Esw特性,還會顯著影響對管Q21/Q22 的Vgs電壓尖峰(undershoot和overshoot),尤其是overshoot的部分,如圖5所示,不僅將Q21/Q22的Vgs電壓尖峰抬高了2V,同時還引起了Vgs的持續振盪。

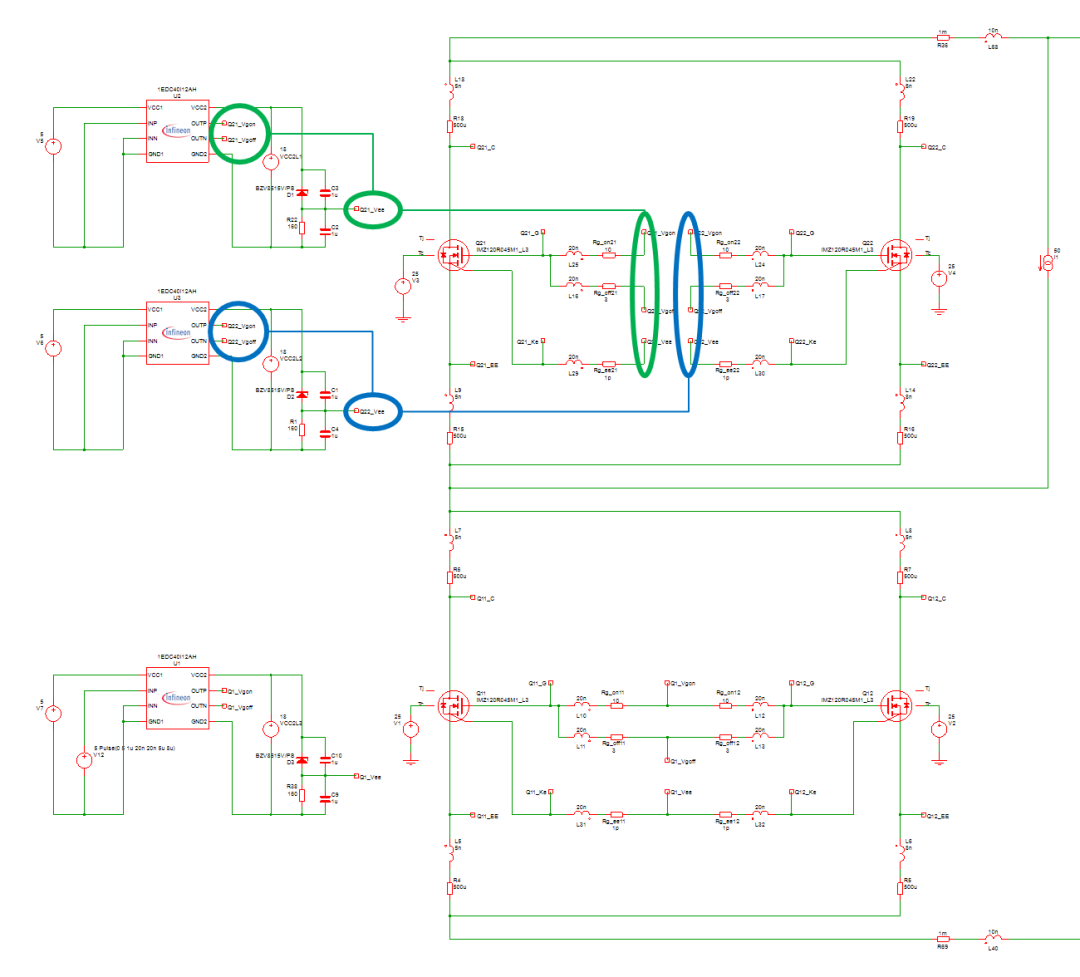

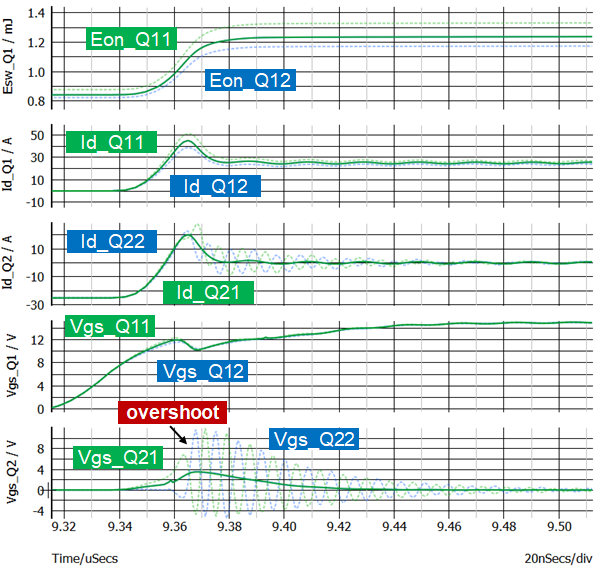

為了驗證源極環流對上述overshoot的惡劣影響,我們又增加了一組仿真,將上管並聯的驅動方式,由一驅二,改為單獨一驅一,下管維持不變,以此切斷上管並聯的環路,如圖6所示:

圖6.上管改為單獨一驅一的並聯驅動方式

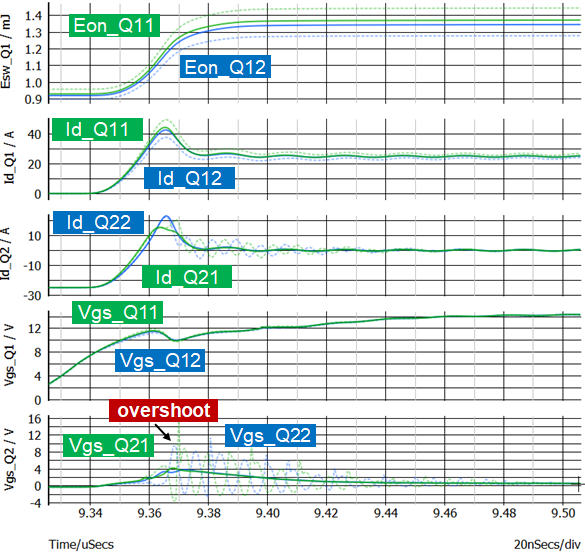

圖7.僅上管改為單獨一驅一的並聯驅動方式後的開通波形

圖7中,虛線為並聯支路的源極電感Lex皆為8nH的波形,實線為並聯支路其中Q11和Q21的Lex=5nH,且Q12和Q12的Lex=8nH的波形。源極電感Lex的差異,在獨立驅動的模式下,幾乎沒有抬高overshoot電壓尖峰。對比圖5和圖7,當切斷上管的源極環路之後,overshoot波形的尖峰和振盪都得到了明顯的改善。

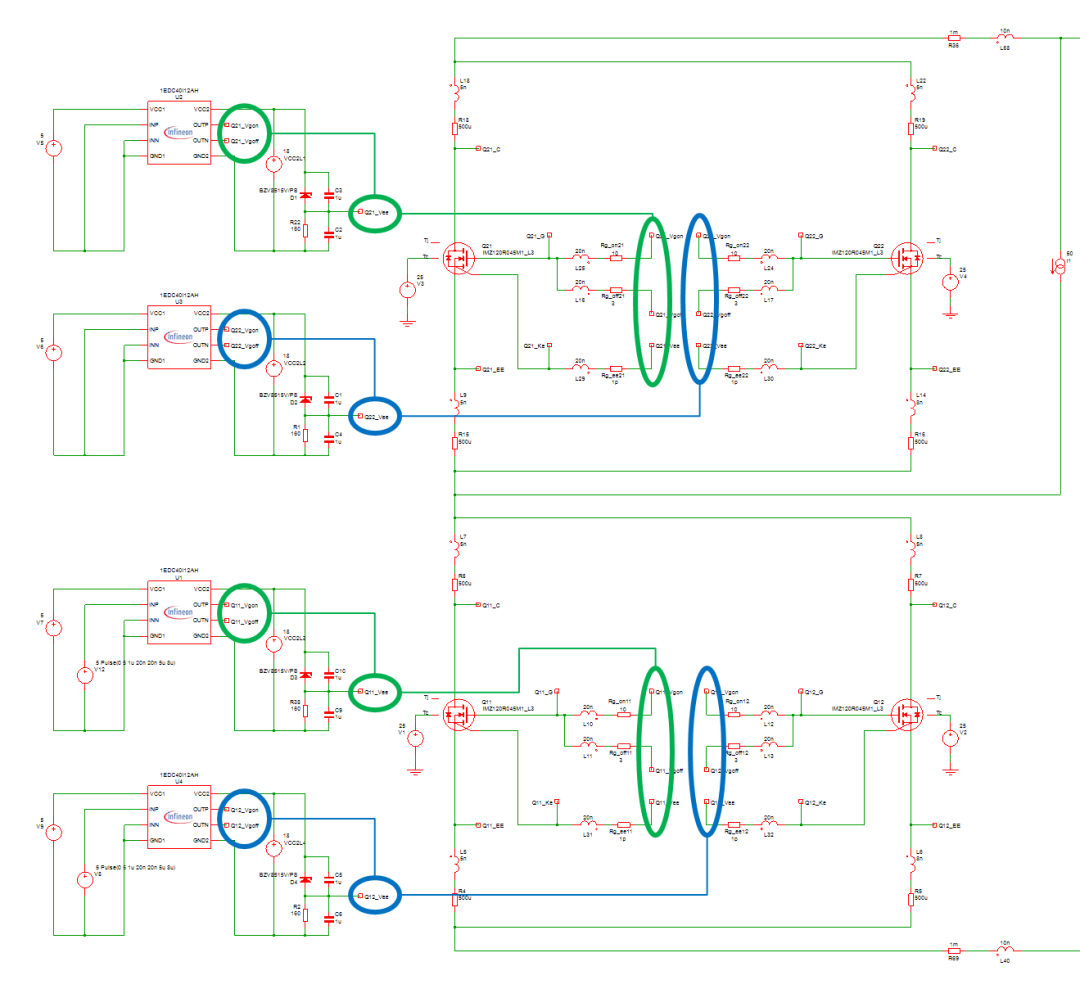

為了進一步對比說明,再補充一組上下管的並聯都改為單獨驅動的仿真與波形,如圖8和圖9所示:

圖8.上下管皆為單獨一驅一的並聯驅動方式

圖9 上下管皆為單獨一驅一的並聯驅動方式的開通波形

圖9中,虛線為並聯支路的源極電感Lex皆為8nH的波形,實線為並聯支路其中Q11和Q21的Lex=5nH,且Q12和Q12的Lex=8nH的波形。波形結論與圖7類似,由於下管也採用獨立的並聯驅動模式,下管的電流均流和損耗差異也得到了非常好的控制。

因此,綜合上述的仿真波形對比與分析可知:在SiC單管並聯時,由於並聯電路中源極迴路的存在,當源極電感Lex有差異時,就會引起形成源極環流,抬高overshoot電壓尖峰,進一步增加了Vgs寄生導通的風險。與此同時,該源極環流,也會對自身Vgs產生影響,進而影響電流Id的均流和損耗Esw的差異。

04 既然“源極環流擋不住”,我們又該何去何從?

由上可知,在SiC單管的並聯應用中,無論是均流還是寄生導通的惡化,都是源極迴路和環流“惹的禍”,尤其在普遍的一驅多的並聯方式下,幾乎“無處可逃”。那麼在實際應用中,既然“源極環流擋不住”,我們又該何去何從,將寄生導通風險降低呢?

策略1. 儘可能做到Lex電感的對稱

在並聯的PCB布局或母排設計時,儘可能做到器件外部源極電感的對稱性。對於複雜的多並聯Case,可利用有限元的工具(如Q3D)進行雜散電感提取以輔助優化設計。

策略2. 增加一些抑制與補救的措施

我們先通過仿真看下幾種常見措施的效果:

■ 採用單獨驅動模式

單獨驅動模式,相比一驅二的驅動方式,可以從根本上切斷源極環路,將源極環流與寄生導通徹底解耦(如圖8和圖9所示),但也存在一些不足:例如,多個驅動IC導致成本上升,不同驅動IC的輸出延遲時間差異導致驅動不同步等,尤其對於SiC這樣的高速器件,尤須謹慎。

■ 適當增加門級Cgs電容

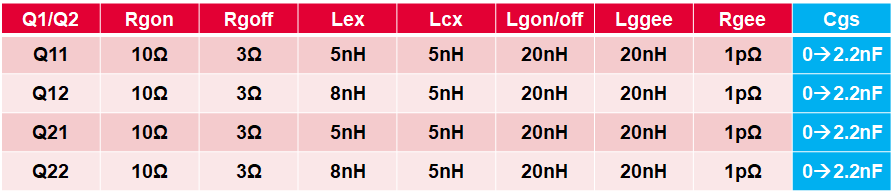

圖10.增加門級Cgs電容的仿真Setup參數設置

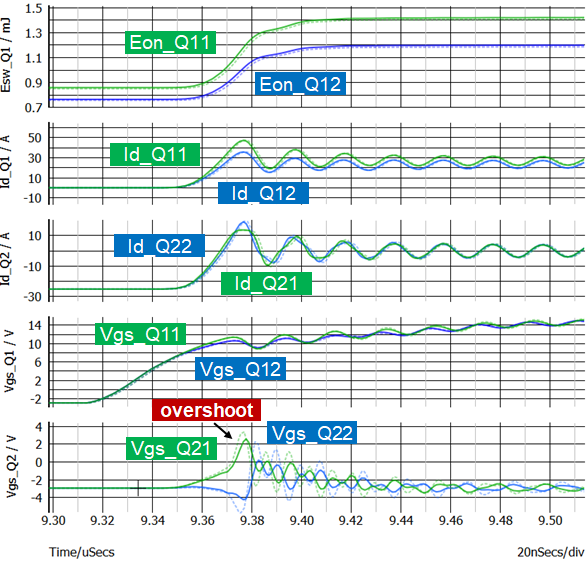

仿真Setup參數設置如圖10所示,令並聯Lex的差異為5nH和8nH,觀察增加門級Cgs電容前後的開通波形變化,如圖11所示:虛線為無Cgs電容,實線為有Cgs電容的開通波形。

圖11.門級增加2.2nF電容前後的開通波形對比

由上,可以看到Cgs以降低開通速度,增加Eon損耗為代價,將上管Vgs的overshoot電壓尖峰從2V降低到0V,同時也大幅降低了Vgs電壓振盪,對於寄生導通的抑制效果還是不錯的(但是對於Eon並聯差異的影響幾乎沒有)。

■ 合理搭配輔助源極電阻電感

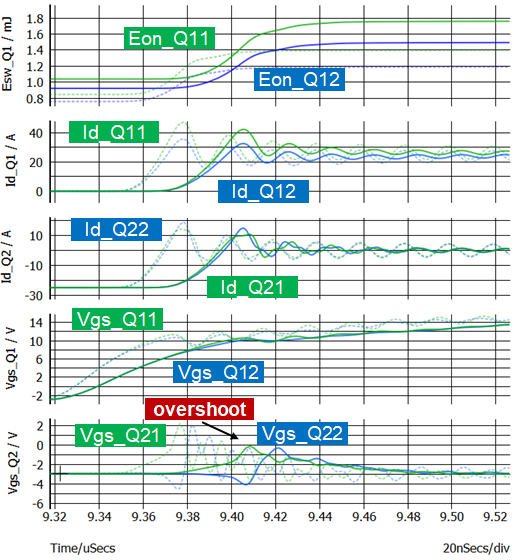

圖12.設置輔助源極電阻Rgee參數舉例1

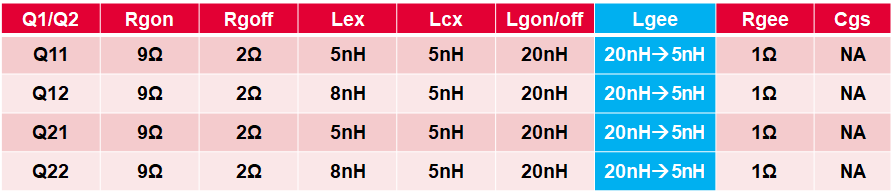

仿真Setup參數設置如圖12和14所示,令並聯Lex的差異為5nH和8nH,觀察配置了輔助源極電阻Rgee前後的開通波形變化。其中圖13:虛線為無Rgee,實線為有Rgee後的開通波形,輔助源極電阻Rgee反而推高了overshoot電壓;圖15為優化輔助源極電感Lgee前後的開通波形,虛線為Lgee=20nH,實線為Lgee=5nH,電感降低可以適當降低overshoot電壓尖峰。

圖13.增加輔助源極電阻前後的開通波形對比1

圖14.優化輔助源極電感Lgee參數舉例2

圖15.優化輔助源極電感Lgee參數前後的開通波形對比2

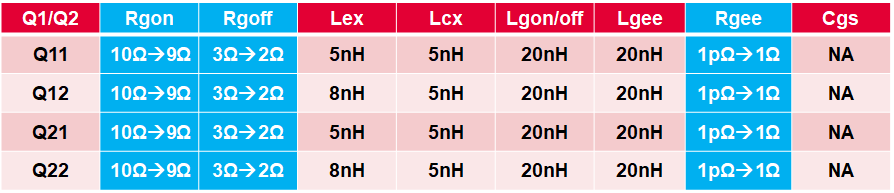

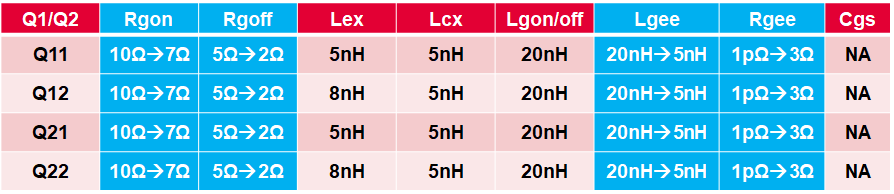

如果適當增加輔助源極電阻與門級電阻比例,效果如何呢?這裡又補充了一組仿真對比,如圖16和17所示,從波形來看,基本與之前的兩組仿真結果類似。

圖16.增加輔助源極電阻Rgee和電感Lgee參數舉例3

圖17.增加輔助源極電阻Rgee和電感Lgee前後的開通波形對比3

結合上述仿真波形可知,輔助源極電阻Rgee和電感Lgee對於開通時刻的寄生導通抑制效果一般,甚至Lgee電感控制不好,還會抬高overshoot電壓尖峰,增加並聯寄生導通的風險,同時對於Eon差異也是無所助益。

■ 採用帶米勒鉗位的驅動IC

為了顯出米勒鉗位的影響,我們對參數(Rg和Vgs電壓)進行了適當微調,同時選擇了英飛凌1EDI30I12MF(含米勒鉗位功能),設置驅動電壓Vgs=15V/0V,如下圖18和19所示:

圖18.米勒鉗位仿真的參數設置

圖19.米勒鉗位仿真的電路示意圖(上管部分)

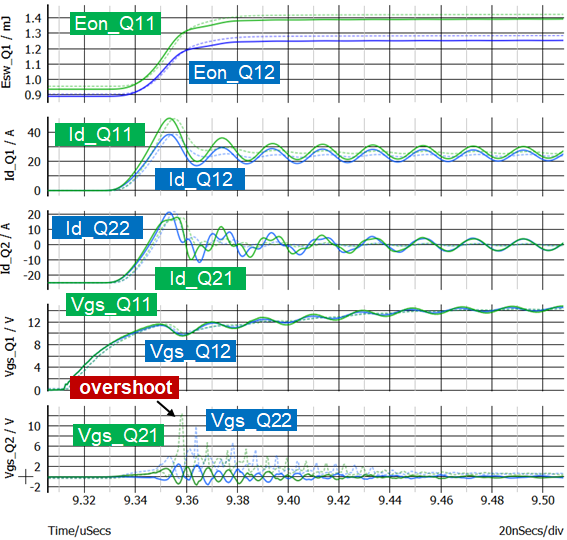

圖20.使能米勒鉗位前後的開通仿真波形

(米勒鉗位迴路電感Lx_clamp=2nH)

圖21.米勒迴路電感Lx_clamp從2nH到5nH前後的鉗位效果仿真對比

結合圖20和圖21中的波形可知,米勒鉗位能一定程度抑制並聯時的overshoot電壓尖峰,但是無法控制Vgs振盪,同時需要控制好米勒鉗位迴路中寄生電感大小,稍微大一些,也可能導致抑制效果減半,甚至變的更差。

■ 在門級增加共模電感

門級增加共模電感的相關參數設置和電路,如下圖22所示:驅動電壓Vgs=15V/0V

圖22.門級增加共模電感仿真參數舉例

圖23.門級增加共模電感仿真電路示意圖

圖24.增加門級共模電感前後仿真的開通波形

由圖24的波形所示,在增加門級共模電感(uH級)前後,虛線為無共模電感,實線為增加了共模電感,可以明顯看到門級共模電感不僅可以顯著改善overshoot的Vgs電壓尖峰和振盪,還能有效控制均流和縮小Eon的差異,效果非常好。

■ 在功率源極增加耦合電感

功率源極增加耦合電感的仿真相關參數設置和電路,如下圖所示:驅動電壓Vgs=15V/0V

圖25.功率源極增加耦合電感仿真參數舉例

圖26.功率源極增加耦合電感電路示意圖

圖27.功率源極增加耦合電感前後的仿真開通波形

由圖27所示,功率源極增加耦合電感(uH級別)後,無論是Vgs的overshoot的電壓尖峰還是並聯的電流差異,都得到了幾乎完美的解決!

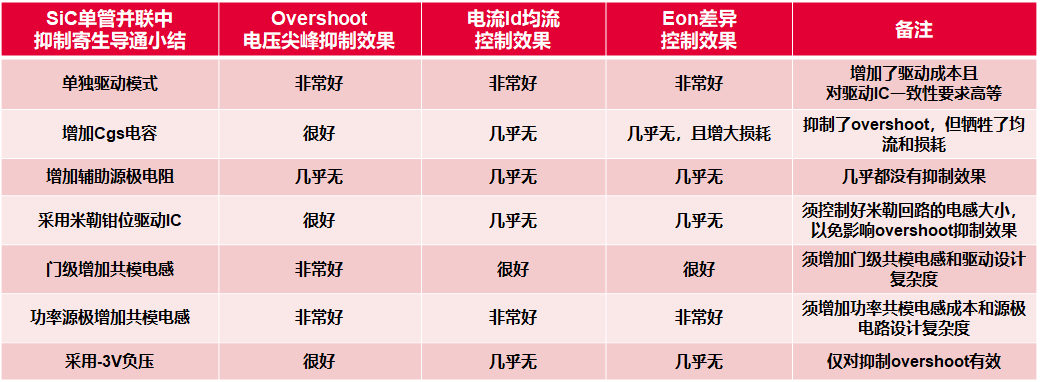

05 SiC單管並聯中的寄生導通問題小結

綜合上述的仿真分析,大致結論如下圖28所示:

圖28.SiC單管並聯中的寄生導通問題小結

原文鏈接:https://mp.weixin.qq.com/s/FDwwHl4zBhtsNC8itATwCQ