1、前言

功率MOSFET數據表通常列出了Rg、Ciss、Crss、Coss的典型、最小及最大值,同時也列出了閘極電荷Qgs、Qgd和Qg。通常也列出了阻性負載開關過程中的開關時間值:t(on)、trise、td(off)和tfall。元件參數Qgs、Qgd以及Qg分別和參數Ciss及Crss對應,一旦測量了元件的電容,就可能保證閘極電荷的參數值。閘極需要得到電荷,從而使閘極的電壓從0V增加到一定的電壓值,而且在電壓範圍內,其集成的電容具有非線性。

開關時間的測量由下面的因素來控制區:

t(on) – Rg、Ciss、Vth和gm,與元件及閘極的驅動器特性相關。

trise – Rg、Crss、Ciss、gm、Vth和Ls,與器件、閘極的驅動器特性、RL及電路設計的雜散電感相關。

td(off) – Rg、Ciss、Vth和gm,與元件及閘極的驅動器特性相關。

tfall – Rg、Crss、Ciss、gm、Vth和Ls,與元件、閘極的驅動器特性、RL及電路設計的雜散電感相關。

對於一個元件,在靜態測試中,一旦與Vth及gm一起測量Rg、Ciss和Crss,在固定的開關頻率下,可以保證元件的開關參數。封裝的雜散電感沒有測量,但由於它僅僅依賴於線的數目及佈置,嚴格的控制這個參數可以確保Ls很小的變化。因此測量Rg、Ciss、Crss和Coss就足以保證元件的閘極電荷和開關時間參數,包括Coss,這也含蓋了影響MOSFET開關損耗的所有元件參數。

2、動態參數的物理特性

2.1 閘極電阻功率MOSFET的閘極分佈電阻如圖1所示。對於一個給定設計的元件Rg由下列因素控制:

• 多晶矽薄膜電阻率、寬度及厚度控制;

• 閘極和多晶矽接觸電阻;

• 閘極金屬薄膜電阻率及寬度控制;

• 封裝的閘極電阻通常對Rg的影響非常小,變化也非常小,可以忽略。

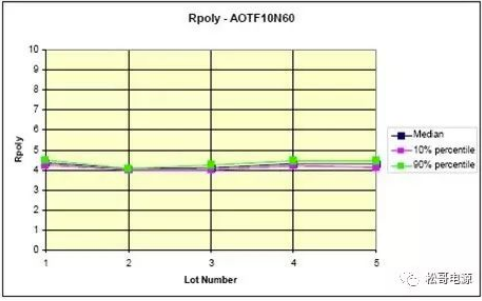

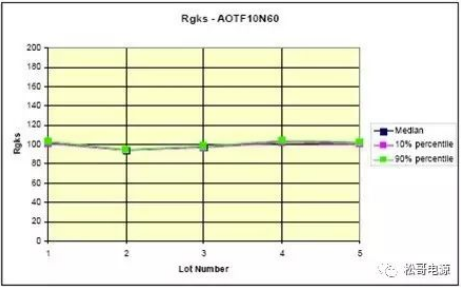

對於每一片的晶片,一條長的多晶矽電阻用來檢測多晶矽的線電阻率。在每一個生產的晶片上都有用於測試標準的工藝控制的檢測器PCM,在位於PCM的結構上進行四個管腳的Kelvin測試。典型的AOS產品的Rpoly性能如圖2所示。閘極金屬和多晶矽的連接電阻使用4管腳的Kelvin結構來檢測。 Rgks使用同樣的方式由PCM檢測,典型的AOS產品的Rgks性能如圖3所示。

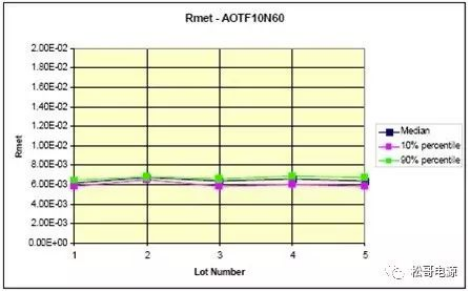

對於每一個生產的晶片,1000um長、10um寬的金屬總線的金屬薄膜電阻率使用位於標準的工藝控制的檢測器PCM上的結構來檢測。典型的AOS產品的Rmet性能如圖4所示,AOS產品的這些參數控制區非常好。

圖1:功率MOSFET閘極電阻的模型表示

藍色是圍繞器件閘極金屬總線,此條件下閘極焊盤位於角落處。閘極多晶矽為紅色,在晶元邊沿其連接到金屬總線上。圖中示出了沿著閘極多晶矽分佈的、和矽片的源極及汲極區域間的分佈的電容。

圖2:高壓平面MOSFET多晶矽電阻率檢測

圖3:高壓平面MOSFET閘極連接電阻檢測

圖4:高壓平面MOSFET的1000um長、10um寬金屬線電阻率檢測

圖2、圖3和圖4中,注意中間10th和90th百分線相互非常接近,表明對金屬電阻率、線寬和薄膜厚在工藝上都進行嚴格控制,此圖覆蓋一定的時間段。

現在考慮圖1中的MOSFET的Rg分佈特性。如果任何一個連接不是完全開放的或者一個小區域有高的Rpoly,這對於Rg或器件沒有或有很小的影響,因為閘極的信號將從多個並聯路徑中最近的路徑通過。

如果一個完整的器件Rpoly、Rmet或Rgks有問題,只有當一個晶片或晶片一部份同樣的參數有問題時,這種現象才會發生。通過在晶片的中間、邊沿放置PCM來檢測這種問題。

對於功率MOSFET低Rg設計,晶片級的Rg測量傳統上一直都認為相當困難,因此在最終測試地點,AOS通常在現場使用一個工裝對其做100%測試,然後使用專門的技術正確的測量器件的在晶片級的Rg;同時測量偏置的Ciss、Crss、Coss和靜態參數。這種技術應用晶片的200個位置取樣,以100%保證數據表中的Rg、Ciss、Crss和Coss參數。在最終的測試中,Rg 也100%的全檢測以保證閘極線很好的連接到閘極焊盤。進一步的,閘極電荷和開關時間參數也是100%保證。

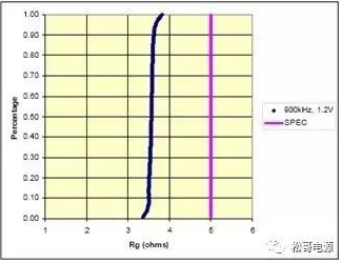

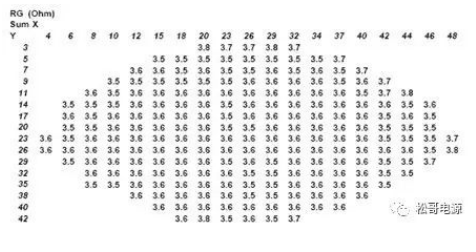

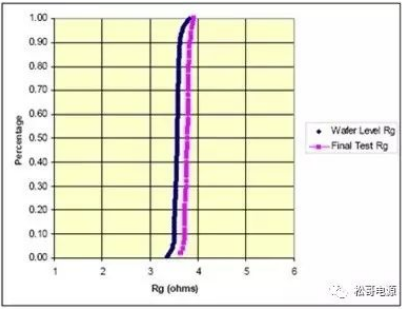

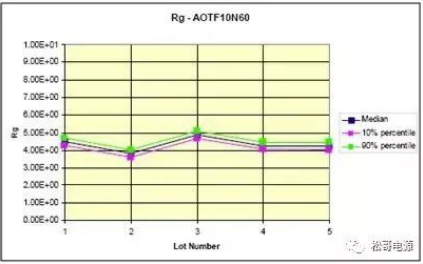

圖5示出了一個晶片的Rg的典型分佈,圖6示出了典型的晶片圖。大部分的Rg漂移儘管很小,但的確可以取得測試器的限制。圖7比較了同一個器件晶片探針和封裝後器件測試的結果。圖8示出了一個典型的產量高的AOS產品的批次和批次間隨時間變化控製圖。 Rg定義的保護帶中大部分應用於處理測試的能力,而不取決於真正的晶片工藝能力。

圖5:晶片的Rg典型分佈圖

圖6:典型的Rg分佈晶片圖

測試的行和列數量用粗體字標出,真正的值在晶片圖中示出,這些值有非常嚴格分佈。

圖7:晶片級和封裝級的Rg測量比較

結果表明可以得到非常好的一致性。

圖8:平面高壓MOSFET管AOTF10N60批次對批次的Rg的趨勢圖

注意到10th到90th百分點線,正好群集在中間線附近,大部分的變化真正的精確測試。

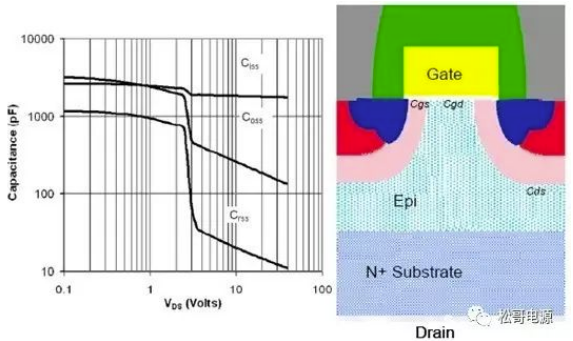

2.2 元件電容

就結構性的電容來說,規格數據表中的電容定義如下:

Ciss = Cgs + Cgd

Crss= Cgd

Coss = Cgd + Cds

平面MOSFET的Ciss由以下因素決定:

• 設計參數如多晶矽的寬度,晶胞斜度;

• 閘極氧化層厚度和一致性;

• 源極-體-Epi摻雜輪廓;

• 閘極多晶矽摻雜通常不是一個因素,由於其是退化的摻雜。

閘極的多晶矽和源極通道區域的電容決定了這些參數,其不具有偏向的敏感度,也非常容易重現。

高壓平面功率MOSFET的Crss由以下因素決定:

•設計參數如多晶矽的寬度,晶胞斜度;

•閘極氧化層厚度和一致性;

•體水平擴散,決定了JFET區域的寬度;

•體-Epi和JFET區域的摻雜輪廓;

•閘極多晶矽摻雜通常不是一個因素,由於其是退化的摻雜;

JFET區域的寬度,JFET輪廓和epi摻雜輪廓主導著這個參數。

高壓平面功率MOSFET的Coss以下因素決定:

• 所有影響Crss參數,由於它是Coss一部分;

• 電晶體二極管p-n結區域和摻雜輪廓。

圖9:高壓平面功率MOSFET電容

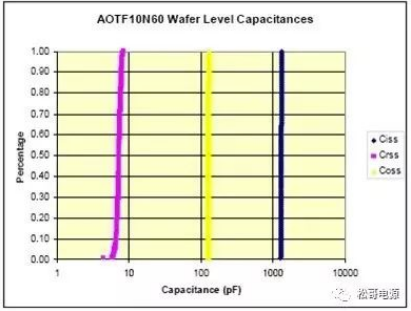

圖10展示了一個晶片上這些參數的典型分佈,圖11展示了同樣分由的晶片圖。

圖10:AOTF10N60晶片上200個測試位置點Ciss,Crss和Coss分佈

結果表明具有非常好的工藝控制,導致非常嚴格的參數分佈。

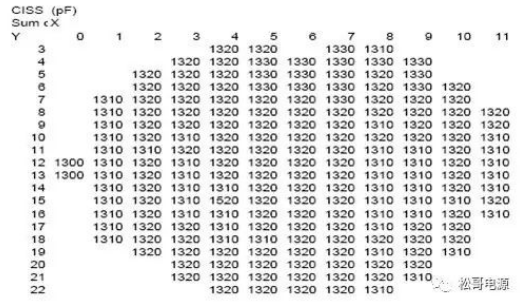

圖11:Ciss晶片圖數據展示晶片上Ciss具有嚴格參數分佈

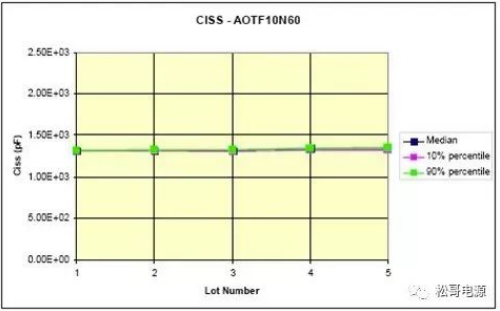

圖12:AOTF10N60的Ciss的批次對批次變化

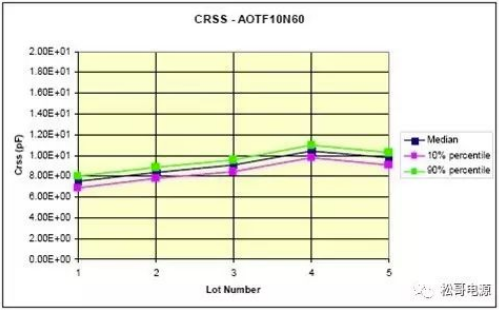

圖13:AOTF10N60的Crss的批次對批次變化

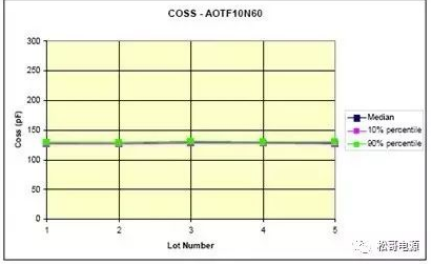

圖14:AOTF10N60的Coss的批次對批次變化

圖12、圖13和圖14示出了典型產品批次對批次的變化,注意到嚴格的10th到90th百分點線,正好群集在中間線附近。這表明的嚴格控制工藝控制。隨著靜態參數數據BVDSS變化,這些電容參數也會微小的變化,Rds和晶片圖模式有助於決定是否是引入的材料、或工藝控制因素起作用,從而影響AC參數,並提供一個強大的工具用於持續的改進。

評論